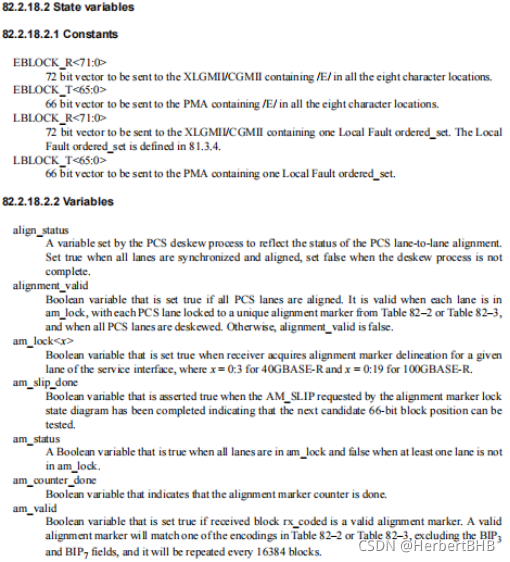

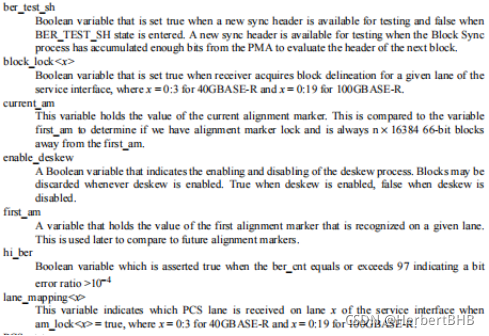

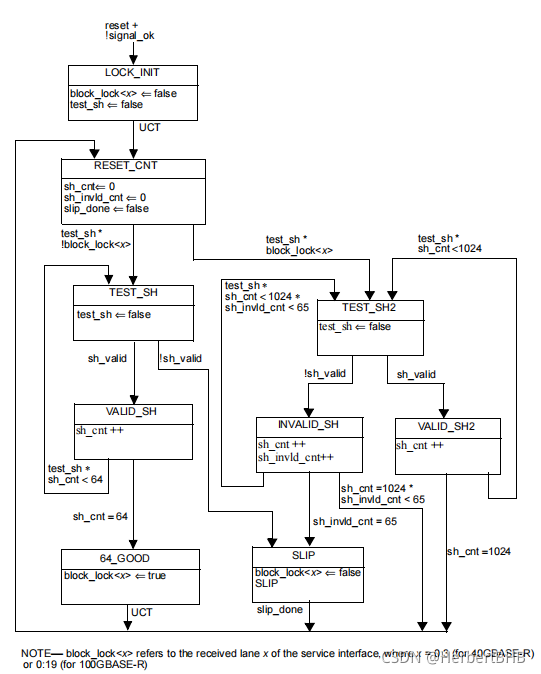

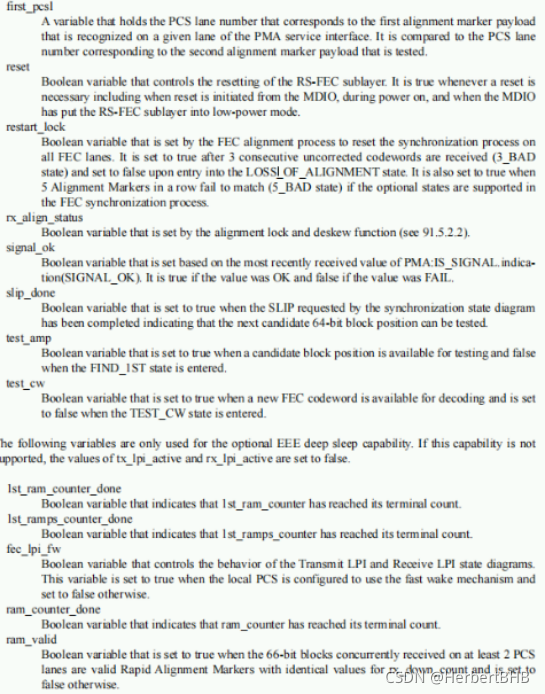

1.已经对状态机处理流程,跳转和边界处理进行汇报,理解其中处理步骤66b同步状态机

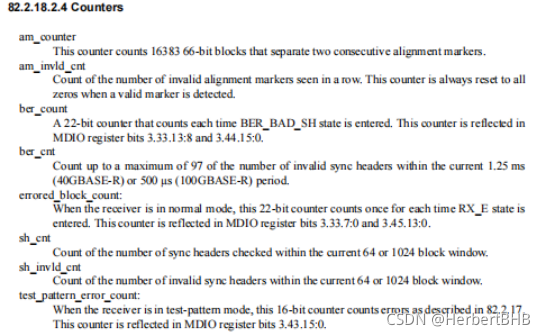

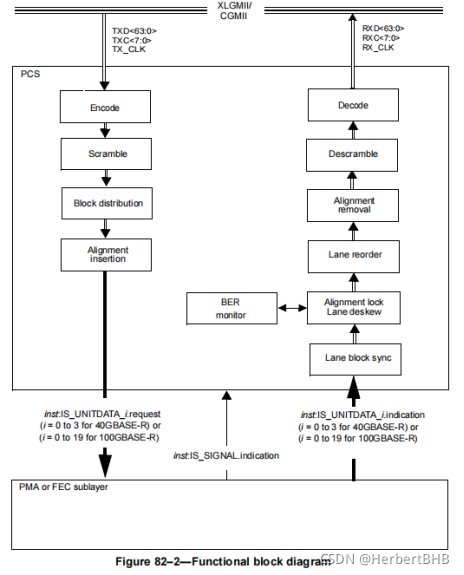

在正常模式下,从IS_UNITDATA_i.indication获得数据,完成同步。PCS按照数据信道顺序完成数据流拼接。使用同步头和66b输出可以从数据流中,得到锁定的66b数据块。

a:注意检验当同步头个数达到1024个时,恰好无效同步达到65个的过程,在验证设计时需要注意细节

b:注意在slip操作进行时需要确定划移数,尽量 做到全部检测

c: 在过程中test_sh什么时候被拉起来的条件,需要多少同步头才能实现

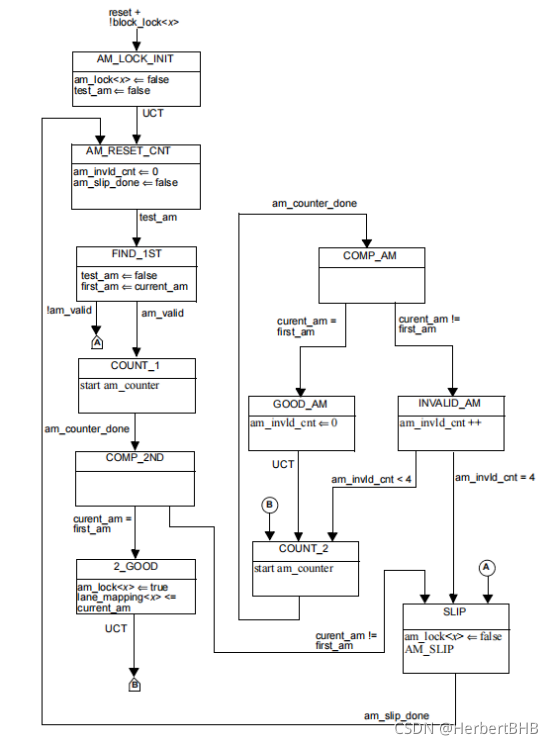

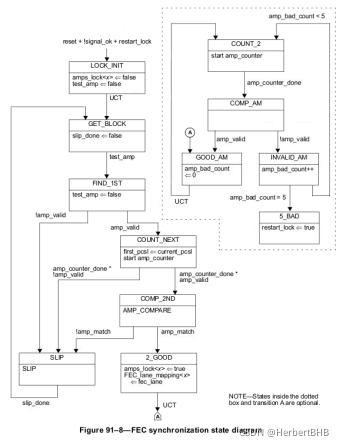

AM同步:

a: 如何配置am-counter,根据需要的数据长度配置周期数据量

b:边界条件当达到4个无效状态时,注意进行相关验证

c: 滑移操作的数量为66个bit数据

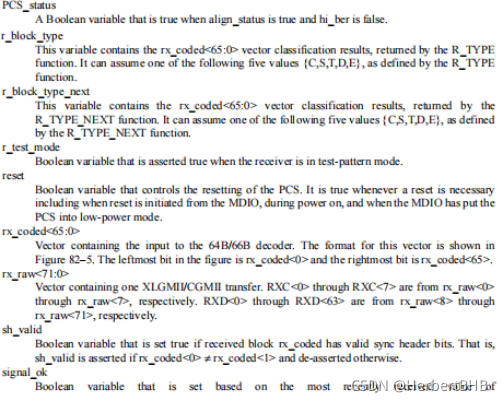

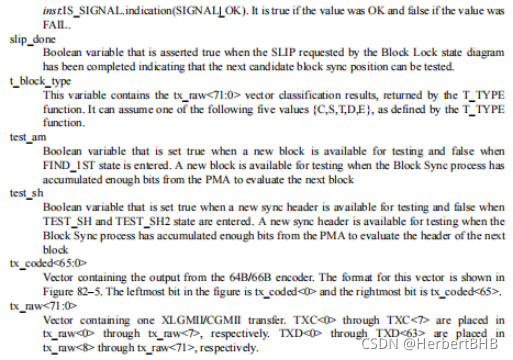

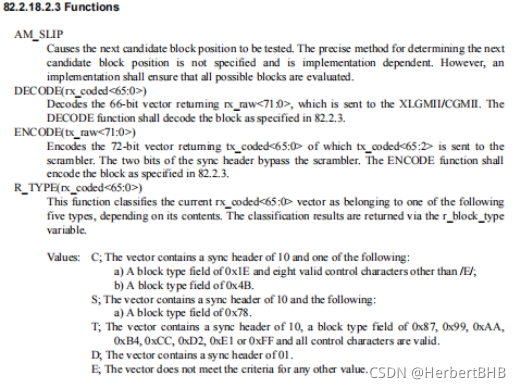

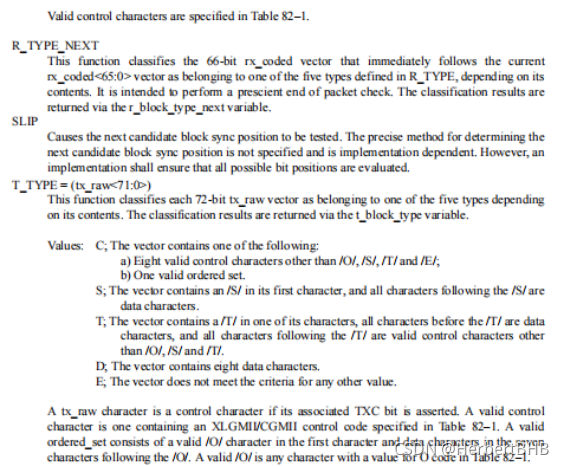

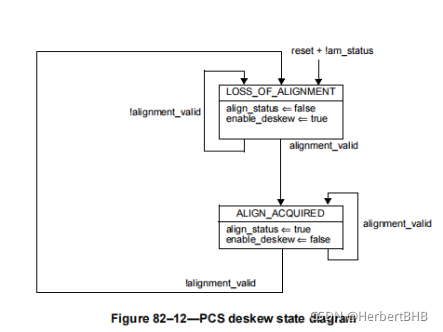

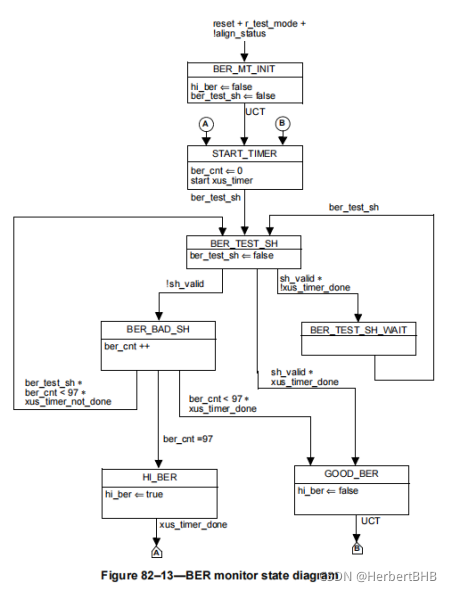

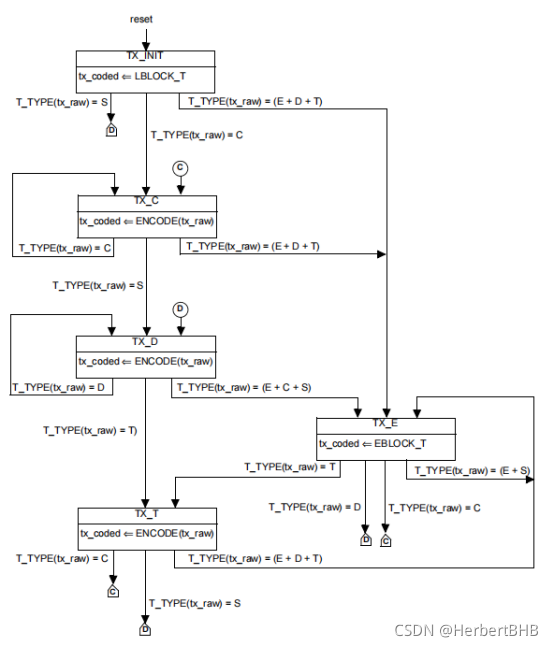

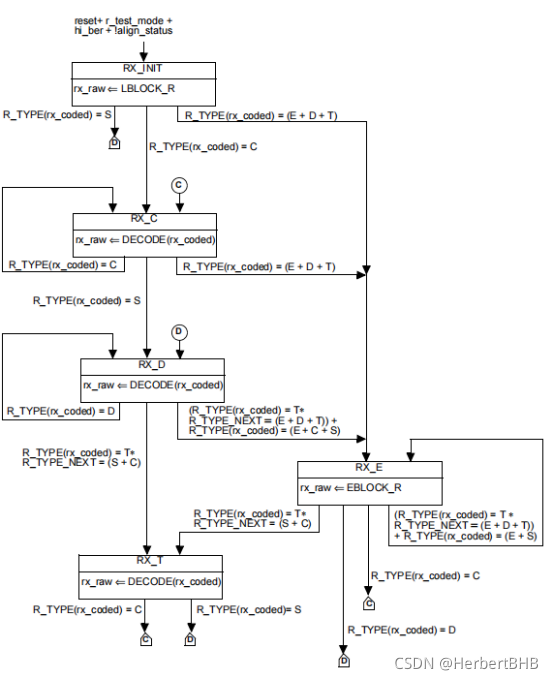

编解码状态:

注意各个状态转换条件以及在数据处理过程中数据位宽接收解码的66b,发送编码72b,特别注意各种编解码状态跳转条件而且在编解码过程中代码控制的具体操作,需要进一步注意

2.码型对应:

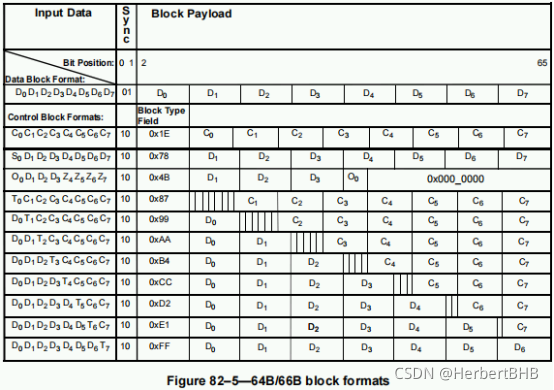

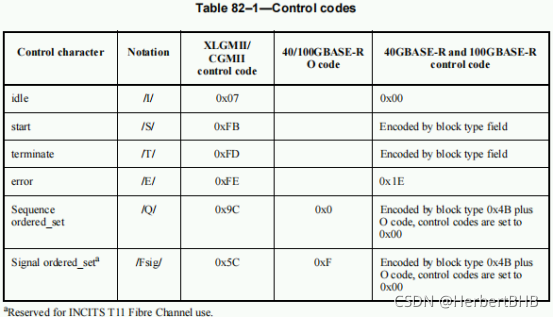

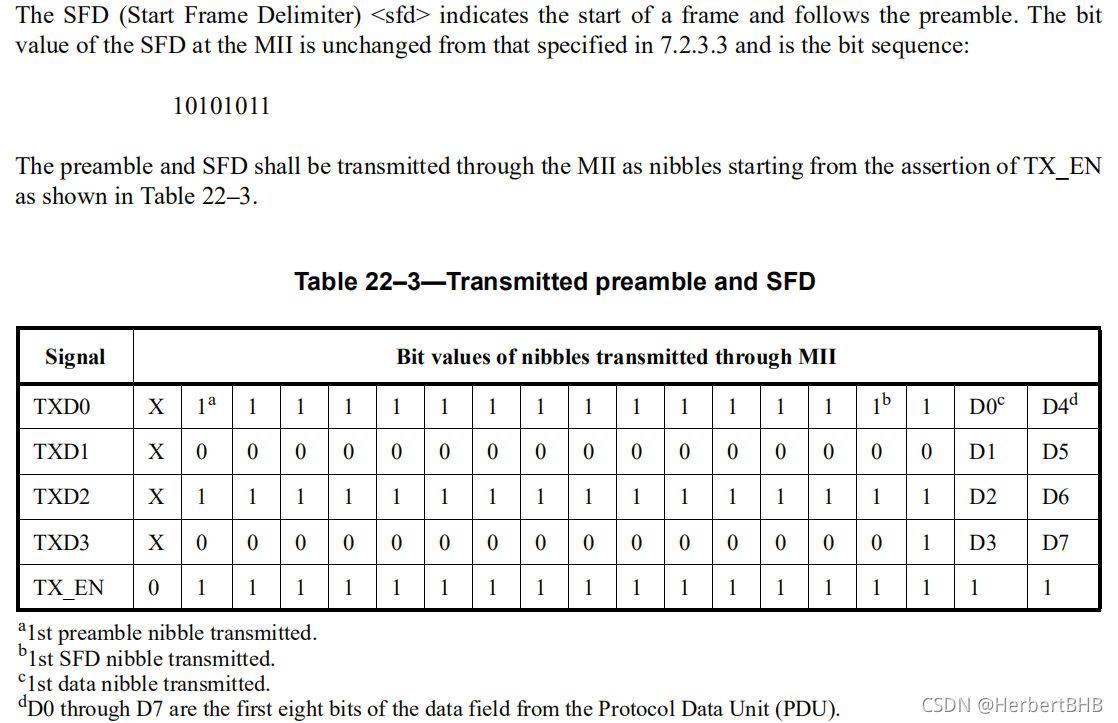

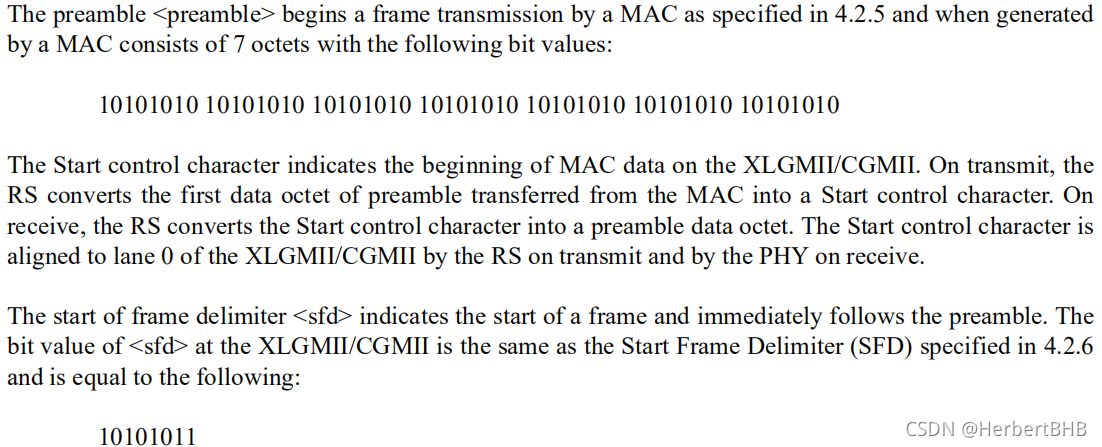

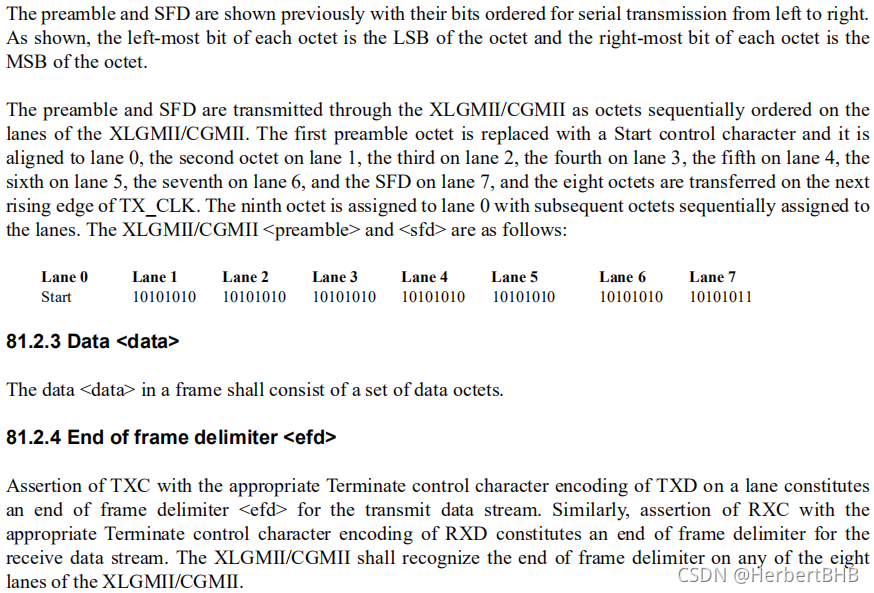

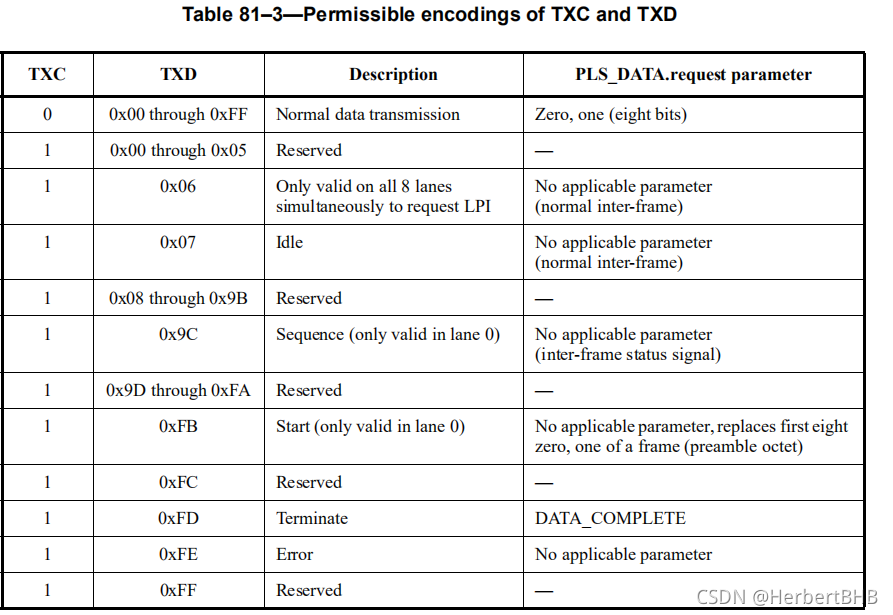

类似于10G编码方式,但编码控制有一些不同,如10时不存在33,而是存在4b,这是由于40g/100g中不存在s标志在第四数据出现,只支持在第一数据出现。且为了拓展控制和状态信息传递而新出现了O码(顺序集),它的组成格式是控制码加三个数据包,而后面在组合4个全零数据包。66bit数据包的前两位是同步头,10是控制包,01是数据包,两种包可以互相转化,余下的64位包含信息。加扰只对信息有效,同步头不进行加扰。同步头只是正常传输的一个标记位置,用来保证数据包同步。数据包含有8字,控制包中会有表示数据控制包类型的类型字段,START,Terminate或Ordered set通过字段标示,还有其余的控制字都被编码为7bit形式,控制码全是由8字符构成的。数据包构成格式如下表所示,通过XLGMII/CGMII传输的数据包分别配置控制字,数据包的控制字全为0,控制包的控制字全为1 。下图中的含Terminate格式中,小矩形代表一个值为0的bit位,在接收时过程中可以不用在意值的正确与否。数据类型字段中各值间的汉明距离是4,没有出现在下面表格中的其余控制字段,全是无效值,故不能进行发送,如若被接收到要按照error处理。

出现以下情况,数据包无效:

1. 同步头是00或11

2. 数据包类型字段不是数据格式列表中的类型

3. 控制包中控制码值不是控制码表中所示的值

4. XLGMII/CGMII传输的8字符数据格式与传入要求不相符

无效码示例:

a :同步头11或00

00 00011110 10001001 00101010 01001100 01001110 10001111 01001101 00001011 (sh:00)

b :包含非有效字段类型

10 00110011 10001001 00100010 01000100 01001110 10001111 00001111 00001111(0x33)

c :包含非有效控制码

10 00011110 01100100 00100000 00010010 01001110 11010110 11001100 10011010(1E数据类型控制码)

d :XLGMII/CGMII传输数据格式与传入要求不符

111111101 00000100 11111100 11110001 11000110 11011011 01100110 10011001

Idle: 当接收到XLGMII/CGMII中的idle信号(c为1,值为07)就发送idle信号(00),通过pcs控制增删idle来适应时钟频率。增删idle以8个为一组,一次增加或减少一组添加idle会紧随idle控制字或有序集后面,但不可在接收数据时添加。

Start:开始控制表明数据开始传输, 在XLGMII/CGMII中只有在第0信道才有效,其余全会报错

Terminate:标志着数据传输包的结束,由于数据包长度的不同,所以T会出现在任何位置,含有t的控制码中只有出现在不含有e或者t数据块后才是有效。

Ordered_set:增强了例如远端和近端故障连接问题的控制以及状态信息的发送能力。O码总是出现在XLGMII/CGMI的第一八位字中,40g和100g以太网中使用序列有序集,信号有序集被保留下来并以其他控制码开始。O码控制字标志着有序集的起始。为适应时钟速率pcs可能会对序列有序集进行删减,而且这种删减只能发生在接收阶段两个连续有序集之间,且只能删除其中两个有序集中的一个。只能插入idle字符来完成时钟数据补偿,而信号有序集不能实现。

Error:当编码或解码过程只要有error被检测到都可以产生E信号,当检测到无效数据块也会产生E。Pcs可以传递检测到的错误。

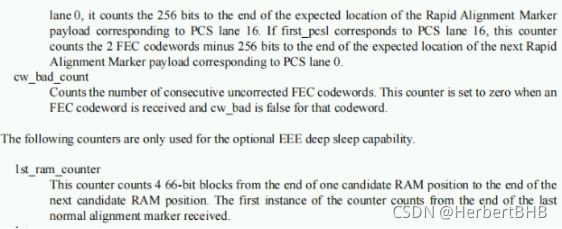

3.3状态机输出

仅仅通过最简单的方式输出了状态机的实现方式,通过开会交流发现实现方式存在问题,根据查找sv中状态机跳转实现方式,需要对伪代码进行优化

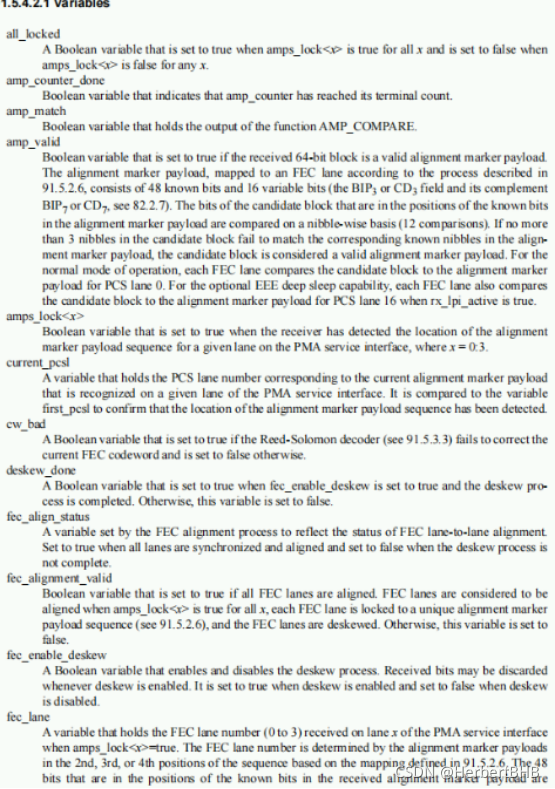

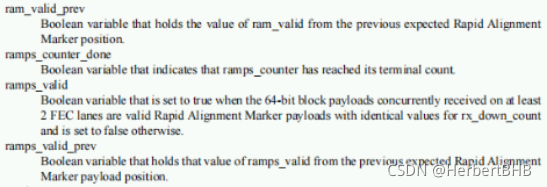

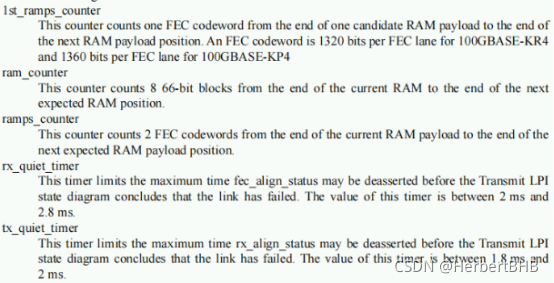

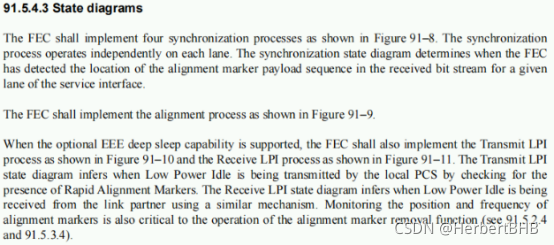

Rs_fec发送端从四个fec接收数据,并按照被的顺序拼接形成4条bit流数据,在每条bit流中使用同步头锁定66b数据并输出。同步数据过程即同步头锁定。

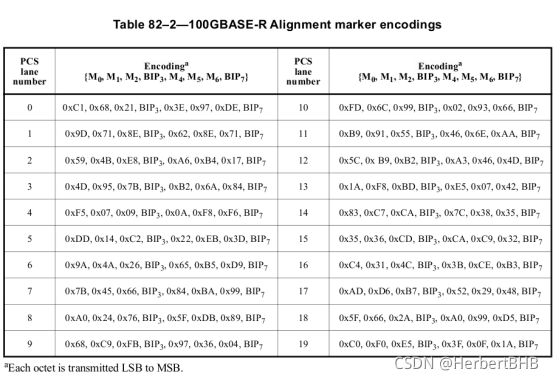

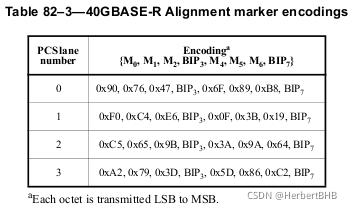

AM移除: 在所有的pcs信道都进行匹配并且去偏移后,多路pcs的信道会被重新排布一遍恢复原始数据流,其中的am会被移除。当am_lock为真时,即使am与期望值不匹配,am也会被移除,重复的am错误会导致pcs的信道中的am-lock被置为假,但在被置为假发生前,am移除的条件是一直满足的。作为am移除的一部分,bip3域会比对每条pcs信道计算得到的bip值。若满足45协议中的MDIO条件,当接受的bip3的值与计算所得的bip值不相等时,相应的bip错误计数器会按次加一。从pcs信道接收到的数据误码率会通过将bip3中的误码率扩充1351680倍得到。从local pcs接收到的数据经过rs_fec处理发送时不会进行误码校准。

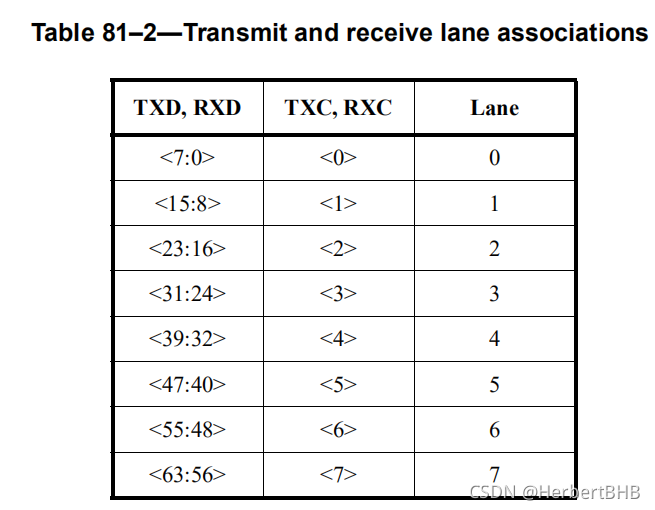

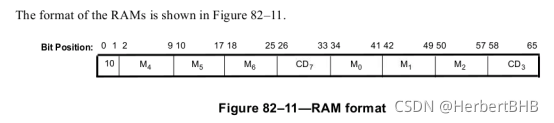

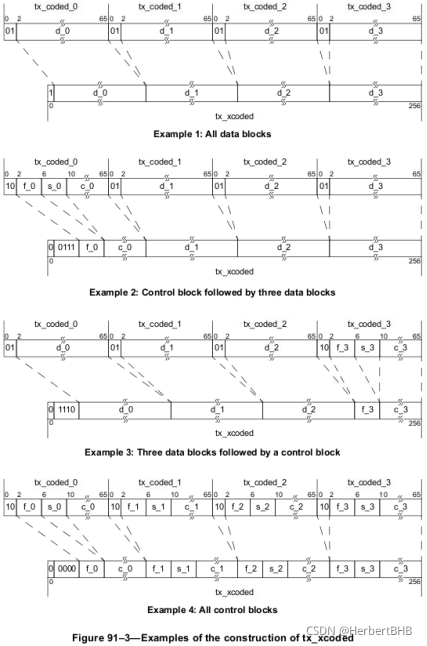

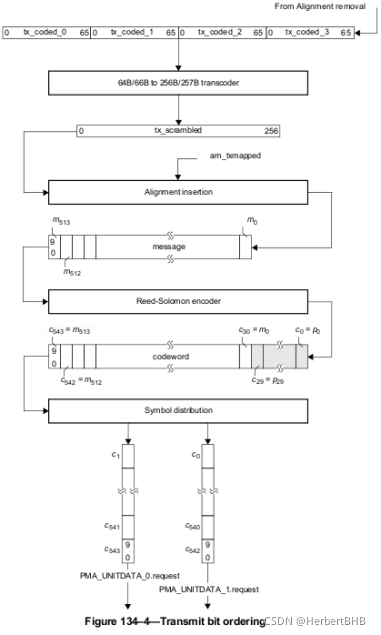

66bto257b:通过4个tx_code_j[65:0](j=0-3)的66b数据包进行拼接成为257b的tx_scrambled[256:0]。

- 若四个66b包全是01类型的数据包,tx_xcoded[256:0]构造成如下形式:tx_xcoded[0]=1,tx_xcoded[(64j+64):(64j+1)]=tx_coded_j[65:2] (j=0-3)

- 若四个66b全是有效包(包含控制包),tx_xcoded[256:0]构造成如下形式:tx_xcoded[0]=0,tx_xcoded[j+1]= tx_coded_j[1](j=0-3),令tx_payloads[(64j+63):64j]= tx_coded_j[65:2](j=0-3),令c等于四个接收到的66b控制包中最小的j值,省略tx_coded_c[9:6],即数据类型域的第二个半字节:构成tx_xcoded[(64c+8):5]= tx_payloads[(64c+3):0];tx_xcoded[(256:(64c+9)]= tx_payloads[255:(64c+8)]

- 若四个66b包含有无效同步头,tx_xcoded[256:0]构造成如下形式:tx_xcoded[0]=0,tx_xcoded[j+1]= 1(j=0-3);令tx_payloads[(64j+63):64j]= tx_coded_j[65:2](j=0-3),省略tx_coded_0中数据类型域的第二个半字节:tx_coded[8:5]=tx_payloads[3:0]; tx_coded[256:9]=tx_payloads[255:8]

最后加绕前5bit数据得到tx_scarambled[256:0]数据,将tx_scarambled[4:0]配为tx_xcoded[4:0]与tx_scarambled[12:8]的按位异或的值,tx_scarambled[256:5]=tx_xcoded[256:5],每个257block都是bit0作为第一个被传输的bit位。

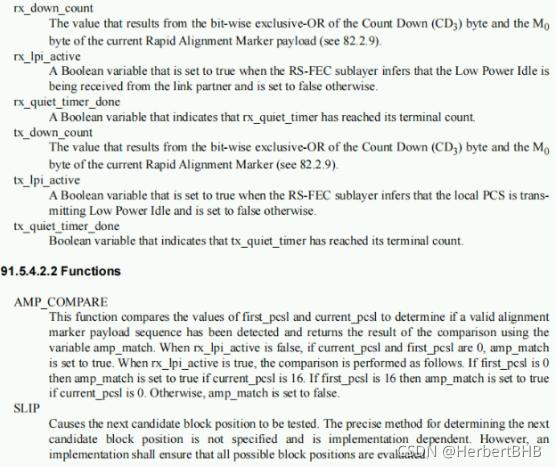

AM匹配及插入:AM在被移除后会被再次插入,匹配是为了完成标记分布并重新配置am头以便在fec信道中保持完整且序列正确。此操作保证了am的性能(如直流平衡,发送数据密度)并为接收端的同步提供了决定性的。Rs_fec接收匹配功能主要是通过从pma接口的给定信道接收数据来确定fec信道,以便完成fec信道去偏移并完成codeword的边界划分。

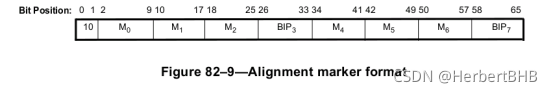

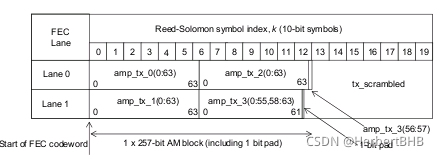

Am匹配主要处理从pcs处接收到的一组四个匹配并重排列的am头。都是bit0先被传输的四个pcs信道的am头成为amp_tx_x[65:0](x=0-3)。通过如下方式将四个am头整合为am_txmapped[256:0]:

首先: amp_tx_x[63:0]构成方式:当x<=1时,y=0,当x>1时, y=x, amp_tx_x[23:0]被配置为pcs的 y信道的M1,M2,M3,amp_tx_x[55:32]被配置为pcs 的y信道的M4,M5,M6,其余的amp_tx_x对应am_tx_x值。此过程使用4信道am编码替换从pcs处接受的am头中可能出错的修正字节。除此之外还会使用pcs信道0的修正字节替换pcs信道1的修正字节。对于变量字节(bip3和bip7)不作处理,这简化了rs_fec接收的同步过程,因为接收处理只需要搜寻每条fec信道中对应pcs信道0的修正的am头即可。

然后构建am_txpayloads[0,129:0]和am_txpayloads[1,125:0]:

am_txpayloads[0,63:0]: =amp_tx_0[63:0]

am_txpayloads[0,127:64]: =amp_tx_2[63:0]

am_txpayloads[0,129:128]: =amp_tx_3[57:56]

am_txpayloads[1,63:0]: =amp_tx_1[63:0]

am_txpayloads[1,119:64]: =amp_tx_3[55:0]

am_txpayloads[1,125:120]: =amp_tx_3[63:58]

此过程只是生成am_txmapped[256:0]的一个中间过程:给定的i=0-1,k=0-12,y=i+2k、Am_txmapped[255:0]构成如下,若y<25,am_txmapped[(10y+9):10y]=am_txpayloads[i,(10k+9):10k] am_txmapped[255:250] =am_txpayloads[1,125:120]

一个1bit的填补位被附加上来满足257位数据包,填补位会被交替配置为0或1。

am_txmapped[256:0]会在传输到rs编码器的每4*20480个66包被插入,对应了1024个rs codeword。在传输每1024个codeword时,匹配的am头,am_txmapped[256:0]会被作为第一个257信息位被传输。在am_txmapped后面别插入的第一个257bit需要对应的是从pcs信道0,1,2,3对应的am头。

Am匹配过程的结果会被用于rs编码和信道分配,上图中所示的am结构会出现在两条fec输出信道,并且在每1024个fec codeword的开头用于匹配,fec接收端使用这些信息来锁定两条fec信道,区分fec codeword边界。

Am匹配过程的附带作用就是从正常pcs接收的bip3和bip7会靠fec保护的链路传输。这些为是不会在66b/257b转换和rs编码过程被监控误码情况。但当这些数据位会在原始bit序列被被修复后会在rs编码和66b/257b转换过程再次被检测误码。

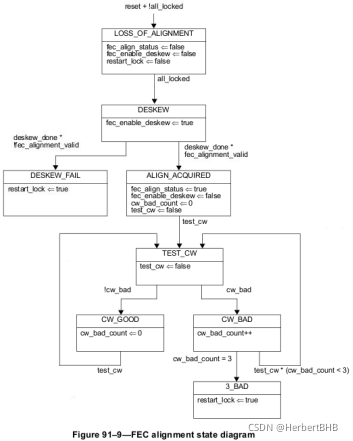

AM头同步:fec从两条pma信道接收数据后分别链接形成两条bit流,通过一下数据流程锁定数据流am。

两条fec信道锁定am头后,会经过下一流程去偏移,支持fec信道间最大偏移180ns,偏移速率4ns。

Fec信道从可以从原始被发送的不同的信道接口被接收。Fec接收端需通过不同信道对应的am序列重排序fec信道编号。所有的fec信道经过匹配,去偏移和重排后,fec信道数据会按照一定的顺序重组成fec编码数据完成被多路传输。

Rs解码:从codeword中提取信息位,必要时会纠错,舍弃等价符号位。解码器通过有目的地删除出66b同步头来向pcs指示错误信息。当解码器发现codeword中包含位纠正的error时,为保证该错误作为包含在codeword中的257b数据的第一数据(第一,第三,第五位等),经过66b/257转换后,第一个66b的同步头会被设为11。除此之外,同一个codeword中的对应的第二个257b数据的rx_code_0[1:0] 以及最后一个(第二十个)257b的rx_code_3[1:0]的同步头也需要被配置为11。rx_code_0[1:0] 配置为11会让pcs将其划为错误的66b数据,并将其内部数据解码全部是错误数据包,会导致pcs舍弃所有的帧结构的64字节,甚至会扩大部分或者全部地包含在codeword中的数据。

每1024个codeword的前257个bit数据是am_rxmaped数据,这个特定的数据里包含着该数据,意味着会被用于am锁定和去偏移,在传输过程中会被移除。

257b/66b转换:从一个257b 数据中提取4个66b数据包x_code_j[65:0](j=0-3)

首先解扰接收到的前5bit: tx_xcoded[4:0]的值为rx_scarambled[4:0]与rx_scarambled[12:8]的按位异或。令rx_xcoded[256:5]=rx_scarambled[256:5]

1.若rx_xcoded[0]=1:rx_coded_j[65:2]=rx_xcoded[(64j+64):(64j+1)] ,rx_coded_j[0]=0,

rx_coded_j[1]=1 (j=0-3)

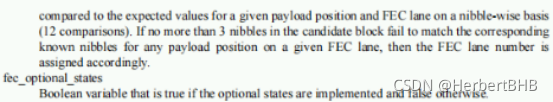

2.若rx_xcoded[0]=0,rx_xcoded[j+1]中含有为0变量(0-3):令c等于满足rx_xcoded[j+1]=0的最小的j值,即令rx_coded_c成为第一个66b控制包,rx_payloads[(64c+3):0]=rx_xcoded[(64c+8):5];

rx_payloads[(64c+7):(64c+4)]=0000(会被s_c替换);

rx_payloads[255:(64c+8)]=rx_xcoded[256:(64c+9)],令f_c[3:0]=rx_coded_c[5:2](即rx_coded_c的加扰block type的第一半字节),f_c[3:0]按照下方方式解扰到g[3:0]中,当c=0时,rx_coded_(c-1)对应前一个257b数据包的tx_coded_3。

![]()

Block type域的值对应数据类型是唯一的,不论如何传输。由于g[3:0]是block type的低4位,可以通过相应的表格补充高四位,假如无法匹配g[3:0],那么高四位则被补充为0000;若rx_xcoded[j+1]=0 那么rx_coded_j[0]=1,rx_coded_j[1]=0;若rx_xcoded[j+1]=1 那么rx_coded_j[0]=0,rx_coded_j[1]=1;若h[3:0]=0000,则rx_coded_c[1]=1

3.若rx_xcoded[0]=0,且rx_xcoded[j+1]全为1(0-3),则rx_coded_j[65:0]构成方式如下:

令c=0并且h[3:0]=0000,rx_payloads[(64c+3):0]=rx_xcoded[(64c+8):5];rx_payloads[(64c+7):

(64c+4)]=0000(会被s_c替换);rx_payloads[255:(64c+8)]=rx_xcoded[256:(64c+9)];rx_coded_j[65:2]=rx_payloads[(64j+63):(64j)](j=0-3) ;rx_coded_j[0]=0,rx_coded_j[1]=0(j=0,2), rx_coded_j[0]=1,rx_coded_j[1]=1(j=1,3);

4.若rx_xcoded[0]=0,加扰h[3:0]得到s_c[3:0],按照如下方式配置rx_coded_c

![]()

接收端Am匹配和插入:am匹配补偿从257数据区分成64位的pcs信道的am用于信道重排给定的i=(0-1),k=0-12,y=i+2k,Am_rxmapped[255:0]构成如下:

若y<25, am_rxpayloads[i,(10k+9):10k]=am_rxmapped[(10y+9):10y]

am_rxpayloads[1,125:120]=am_rxmapped[255:250]

构建am_txpayloads[0,129:0]和am_txpayloads[1,125:0]:

amp_rx_0[63:0]=am_rxpayloads[0,63:0]

amp_rx_1[63:0]=am_rxpayloads[1,63:0]

amp_rx_2[63:0]=am_rxpayloads[0,127:64]

amp_rx_3[55:0]=am_rxpayloads[1,119:64]

amp_rx_3[57:56]=am_rxpayloads[0,129:128]

amp_rx_3[63:58] =am_rxpayloads[1,125:120]

am_rx_x[63:0]构成方式:am_rx_x[0]=1,am_rx_x[1]=0;am_rx_x[25:2]被配置为pcs的 x信道的M1,M2,M3,am_rx_x[57:34]被配置为pcs 的x信道的M4,M5,M6,其余的am_rx_x对应amp_rx_x值。每1024个rs的编码会含有一个可以解析四个am头的向量。Am头会在四个66位块的每20479列之后四条pcs信道同时发送。Am头am_rx_0 - am_rx_3会被插入,分别紧随在rx_coded_0和rx_coded_3后面。

此过程使用4信道am编码替换从pcs处接受的am头中可能出错的修正字节。除此之外还会使用pcs信道0的修正字节替换pcs信道1的修正字节。对于变量字节(bip3和bip7)不作处理,这简化了rs_fec接收的同步过程,因为接收处理只需要搜寻每条fec信道中对应pcs信道0的修正的am头即可。

HEC校验

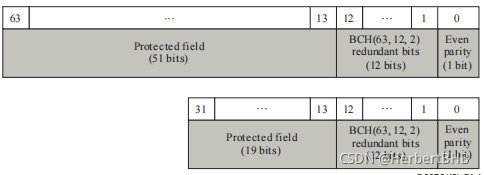

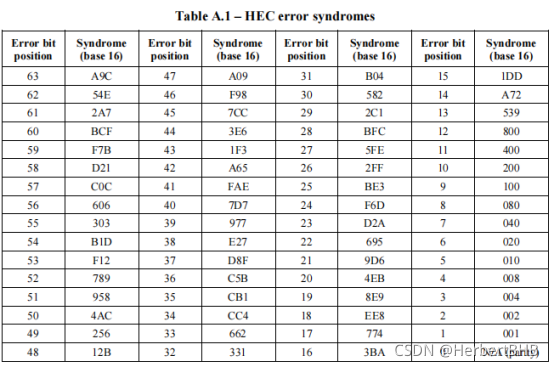

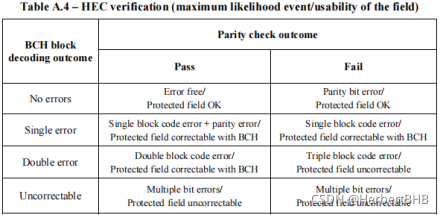

HEC具备双错纠正,三错探测能力,由两部分构成,第一部分为由生成多项式X12+X10+X8+X5+X4+X3+1生成的BCH码(63,12,2)。应用BCH码于受保护域(51bit) 以便将63bit结果被生成多项式切割。应用BCH可以让每个单错和双错具备唯一的12bit特征值,因此可以进行纠错,而数据存在三错时会产生匹配双错特征值或非法码型,不会产生匹配单错特征值。最后一点,应用BCH码会采用1bit的parity奇偶校验来监控并移除三错的情况。下表中表示了不同bit位置出错时对应的特征值,其中bit63位置代表51bit的被保护域的第一bit,1bit的位置表示hec的倒数第二位,0bit位置保留用于奇偶校验。对于更短的结构类型,bit31位置是19bit保护域的第一bit。

由于63种单错特征值,所以存在1953种双错特征值;12位的空间可以产生4097种特征值可能,故存在2079个值使用不到。这些不用的码字仅仅在三错甚至更高错的情况中会被按照当成非法值处理。

hec中的第二部分就是奇偶校验位。该校验位需要计算保护域和HEC值所有数的均值,可以表征header中错误是否为奇数。注意在BCH中不计算parity,但parity中需计算BCH。

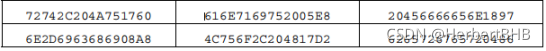

下表中列举了64位保护hec结构的部分有效格式示例。

下表中列举了32位hec保护结构的部分有效格式示例

下表中列举了32位hec保护结构的部分有效格式示例。

在接受处通过计算特征值以及parity解码hec。下表中列出了hec校验的结果:

2392

2392

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?