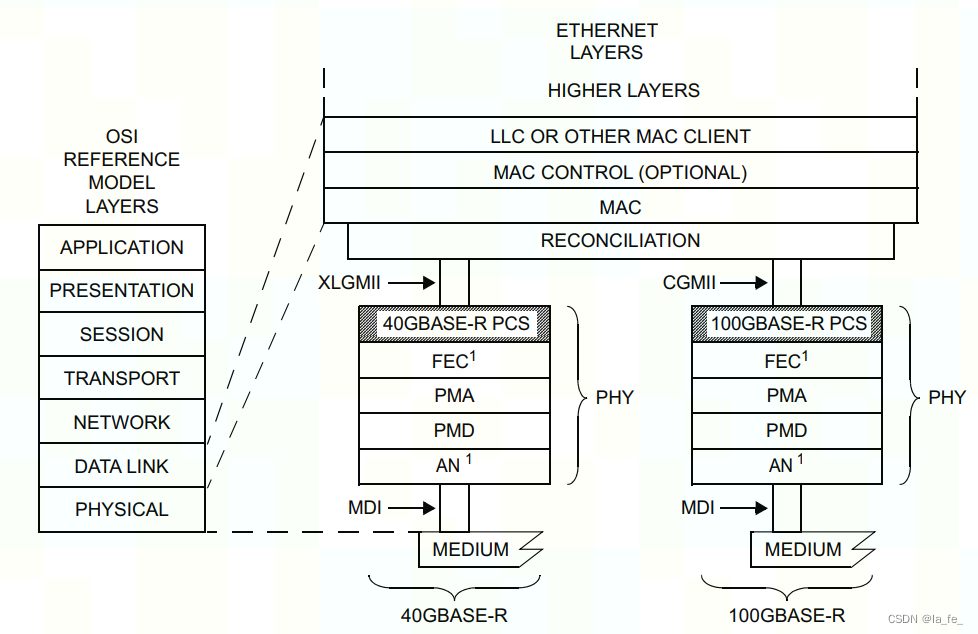

Clause82:Physical Coding Sublayer (PCS) for 64B/66B, type 40GBASE-R and 100GBASE-R

1. PCS 介绍

1.1 概述

PCS( Physical Coding Sublayer)属于物理层,通过 MII 接口与 MAC-RS 层进行连接,主要功能:

(1)将 MII 接口的数据编码为 66B Block,反之,将 66B Block 解码为 MII 接口数据;

(2)对数据进行加扰和解扰;

(3)通过插入或删除对齐字补偿 PMA 和 MII之间的速率差。

XLGMII 传输速率为 40Gbps,经过PCS 64B/66B编码后传输速率变为 40Gbps * (66/64) = 41.25Gbps

CGMII 传输速率为 100Gbps,经过PCS 64B/66B编码后传输速率变为 100Gbps * (66/64) = 103.125Gbps

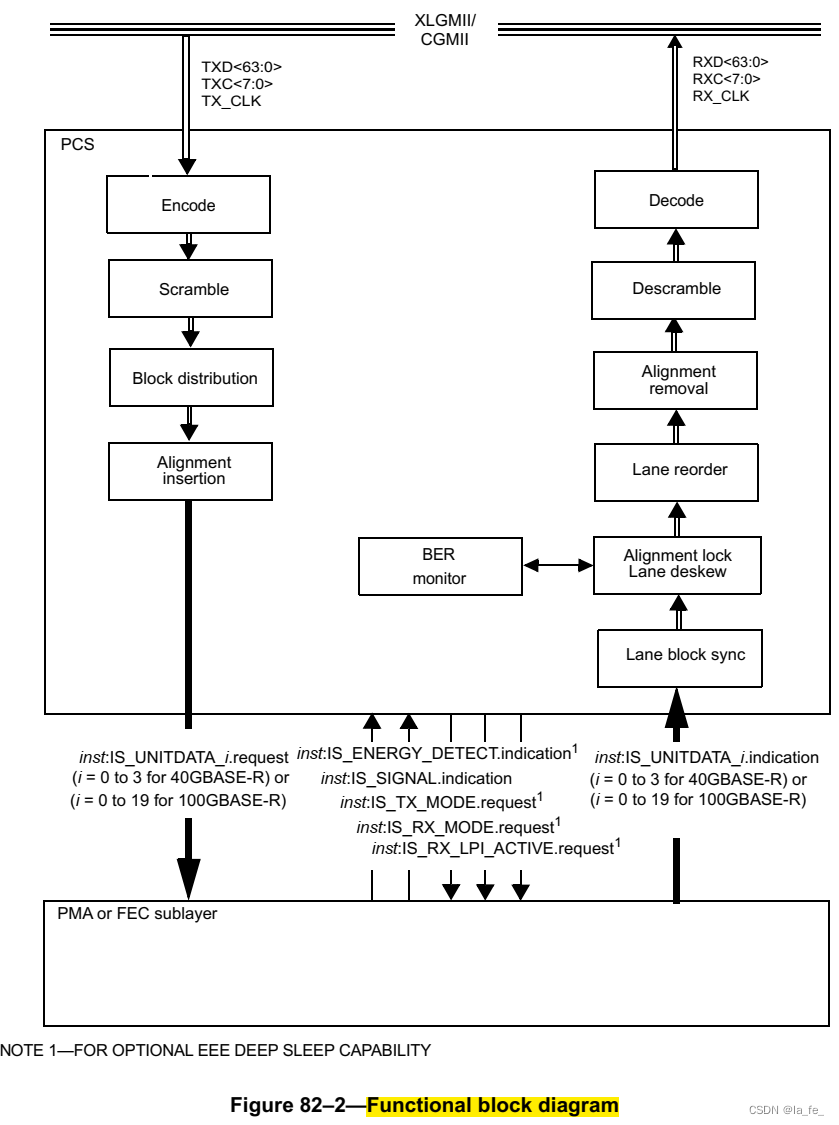

1.2 功能框图

为了支持物理层的多条lane,PCS增加了Block分发机制,并在分配Block时周期性地插入对齐标志AM。40G/100G Base_R PCS模块图如下所示,和10G Base_R PCS相比,增加了多lane的功能模块(Block distribution,lane reorder,lane deskew)和对齐标记相关的功能模块(alignment insertion,alignment lock,alignment removal)。

40G/100G Base_R在继承之前以太网技术的物理层结构的同时,增加了可选的前向纠错FEC子层、自协商AN子层,PCS编码和扰码处理也进行了调整。具体工作流程如下图所示:

上下层间接口:

-

40G/100G PCS 与上层 RS 分别通过 XLGMII/CGMII 接口进行数据传输,接收数据为 64bit,控制字为 8bit;

-

40G/100G PCS 分别使用 4 条 lane 和 20 条 lane 与 FEC/PMA 进行数据传输;

工作流解读:

(1)发送方向:

PCS 传输过程根据 XLGMII/CGMII 上的 TXD <63:0> 和 TXC <7:0> 信号不断编码生成 66B Block——>

编码后进行扰码并按逐序分发到独立的 PCS lane 上 ——>

周期性地(每16383 个 Block插入一次)插入 AM ——>

数据通过 inst:IS_UNITDATA_i.request 发送到层间服务接口(inst 可以是 FEC 或 PMA);

(2)接收方法:

PCS 同步流程监控 inst:IS_SIGNAL.indication(SIGNAL_OK) 的信号,当 SIGNAL_OK = OK 时,PCS 通过 inst:IS_UNITDATA_i.indication 接收数据 ——>

在每条 lane 上根据 2-bit 的同步头获取 Block Lock ——>

Block Lock 后,根据可用的 AM 来获取 AM Lock ——>

当所有 lane AM Lock 后,对 PCS 通道进行重排序和 deskew ——>

所有通道对齐后,删除 AM 并将数据组成单一数据流,设置 align_status = true 表示 PCS 已经对齐。同时,BER 监控器监控信号质量,当误码率高时,设置 hi_ber = true ——>

当 align_status = tru

本文详细介绍了802.3标准中的PCS(Physical Coding Sublayer)子层,主要负责64B/66B编码、加扰、块分发、对齐标志插入和移除等功能。在发送方向,PCS将数据编码为66B Block并进行加扰,接收方向则涉及块同步、对齐标志锁定和去抖动等过程。PCS在40GBASE-R和100GBASE-R中起到关键作用,通过多lane处理实现高速数据传输。

本文详细介绍了802.3标准中的PCS(Physical Coding Sublayer)子层,主要负责64B/66B编码、加扰、块分发、对齐标志插入和移除等功能。在发送方向,PCS将数据编码为66B Block并进行加扰,接收方向则涉及块同步、对齐标志锁定和去抖动等过程。PCS在40GBASE-R和100GBASE-R中起到关键作用,通过多lane处理实现高速数据传输。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

6442

6442

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?