VIP Introduction

上一篇对layering sequence的UVM结构进行了介绍(🔗UVM layering sequence for layered protocol),本篇分析商业VIP(Verification Intellectual Property)是如何采用layering sequence构建agent对layered USB protocol进行建模;

VIP提供高度可配置的标准协议Model,用于快速集成搭建验证平台对DUT测试;常用的VIP厂商如Synopsys,Cadence,Avery等;

本篇以Synopsys的VC(Verification Continuum)产品:SVT(SystemVerilog Verification Technology) USB VIP为例。(本篇仅从layering sequence角度粗略介绍svt_usb,不涉及usb协议和VIP具体使用问题;商业级VIP仅从使用角度理解即可,其整体功能的实现较复杂)

svt_usb_agent

svt_usb_agent 的组成结构和USB协议栈一样,分为三层结构,Physical, Link, 和 Protocol 层。

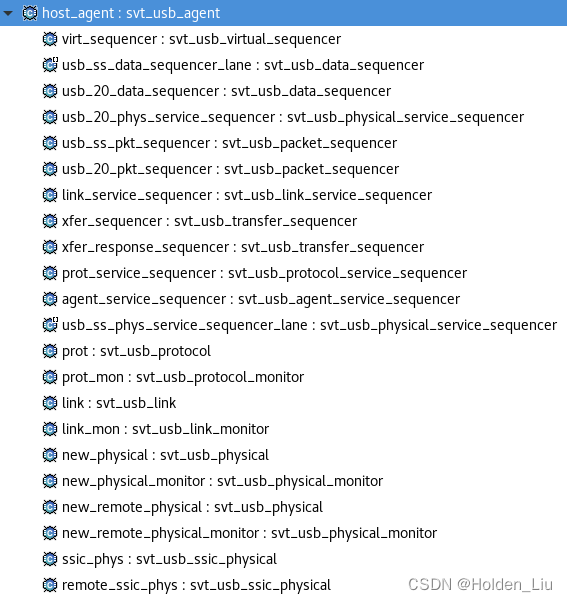

svt_usb_agent的UVM Hierarchy例化结构如下(DVT生成):

svt_usb_agent包含svt_usb_physical/link/protocol,分别模拟USB中的Physical, Link, 和 Protocol 层;各种sequencer负责不同的transaction发送;monitor负责transaction的收集;remote component用于测试DUT MAC接口;图中没有显示driver,因为USB VIP中的driver并没有继承uvm_component,而是单独创建的class,具体后面讨论。

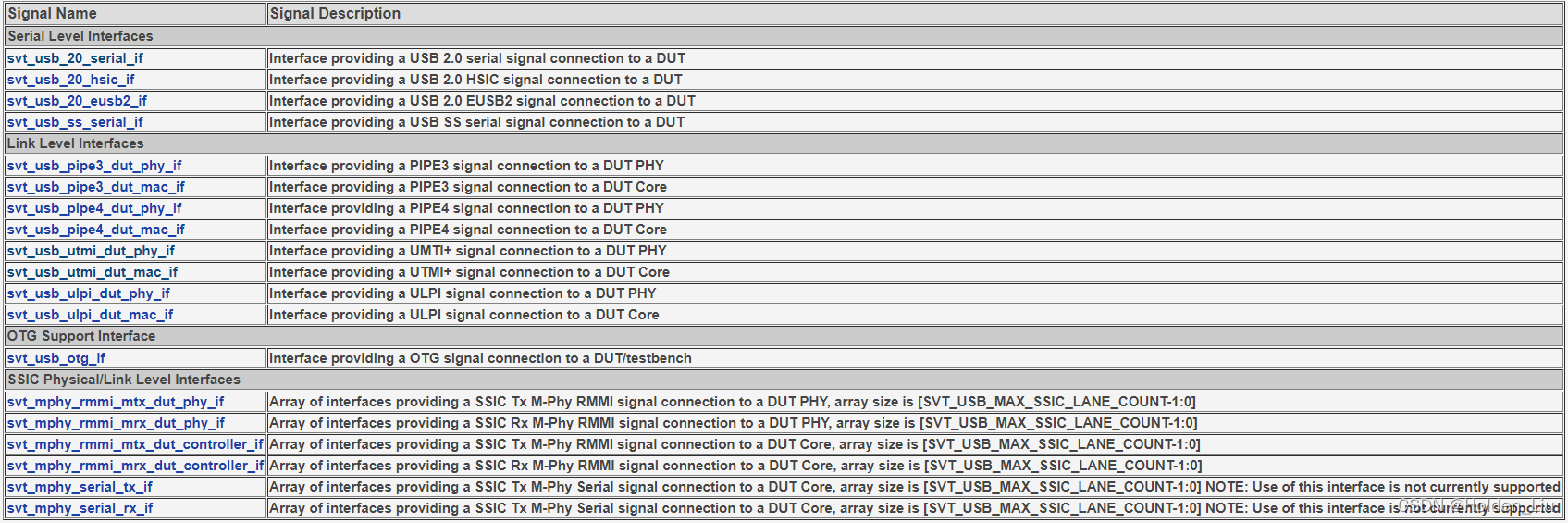

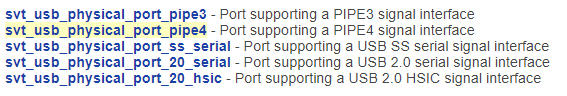

USB的应用接口众多,根据DUT接口的不同,可以进行不同的配置:

USB协议分为2.0(LS,FS,HS)和3.x(SS:super-speed),其Phy的接口不同,但都是串行差分对cable bus,svt_usb_20_X为usb2.0接口,svt_usb_ss_X为usb3.x接口;对于eUSB2,接口为svt_usb_20_eusb2,可以通过repeater连接常规USB2.0; 对于Inter-Chip PCB互联bus,2.0为HSIC,3.x为SSIC(分为USB PHY和 MIPI M-PHY两种);对于DUT是MAC的接口,USB2.0分为UTMI和ULPI;USB3.x为PIPEx;对于使用MPHY的USB3.x,MAC接口为RMMI;

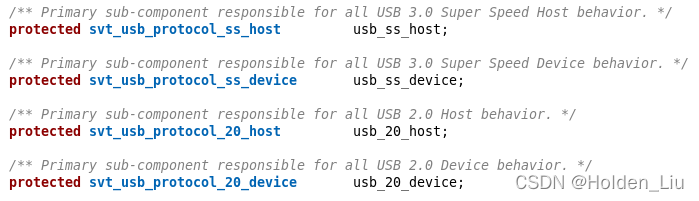

svt_usb_protocol

svt_usb_protocol负责USB协议层功能,包含了USB host、USB device、USB 2.0 protocol、USB 3.0 Super Speed protocol,彼此之间相互独立. 这些Function Block负责transaction的schedule和process.

当作为HOST时 (VIP作为Device不在扩展介绍):

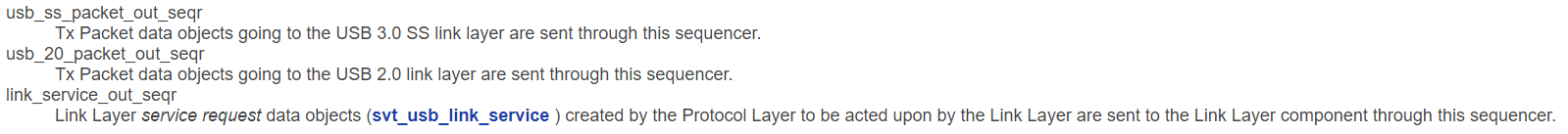

TX方向,svt_usb_ptotocol从sequencer接收到svt_usb_transfer,分解为svt_usb_transaction,再转化为svt_usb_packet; 通过layering_sequence将TX packets发送给svt_usb_link;

RX方向,从svt_usb_link的port端口接收RX packets,整合处理为svt_usb_transfer;

除了数据传输功能,USB协议规定的其他内容,如状态控制相关,从suspended进入assume状态,属于service范畴,由svt_usb_protocol_service负责.

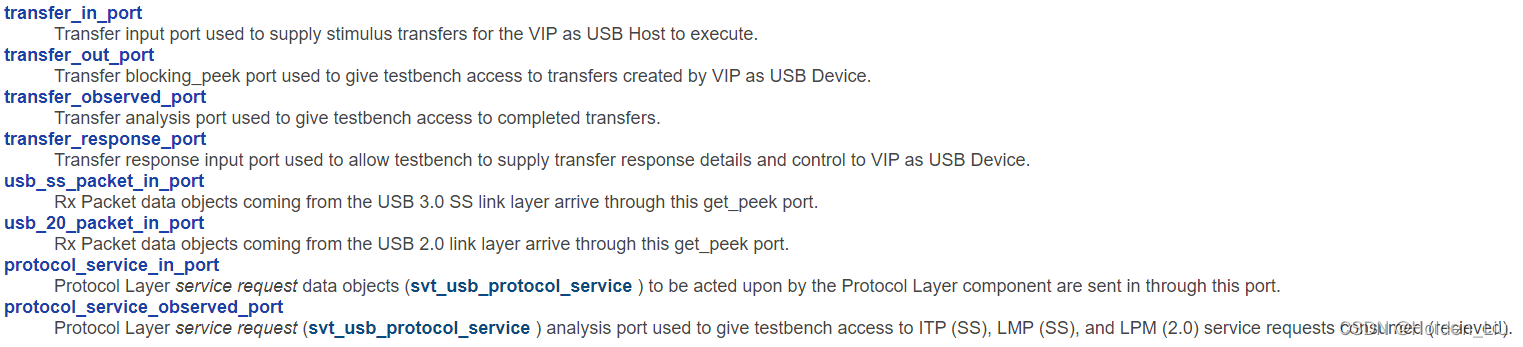

svt_usb_protocol提供了5种方式和testbench交互:

-

各种UVM port

如transfer_observed_port可以连接scoreboard做check;

-

UVM Sequencers、

用户可以直接通过sequence产生svt_uvm_packet,使用svt_usb_protocol内建的sequencer发送给link层;而通常使用方式是构建sequence产生svt_uvm_transfer,由svt_usb_protocol做进一步处理.

-

Callbacks

svt_usb中预留了大量callback,用户可以继承svt_usb_protocol_callback进行重写. -

Notifications

svt_usb中提供众多notification,可以很容易了解到内部处于何种状态;

notifications其实就是uvm_event,提供了众多API,除了wait_trigger()做事件同步,get_trigger_data()也可以获取data. -

Factories

svt_usb_protocol会根据override后的类型创建实例.

svt_usb_link

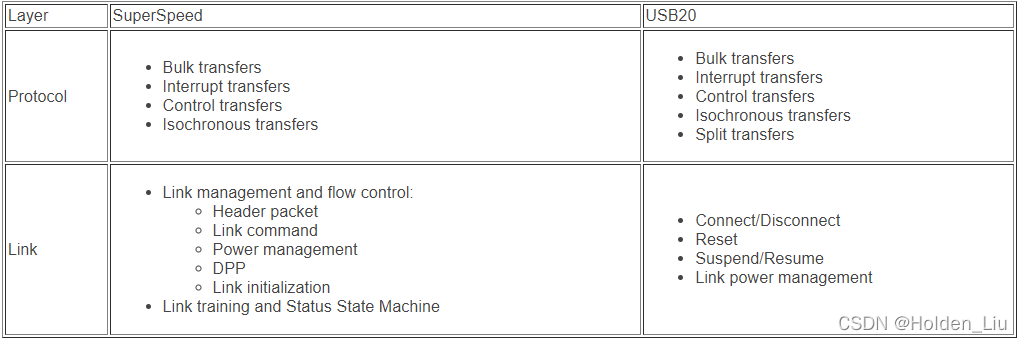

svt_usb_protocol负责USB链路层功能,包含了usb_ss_link和usb_20_link,彼此之间相互独立.

usb_ss_link包含了Super-Speed Link Transmitter/Receiver、Super-Speed LTSSM、Link Command Manager;

usb_20_link包含了2.0 Device-A State Machine(模拟Downstream Facing Ports FSM)、2.0 Device-B State Machine(模拟Upstream Facing Port FSM);

具体功能见下表:

当作为HOST时 :

TX方向,svt_usb_link从sequencer接收到svt_usb_packet,转化为svt_usb_data; 通过layering_sequence将TX data发送给svt_usb_physical;

RX方向,从svt_usb_physical的port端口接收RX data,整合处理为svt_usb_packet;

svt_usb_link和svt_usb_protocol一样,也提供了5种方式和testbench交互;

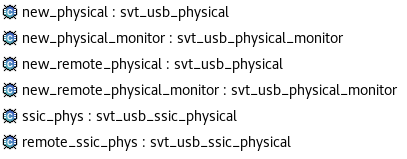

svt_usb_physical

svt_usb_physical负责USB物理层功能

new_physical负责2.0,3.X USB Phy功能;

new_remote_physical负责和DUT MAC连接(当DUT不是serial接口时,VIP的 local PHY和 remote PHY内部通过 TLM 连接,然后再和 DUT Link interface相连 );

ssic_phs负责USB SSIC,包含mphy_svt的组件;

SVT USB Physical component的功能分为三类:

svt_usb_data的处理,如3.x的8b10b编码,2.0的NRZI编码;- Event Modeling,如插拔状态的监测

- Signal Interfaces的驱动和采样

当作为HOST时 :

TX方向,svt_usb_physical从sequencer接收到svt_usb_data,若是serial interface,则通过 svt_usb_physical_port驱动symbol到signal interface;若是link interface,则将svt_usb_data发送给remote physical;

RX方向,svt_usb_physical从svt_usb_physical_port或者remote physical接收svt_usb_data,再通过port发送给svt_usb_link;

svt_usb_physical不同于svt_usb_protocol,提供了4种方式和testbench交互,不包含sequencer,因为svt_usb_physical已处于最底层,svt_usb_packet为USB的最小有效单元,用户不会直接构造svt_usb_data的transaction.

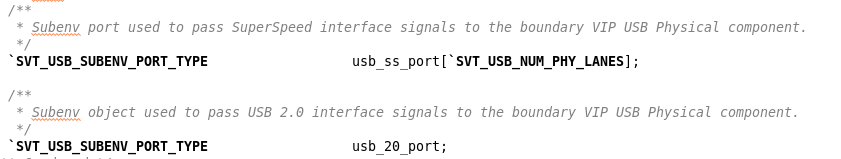

这里重点介绍下svt_usb_physical_port,这个port实现的是driver的功能,但是并没有继承uvm_driver,virtual interface也不是通过config_db::get方式获取;不同接口对应不同类型的port:

svt_usb_agent中分为2.0,3.x两种(3.x根据lane的数量确定):

以USB2.0为例:

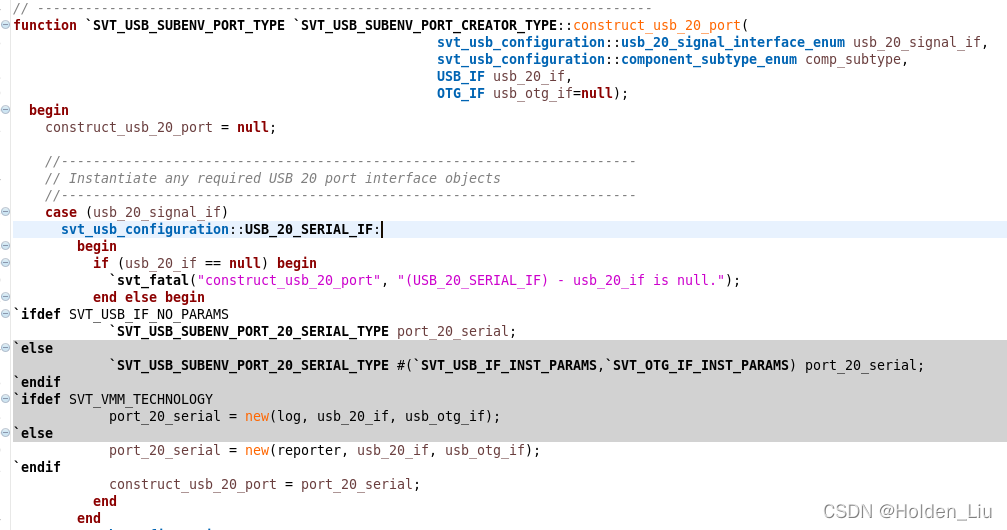

TOP层例化的interface为svt_usb_if类型,其中包含各子类interface;svt_uvm_agent config_db::get获得virtual interface后,会根据cfg中指定的signal interface type选择创建某一类port;并将interface指向port中的virtual interface;

这些操作都封装到了usb_20_if_obj_creator中的construct_usb_20_port;

接着调用set_usb_20_if_obj为svt_usb_agent中的句柄usb_20_port赋实例;

在创建svt_usb_physical时,调用set_usb_20_port为physical中的port句柄赋实例;

至此,当svt_usb_physcal中收到svt_usb_data,通过tx_consumer里调用port的main()函数对signal interface驱动;(具体实现较复杂,这里仅作简单描述)

layering sequence

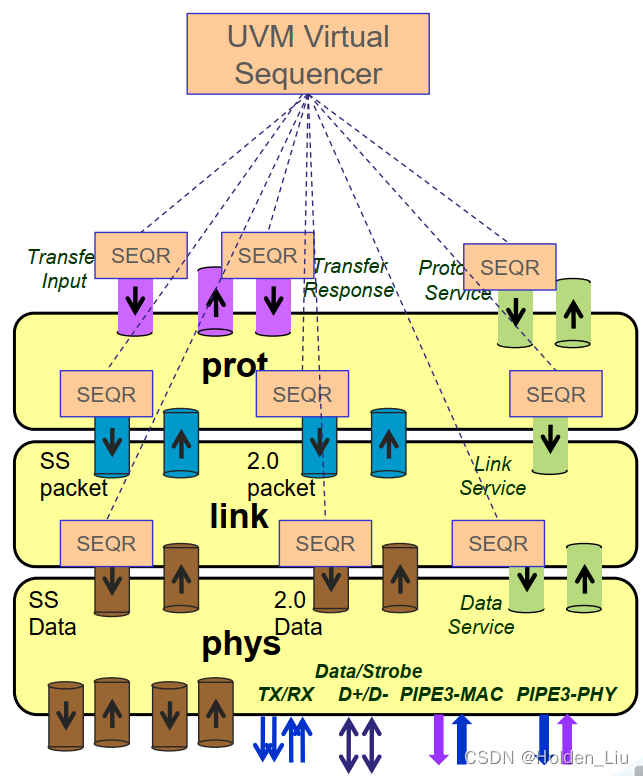

svt_usb_agent的传输结构如下:

以USB2.0 HOST TX方向为例:

-

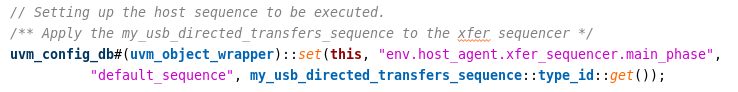

testcase中创建sequence,挂载到

xfer_sequencer;

-

sequence中产生

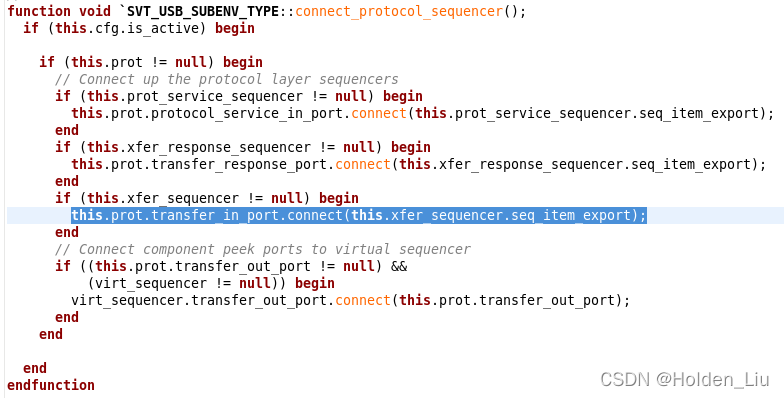

svt_usb_transaction类型的tr,发送给svt_usb_protocol中的transfer_in_port;TLM连接通过调用svt_usb_agent中的connect_protocol_sequencer在connect_phase中完成:

-

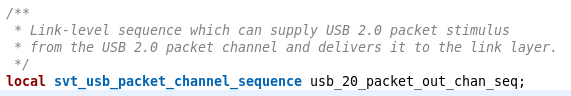

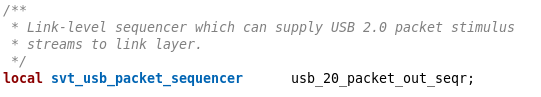

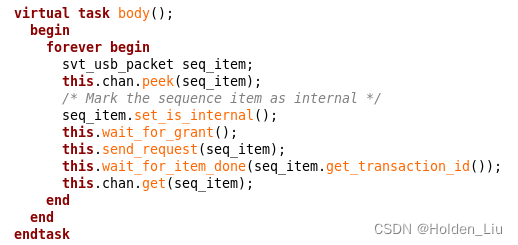

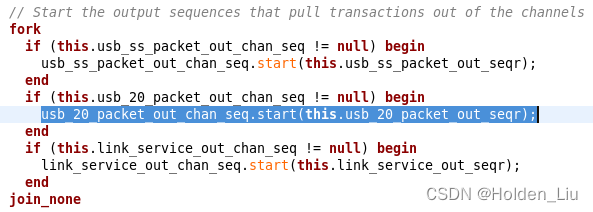

svt_usb_protocol将svt_usb_tranfer类型的tr处理为svt_usb_packet类型的tr,usb_20_packet_out_chan_seqpeek到tr后,通过svt_usb_packet_sequencer将tr发送给link的usb_20_packet_in_port;

sequence中的body函数forever执行:

usb_20_packet_out_chan_seq挂载在svt_usb_packet_sequencer上:

-

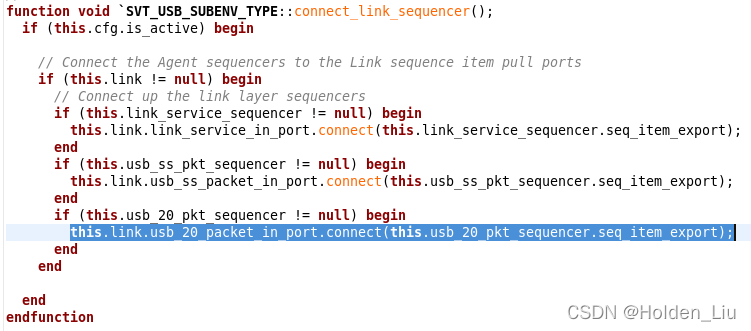

svt_usb_link中的usb_20_packet_in_port在svt_usb_agent通过connect_link_sequencer完成connect

-

和

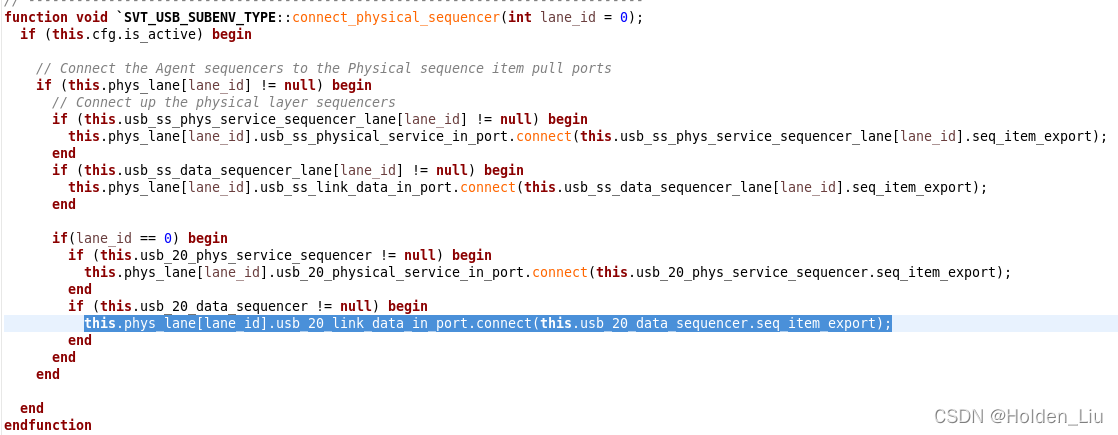

svt_usb_protocol类似,svt_usb_link将svt_usb_packet类型的tr处理为svt_usb_data类型的tr,usb_20_data_out_chan_seqpeek到tr后,通过svt_usb_data_sequencer将tr发送给physical的usb_20_physical_in_port; -

svt_usb_physiacl从usb_20_link_data_in_port获得tr,交由svt_usb_physical_port_20_serial驱动到signal interface上;

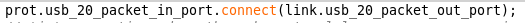

对于RX方向,则是通过connect_protocol_layer、connect_link_layer、完成TLM connet:

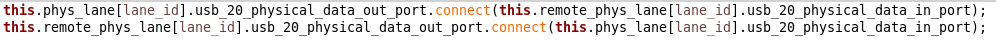

对于remote_phy:

USB3.x和service componet的实现结构类似。

参考

- Verification Methodology and Practices for Coverage Planning and Closure in USB Subsystem

- UVM layering sequence for layered protocol

本文详细介绍了Synopsys的SystemVerilog Verification Technology (SVT) USB Verification Intellectual Property (VIP)如何使用layering sequence构建其agent来模拟layered USB protocol。文章涵盖了VIP的三层结构——Physical, Link, 和 Protocol层,以及它们各自的功能和与testbench的交互方式。特别强调了svt_usb_physical_port的角色以及USB2.0和USB3.x的不同接口类型。此外,还探讨了layering sequence在传输过程中的作用,展示了从transaction生成到物理信号驱动的流程。

本文详细介绍了Synopsys的SystemVerilog Verification Technology (SVT) USB Verification Intellectual Property (VIP)如何使用layering sequence构建其agent来模拟layered USB protocol。文章涵盖了VIP的三层结构——Physical, Link, 和 Protocol层,以及它们各自的功能和与testbench的交互方式。特别强调了svt_usb_physical_port的角色以及USB2.0和USB3.x的不同接口类型。此外,还探讨了layering sequence在传输过程中的作用,展示了从transaction生成到物理信号驱动的流程。

2756

2756

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?