为了能把一个输出信号赋给输出端口,常看到如下的两种处理方式。

方式A:

module test1(clk,counter);

input clk ;

output[7:0] counter ;

reg[7:0] counter_reg ;

always@(posedge clk)

begin

counter_reg<=counter_reg+1 ;

end

assign counter=counter_reg;

endmodule方式B:

module test1(clk,counter);

input clk ;

output reg[7:0] counter ;

always@(posedge clk)

begin

counter<=counter+1'b1 ;

end

endmodule

A是单独设置内部变量,在always中将输出信号赋给counter_reg,让后通过assign将counter和counter_reg连接起来。

B是直接将输出端口设置成reg型信号,直接在always中赋值。

综合的结果表明,两种处理方式的结果一致。

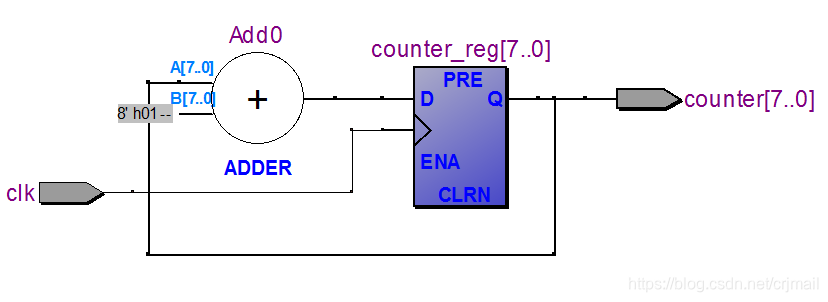

综合后的RTL级视图均为:

本文探讨了Verilog HDL中处理输出信号的两种常见方式:一种是通过内部变量和assign语句连接;另一种是直接使用reg类型的输出端口。文章详细解析了两种方式的具体实现,并指出它们在综合后的RTL级视图上具有一致性。

本文探讨了Verilog HDL中处理输出信号的两种常见方式:一种是通过内部变量和assign语句连接;另一种是直接使用reg类型的输出端口。文章详细解析了两种方式的具体实现,并指出它们在综合后的RTL级视图上具有一致性。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?