引言

近年来,硅/硅锗异质结构已成为新型电子和光电器件的热门课题。因此,人们对硅/硅锗体系的结构制造和输运研究有相当大的兴趣。在定义Si/SiGe中的不同器件时,反应离子刻蚀法(RIE)在图案转移过程中起着重要的作用。这种制造过程通常需要与埋着的SiGe薄膜接触。与这些埋地区域接触需要蚀刻硅并在薄薄的SiGe层中停止。

因此,为了实现精确的图案转移,我们需要一种可控蚀刻的方法。不幸的是,针对SiGe选择性的RIE技术尚未被发现。幸运的是,利用光学发射光谱(OES)可以克服这种对硅蚀刻选择性的不足。因此,我们研究了外延Si/SiGe多堆叠在Cl /SiCl /N气体混合物中的干法蚀刻机理。

实验与讨论

RIE实验是在传统的反应离子蚀刻系统中进行的。在RIE之前,背景压力低于10 Pa,晶片被放置在13.56 MHz射频驱动的铝阴极(直径= 250 mm)覆盖的一个石英板上。根据Si RIE的经验,我们选择了以下流速的Cl2/SiCl/N2、Cl2-8sccm、SiCl - 35 sccm、N2-50 sccm。使用氯是因为由于离子辅助蚀刻机制,它可以产生垂直的侧壁。四氯化硅的加入有助于通过同时解吸来更好地控制沟槽的形成。

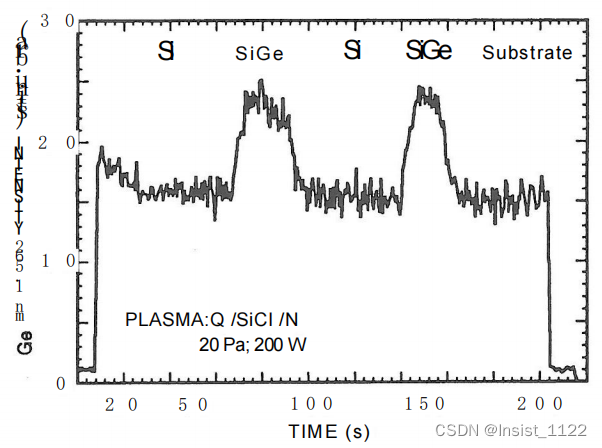

图1显示了样品结构的蚀刻演变。在等离子体点火后约60秒,其中去除天然氧化物膜和硅帽发生时,我们观察到265 nm Ge发射线的强度从其基线上升。在第一次SiGe层蚀刻过程中近似恒定,如果RIE过程继续进入硅层,它则会减小到初始值。第二层掩埋SiGe膜的蚀刻特征是锗发射线的反复增加强度。SiGe的蚀刻速率是Ge含量的函数,并随着Ge含量的增加而增加。

图1:SiGe/Si/SiGe/Si堆栈在RIE过程中,265nmGe谱线的发射强度随时间的函数

结论

为了了解这种小的Ge富集蚀刻,英思特对表面进行了XPS分析,并与足够的未蚀刻样品进行了比较。英思特研究表明这种富集一些可能的原因有:与纯硅的测量速率相比,SiGe合金中Ge的存在显著增加了Si原子的挥发速率。

此外,SiCln的较高挥发性(与GeCln相比)应该会导致该化合物更快的去除,并导致表面轻微的Ge富集。此外,在完成RIE过程后或在AES测量之前的空气接触期间,高活性的SiGe表面氧化也会导致薄氧化物层下的Ge富集。

382

382

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?