1 异步路径和亚稳态

1.1 同步电路和异步电路

广义定义的同步与异步逻辑如下:

CLK间有固定的相位关系或者CLK特征是可预测的被称为同步逻辑;

CLK间没有有固定的相位关系,即CLK特征是不可预测的被称为异步逻辑。

注意:

①同源一定同步,且系统知道同一拍的相对相位关系(超前或滞后),一定是下一拍latch上一拍launch的数据。

②同步仅代表相位关系固定,非同源情况下遇下一个时钟沿即触发。

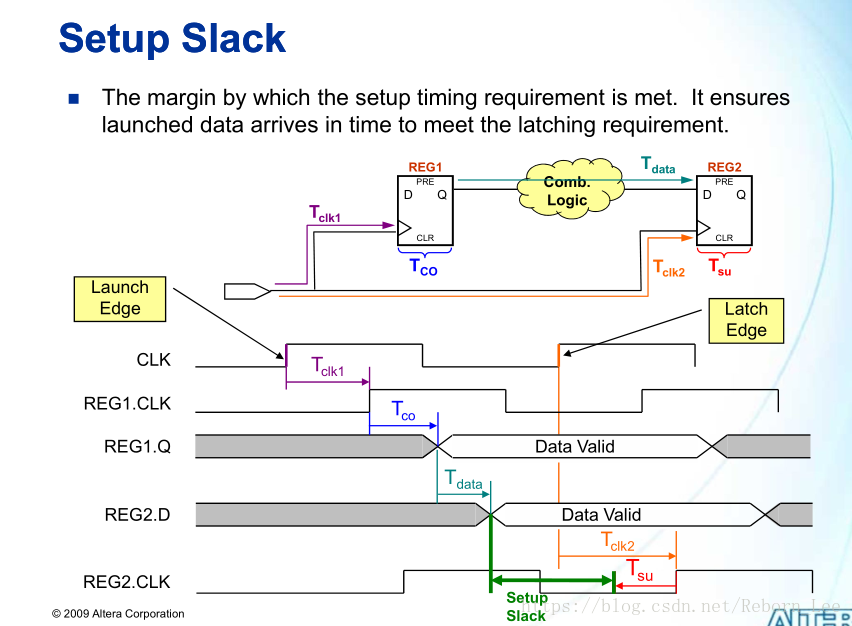

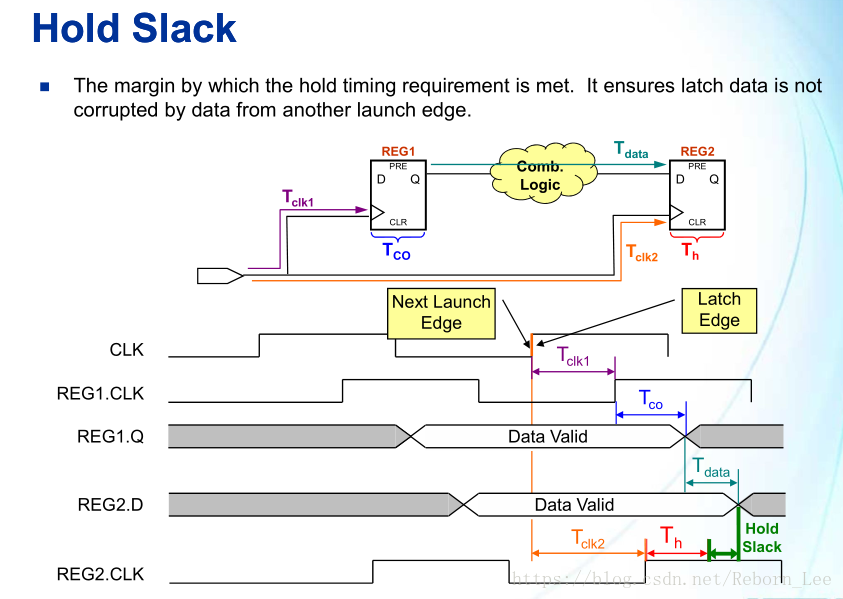

1.2 建立关系和保持关系

详细见静态时序分析(STA)基础。

1.3 亚稳态

在时钟有效沿到来的前后,触发器数据端的数据不稳定导致违反触发器的建立时间或者保持时间,可能引起触发器的输出处于未知的状态,这种未知的状态称为亚稳态。亚稳态是器件的固有属性,不能消除,只能从概率上减少这一状态的发生。

①在同步系统中,组合路径上的延迟过大,触发器D端输入信号只要不满足和

要求就可能会产生亚稳态;

②亚稳态问题通常发生在一些跨时钟信号传输及异步信号采样上;

③异步复位而导致系统电路可能产生亚稳态,因为异步复位信号有可能随时复位在时钟沿的附近,而导致系统产生亚稳态。这一类的解决方式有“异步复位,同步释放”等。

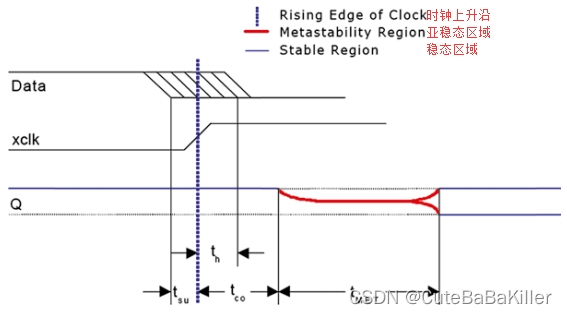

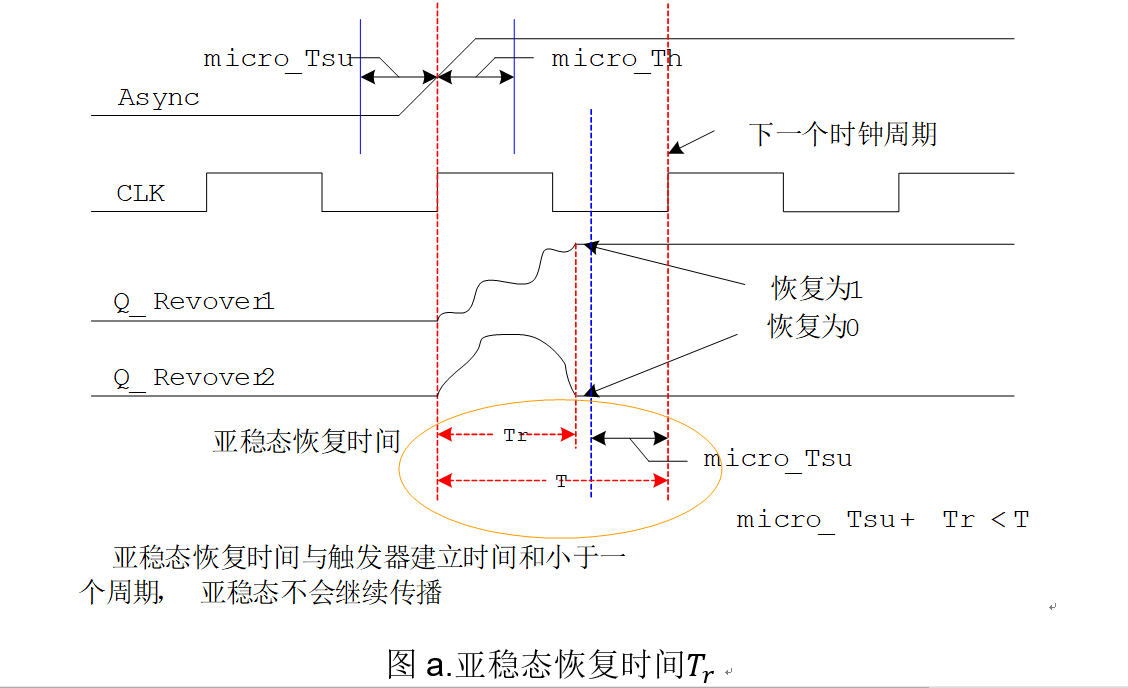

1.3.1 亚稳态的时间

当触发器处于亚稳态时,输出会在高电平和低电平之间徘徊,导致输出转换被延迟,并超过指定时钟的数据输出延迟()。亚稳态输出需要花费超过

的额外时间才能解析为稳定状态(0或1都有可能,不一定是正确电平),该时间称为亚稳态的稳定/振荡/决断时间(resolution time,

,电气特性)。

注意:不包含

,且在

时间段内,触发器的输出Q是稳定的。

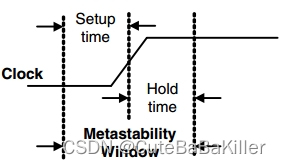

建立时间和保持时间的组合的特定时间长度决定了亚稳态窗口的大小。窗口越大,系统进入亚稳态的机会就越大。

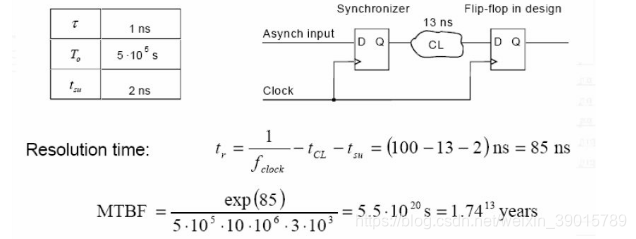

1.3.2 平均故障间隔时间(MTBF)

发生亚稳态并传递到后级触发器的情况的平均时间间隔可以用平均故障间隔时间来描述。MTBF越大,表示系统工作在稳定状态(后级触发器不发生亚稳态,即亚稳态未传递)的概率越大。

:在不引起同步失败的前提下,允许超出器件正常传输延迟时间的最大恢复时间(

)

: 触发器的亚稳态时间常数

:亚稳态窗口

:同步时钟频率

:异步信号边沿频率(异步信号时钟频率)

例如假设触发器的时钟频率为10MHZ,而输入数据频率为3KHZ,则同步器的第1级触发器的MTBF如下图所计算的(忽略了时钟偏斜/clock skew):

总结:在忽略电气特性、环境以及clk频率固定的情况下,MTBF与Setup Slack正相关。

增大MTBF的方法:

①提高工艺,使用更快的触发器,触发器、

和

都会变小,

和

也会变小;

②降低输入数据翻转频率(toggling frequency);

③降低同步触发器的时钟频率;

④减小触发器间的组合逻辑时延。

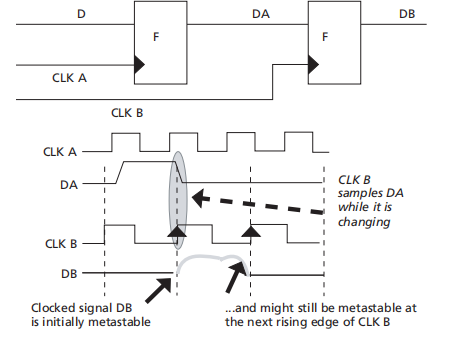

1.3.3 亚稳态的危害与传递

亚稳态的危害主要体现在破坏系统的稳定性。由于输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值,因此亚稳态除了导致逻辑误判之外,输出0~1之间的中间电压值还会使下一级产生亚稳态(即导致亚稳态的传播)。逻辑误判有可能通过电路的特殊设计减轻危害,而亚稳态的传播则扩大了故障面。另外,在亚稳态状态下,任何诸如噪声、电源干扰等细微扰动将导致更恶劣的状态不稳定,这时这个系统的传输延时增大,状态输出错误,在某些情况下甚至导致会使寄存器在两个有效判定门限之间长时间振荡。

如上图所示,亚稳态恢复时间。当恢复时间较小时,输出Q能在下一周期到来前稳定,否则输出Q在下一周期到来后未能恢复到稳定状态(不满足Q输入的寄存器的建立时间)这就会使得下一级触发器也发生亚稳态,即亚稳态发生了传递。

2 跨时钟典型电路设计

2.1 同步器

2.1.1 定义

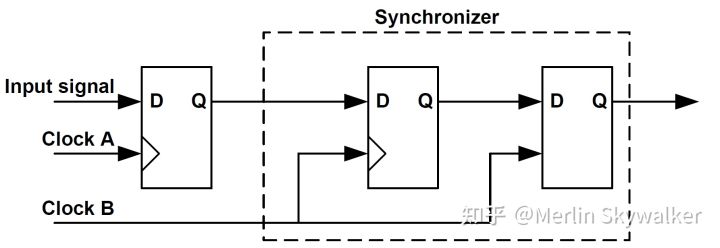

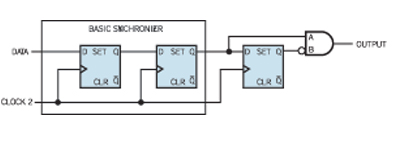

同步器的目的是为了防止目的时钟域中的第一级触发器的亚稳态对后级逻辑造成影响。例如最简单的两级触发器作为同步器来说,其中间没有任何组合逻辑,这种设计可以保证后级触发器在获得前级触发器输出时,前级触发器已经退出亚稳态即输出已经稳定。

①同步器中级联的触发器越多,发生亚稳态的概率就越小。两级同步器的MTBF大小大概是一级同步器的平方。建议主频<1GHz使用2级串联,更高主频时采用3级串联。

②同步器中的触发器间的位置尽可能靠近,原因如下:

根据,减小触发器间的组合逻辑时延(

,这里主要是线延时),会增加有效亚稳态沉降时间(vailable metastability settling time)

或

。而对于时钟偏斜(clock skew),由于clock skew可正可负,与Setup Slack的相关性也可正可负,且在clock tree balance之后可以忽略不计。

2.1.2 同步器应用场景注意

①禁止直接裸跨

单触发器甚至是直接跨时钟域无法抑制可能产生的亚稳态继续传播。

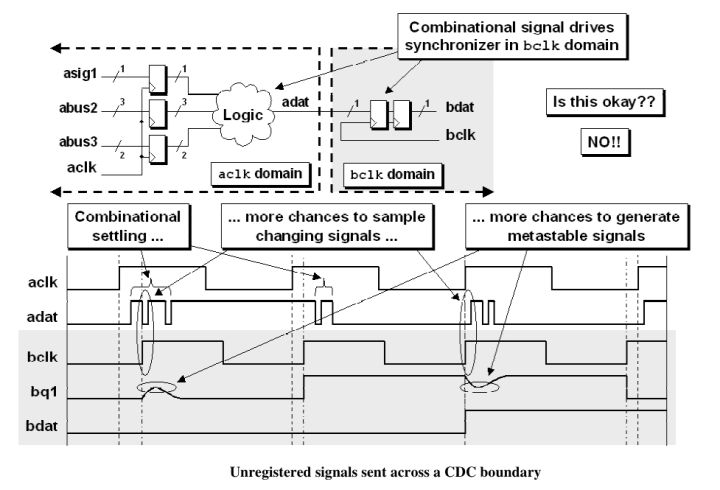

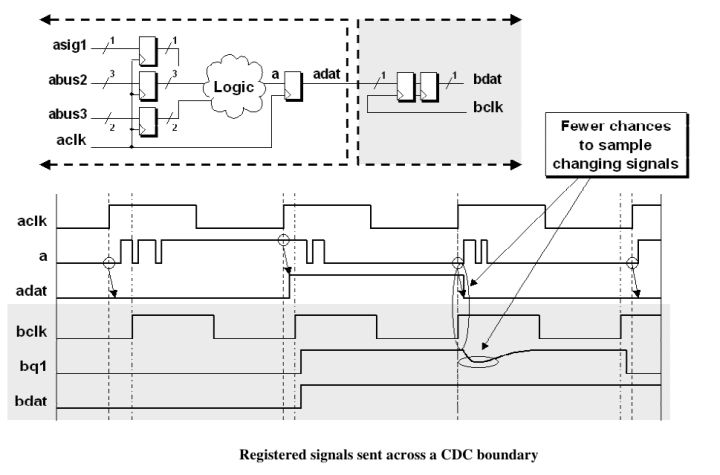

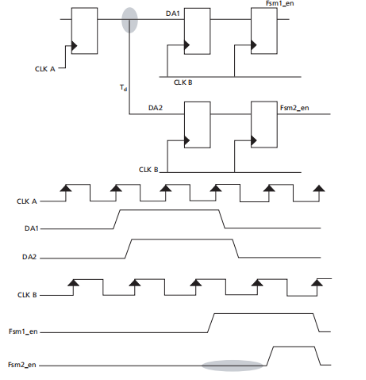

②跨时钟域信号在同步前必须是源时钟寄存器输出,禁止组合逻辑输出。

组合逻辑电路在输入变化时输出可能出现毛刺(glitch),导致数据变化太快减小MTBF,增加亚稳态发生的概率。正确的做法是在adat前加一级触发器寄存输出,当adat是FF的输出时,那么根据FF的特性,输出在一个时钟周期内是不会改变的,数据的变化频率不会超过时钟频率,这样就能降低跨时钟信号变化的频率,减小亚稳态发生的概率,如下图所示。

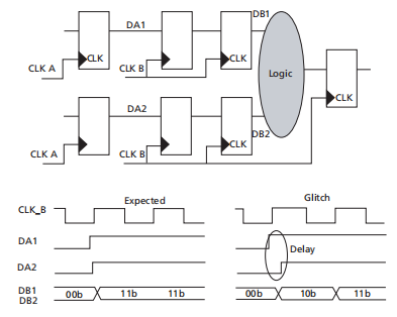

③禁止异步多bit关联信号直接分开使用同步器来跨时钟域,这里包含两种场景:

a、多路扇出:同一异步信号多路扇出(即变为多bit的关联信号)后分别使用同步器跨时钟域。

b、重新聚合:多bit异步信号分别使用同步器跨时钟域后汇入组合逻辑,即视为关联信号。

两种应用场景的错误:目的时钟域下的多路同步器的输入由于传输delay的不同产生错拍,只要有两路及以上的输入值同拍即会产生不期望的中间值,后经由同步器跨时钟域后信号间的逻辑关系发生错误。

2.1.3 同步器的分类

同步器的类型基本上有三种:电平、边沿检测和脉冲。

2.1.3.1 电平同步器

电平信号是指信号变化后会稳定一定的时间,不小于采样时钟的2个周期,对于这种单bit电平信号即可直接使用同步器。

如图所示,bclk的第一级FF输出发生亚稳态,亚稳态维持了一段时间,并在下一个时钟上升沿稳定,被识别为高,这样第二级的FF就能正确的将adat采样到了bq2_dat。但是另外两种种可能:

①如果亚稳态维持的时间不止一个周期,在下一个时钟上升沿没有稳定,那么第二级的FF就也会进入亚稳态。那么这种情况的概率是多少呢?就是我们上面描述的1/MTBF。

②第一级的亚稳态在下一个时钟上升沿稳定,但是被识别为0,那么第二级的FF输出bq2_dat就是0,说明信号跨时钟采样失败。但是这种情况不会造成亚稳态的传播,也就是不会影响后面的设计。针对这种情况,我们一般会改变设计,禁止让快时钟域的单cycle脉冲跨时钟到慢的时钟内采样。

2.1.2 适用范围

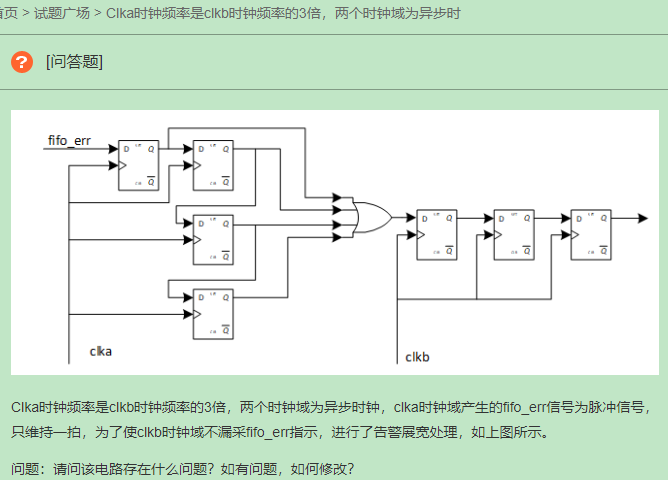

①单bit信号:original signal pulse width no less than 2 period of dest clock,即源时钟域的信号电平保持长度不能小于目的时钟域周期(最好是2倍),否则会漏采,需要展宽操作;

②gray-code形式:例如采样错误对设计无影响的FIFO Gray同步。

注意:采样时钟的频率需要大于输入数据频率的2倍(建议3倍以上),或者输入数据的有效电平稳定时间大于采样时钟周期(建议1.5倍或2倍以上)。

2.1.3 应用注意

同步器

同步器输入:源时钟寄存

展宽电路

应该在clka的组合逻辑输出后添加一个clka时钟域的FF输出给clkb。

边沿检测

时钟切换

异步复位,同步释放

握手

fifo

边沿检测同步器在电平同步器的输出端增加了一个触发器(图 2)。新增触发器的输出经反相后和电平同步器的输出进行与操作。这一电路会检测同步器输入的上升沿,产生一个与时钟周期等宽、高电平有效的脉冲。如果将与门的两个输入端交换使用,就可以构成一个检测输入信号下降沿的同步器。将与门改为与非门可以构建一个产生低电平有效脉冲的电路。

图2,边沿检测同步器在电平同步器的输出端增加了一个触发器。

当一个脉冲进入更快的时钟域中时,边沿检测同步器可以工作得很好。这一电路会产生一个脉冲,用来指示输入信号上升或下降沿。这种同步器有一个限制,即输入脉冲的宽度必须大于同步时钟周期与第一个同步触发器所需保持时间之和。最保险的脉冲宽度是同步器时钟周期的两倍。如果输入是一个单时钟宽度脉冲进入一个较慢的时钟域,则这种同步器没有作用,在这种情况下,就要采用脉冲同步器。

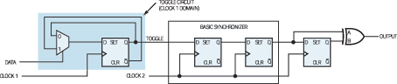

脉冲同步器的输入信号是一个单时钟宽度脉冲,它触发原时钟域中的一个翻转电路(图 3)。每当翻转电路接收到一个脉冲时,它就会在高、低电平间进行转换,然后通过电平同步器到达异或门的一个输入端,而另一个信号经一个时钟周期的延迟进入异或门的另一端,翻转电路每转换一次状态,这个同步器的输出端就产生一个单时钟宽度的脉冲。

图3,脉冲同步器的输入信号是一个单时钟宽度脉冲,它触发原时钟域中的一个翻转电路

脉冲同步器的基本功能是从某个时钟域取出一个单时钟宽度脉冲,然后在新的时钟域中建立另一个单时钟宽度的脉冲。脉冲同步器也有一个限制,即输入脉冲之间的最小间隔必须等于两个同步器时钟周期。如果输入脉冲相互过近,则新时钟域中的输出脉冲也紧密相邻,结果是输出脉冲宽度比一个时钟周期宽。当输入脉冲时钟周期大于两个同步器时钟周期时,这个问题更加严重。这种情况下,如果输入脉冲相邻太近,则同步器就不能检测到每个脉冲。

本文探讨了同步电路与异步电路的区别,着重讲解了亚稳态在时钟路径中的影响,包括建立时间、保持时间与MTBF的关系。针对跨时钟电路设计,介绍了同步器的作用、分类(电平、边沿检测、脉冲)以及在不同应用场景下的注意事项。

本文探讨了同步电路与异步电路的区别,着重讲解了亚稳态在时钟路径中的影响,包括建立时间、保持时间与MTBF的关系。针对跨时钟电路设计,介绍了同步器的作用、分类(电平、边沿检测、脉冲)以及在不同应用场景下的注意事项。

2101

2101

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?