1.简介

FIFO( First Input First Output)简单说就是指先进先出。FIFO存储器是一个先入先出的双口缓冲器,即第一个进入其内的数据第一个被移出,其中一个口是存储器的输入口,另一个口是存储器的输出口。

对于单片FIFO来说,主要有两种结构:触发导向结构和零导向传输结构。触发导向传输结构的FIFO是由寄存器阵列构成的,零导向传输结构的FIFO是由具有读和写地址指针的双口RAM构成。

FIFO与普通RAM存储器的区别是没有外部读写地址线(指针),使用方便,但缺点是只能顺序写入数据和读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

1.1.功能

FIFO存储器是系统的缓冲环节,主要有几方面的功能:

1)对连续的数据流进行缓存,防止在进机和存储操作时丢失数据;

2)数据集中起来进行进栈和存储,可避免频繁的总线操作,减轻CPU的负担;

3)允许系统进行DMA操作,提高数据的传输速度。这是至关重要的一点,如果不采用DMA操作,数据传输将达不到传输要求,而且大大增加CPU的负担,无法同时完成数据的存储工作。

1.2.用途

1.2.1.跨时钟域多bit数据传输

解决一个系统多个时钟所带来的问题:异步时钟之间的接口电路。异步FIFO是解决这个问题的一种便捷简单的方案,使用异步FIFO可以在两个不同时钟系统之间快速方便地传输实时数据。

1.2.2.达到数据匹配问题(读写位宽不一致)

对于不同宽度的数据接口也可以使用FIFO,例如单片机的8位输出而DSP可能是16位输入,在单片机与DSP连接时就可以使用FIFO来达到数据匹配的目的。

1.3.主要参数

- 宽度(WIDTH):FIFO每个地址的数据位宽(W);

- 深度(DEEPTH):FIFO可以存储多少个W位的数据;

- 满(full)标志:FIFO已满或将满时,会输出一个对写操作的反压信号,以阻止被继续写入数据而溢出;

- 空(empty)标志:FIFO已空或将空时,会输出一个对读操作的反压信号,以避免被继续读出无效数据;

- 读/写时钟:读/写操作所遵循的时钟,每个时钟沿触发。

根据FIFO工作的时钟域分为同步/异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟在时钟沿来临时同时发生读写。异步FIFO读写时钟不一致,读写相互独立。

读写指针即读写地址,当前读/写操作完成后,指针自动加一指向下一个地址(连续递增)。

- 写指针:总是指向下一个将要被写入的地址,复位时指向编号0的地址;

- 读指针:总是指向下一个将要被读出的数据地址,复位时也指向编号0的地址且此时数据无效;

2.工作原理

2.1.空满标志

2.1.1.读空信号(rd_empty)

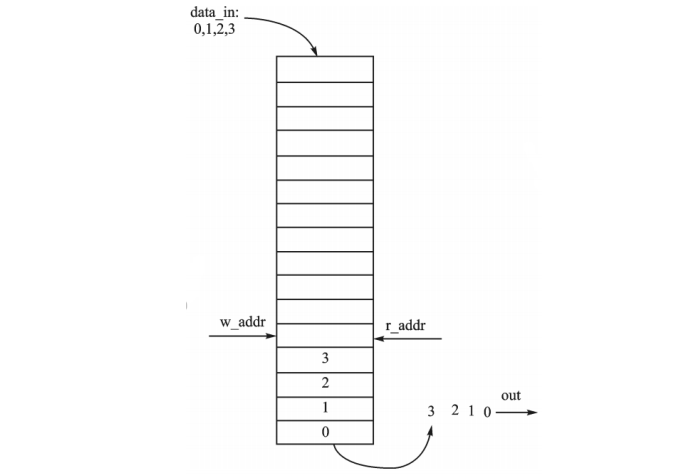

一般情况下当读写指针相等时,表明FIFO已空,这种情况发生在复位操作时或当读指针读出FIFO中最后一个有效数据时(即读指针追赶上写指针),此时读空信号有效,如下左图:

2.1.2.写满信号(wr_full)

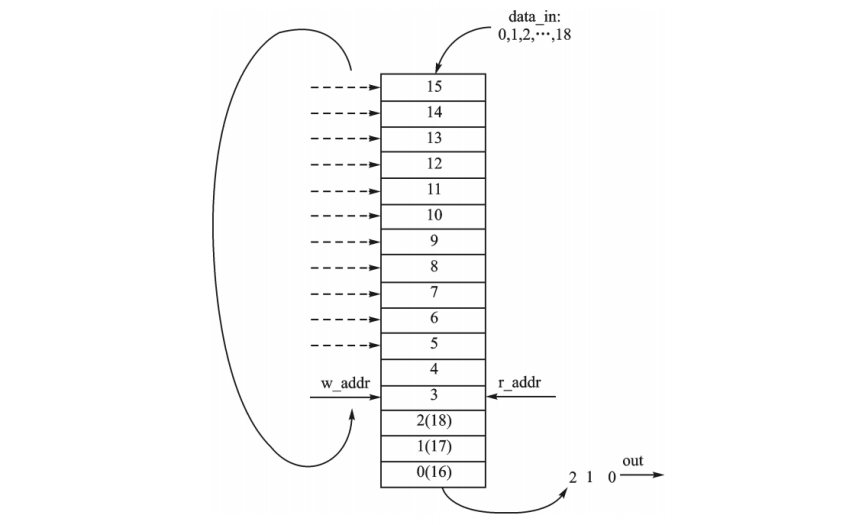

当读写指针再次相等时,即写指针转了一圈又折回来(wrapped around)从起始低位追上了读指针(写比读快),此时表明FIFO已满,如上右图:

2.2.空满判断机制

2.2.1.同步fifo空满判断

- 方案一:extra bit

深度为的FIFO其地址位宽为n,若数据位宽为W则该FIFO的容量为N*W bits。

现在在指针添加1个extra bit即地址的MSB,使其变为n+1 bits,该extra bit用来指示读/写

FIFO是一种先进先出的存储器,常用于数据缓冲,解决异步时钟域间的数据传输问题。它有读写指针自动加一的特性,提供满和空标志以防止溢出和无效读取。FIFO的空满判断可通过地址位的额外位或数据计数器实现。同步FIFO和异步FIFO在空满判断上有不同策略,异步FIFO通常需要格雷码和时钟同步来确保正确性。

FIFO是一种先进先出的存储器,常用于数据缓冲,解决异步时钟域间的数据传输问题。它有读写指针自动加一的特性,提供满和空标志以防止溢出和无效读取。FIFO的空满判断可通过地址位的额外位或数据计数器实现。同步FIFO和异步FIFO在空满判断上有不同策略,异步FIFO通常需要格雷码和时钟同步来确保正确性。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

650

650

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?