1 同步复位

示例:

always@(posedge clk) //没有“or negedge reset”

if(!reset) begin

out2 <= 0 ;

else

out2 <= in2;1.1 优点

①一般能够确保电路是百分之百同步的。

②确保复位只发生在有效时钟沿,可以作为过滤掉毛刺的手段。

1.2 缺点

①复位信号属于数据路径的一部分

②复位信号的有效时长必须大于时钟周期,且在时钟的有效边沿才能真正被系统识别并完成复位。同时还要考虑如:时钟偏移、组合逻辑路径延时、复位延时等因素。

③由于大多数的厂商目标库内的触发器都只有异步复位端口,采用同步复位的话,就会耗费较多的逻辑资源。

2 异步复位

示例:

always@(posedge clk or negedge reset) //异步复位

if(!reset) begin

out1 <= 0 ;

else

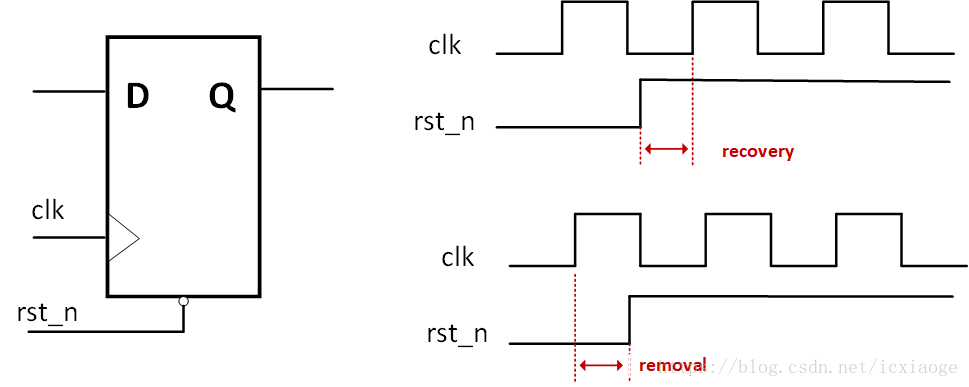

out1 <= in1 ;2.1 recovery time和removal time

在同步电路中,输入数据需要与时钟满足setup time和hold time才能进行数据的正常传输,防止亚稳态。同样的道理,对于一个异步复位寄存器来说,同样异步复位信号同样需要和时钟满足recovery time和removal time 才能有效进行复位操作和复位释放操作,防止输出亚稳态。

recovery time(恢复时间):

撤销复位时

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

225

225

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?