问题由来

一次仿真中发现信号的变化跟预期不一致,分析之下感觉不合逻辑,因此怀疑是有某个地方有force的动作,那么如何check是否有force呢?

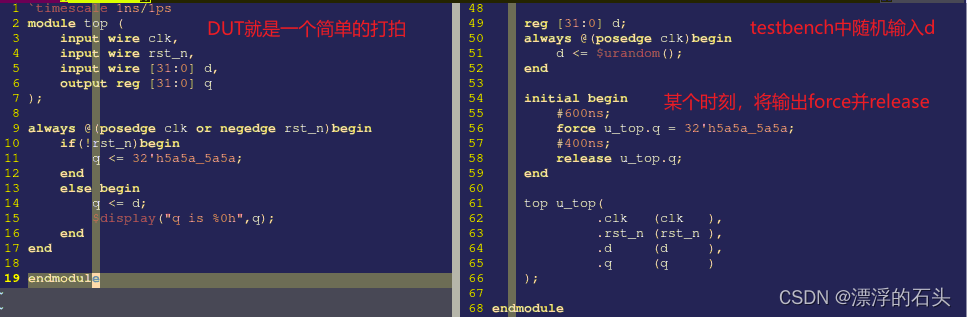

因此做了一个小实验来检查是否有force动作,简单代码如下:

解决办法

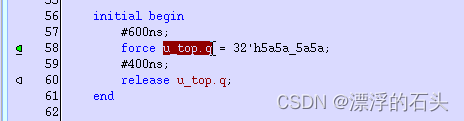

- 最直接的办法,就是在波形中不合理的时刻,双击该信号的跳变沿,可以直接在工程中显示出该信号跳变的驱动位置

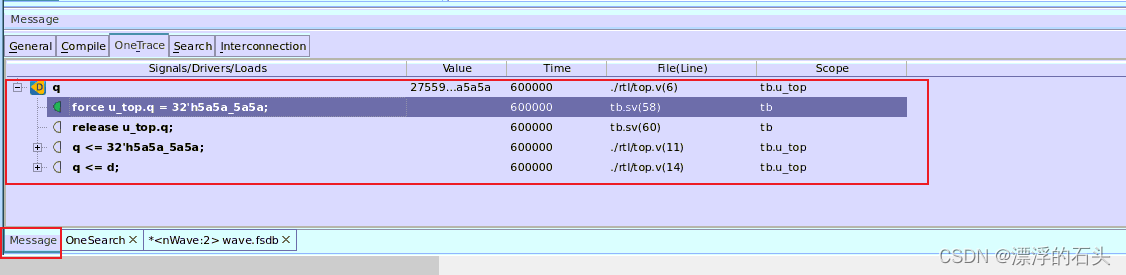

如果因为驱动的位置较多,可以进一步点击Verdi下方Message窗口,可以显示出所有驱动该信号的位置,看下有没有force的动作

注:这里显示的每行信号都可以双击跳转到工程中相应的位置

- 仿真时添加参数

+fsdb+force重新仿真一遍,如果有force动作,那么波形中会有显示

注:是仿真阶段,不是编译阶段

示例如下:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3484

3484

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?