基于NIOS-II软核实现流水灯+串口输出

引言:

在现代电子设计领域,FPGA(现场可编程门阵列)因其灵活性和并行处理能力而成为实现复杂数字系统的首选平台。Nios II,作为Altera(现为Intel旗下)提供的软核处理器,为FPGA提供了强大的处理核心,使得FPGA的应用领域得以进一步扩展到嵌入式系统设计。

·

本次实验的核心目标是利用Nios II软核处理器的软件编程能力,结合硬件描述语言(HDL)的硬件实现,完成两个基础而经典的任务:流水灯控制和串口数据输出。这不仅将加深对Nios II处理器编程的理解,也将熟悉FPGA硬件的串口通信接口。

- 流水灯控制部分将通过编写C代码,控制FPGA上的LED灯依次点亮,形成流水灯效果,以此来练习基本的输入输出操作和时间控制逻辑。

- 串口数据输出部分则要求我通过编写串口通信程序,实现通过串口终端与FPGA之间的数据传输,这将涉及到串口配置、数据发送和接收等关键技术点。

希望你在本次学习过后,能够有一定的收获!!!

推荐歌曲—Call of Silence-Haru&CHANYEONG KIM

冲啊!!!! ٩(͡๏̯͡๏)۶ ٩(͡๏̯͡๏)۶ ٩(͡๏̯͡๏)۶

一、任务介绍

1) 了解Nios II软核

Nios II软核处理器是一款可定制的嵌入式处理器,运行在FPGA内部,由Altera(现为Intel FPGA)提供。它支持多种配置选项,包括不同的流水线级别、缓存大小、中断和异常处理等。了解Nios II软核对于掌握如何利用FPGA进行复杂系统设计至关重要。

目标:

- 学习Nios II处理器的基本架构和工作原理。

- 熟悉Nios II软核的开发工具和环境。

- 理解如何对Nios II软核进行配置以满足特定应用需求。

2) 了解Qsys

Qsys(原名AES)是Altera提供的一种基于图形的集成开发环境,用于快速设计和集成复杂的系统。通过Qsys,可以轻松地将Nios II软核与其他IP核(如内存控制器、外设接口等)集成在一起,形成完整的系统。

目标:

- 掌握Qsys的基本使用,包括组件的选择、连接和配置。

- 学习如何通过Qsys生成定制的系统,并将Nios II软核与所需的外设和接口集成。

- 理解Qsys生成的系统如何映射到FPGA硬件上。

3) 实现流水灯

流水灯是FPGA设计中的一个经典实验,通过控制一组LED灯依次点亮来模拟流水效果。该任务将结合硬件描述语言和Nios II软件编程来实现。

目标:

- 学习如何在FPGA上实现流水灯的硬件逻辑。

- 编写C代码,控制LED灯的顺序点亮,形成动态流水灯效果。

- 掌握基本的输入输出操作和时间控制逻辑。

4) 实现串口输出

串口是一种常用的异步通信接口,广泛应用于嵌入式系统的数据交换。本任务要求通过Nios II处理器实现串口通信,完成数据的发送和接收。

目标:

- 学习串口通信的基本原理和相关的参数设置(如波特率、数据位、停止位等)。

- 编写C代码,实现通过串口发送数据到外部设备(如PC机)。

- 掌握使用Nios II处理器进行串口通信的方法,包括初始化串口、发送数据和接收数据。

二、Nios II软核

2.1 Nios II软核概述

Nios II是应用于Intel FPGA的嵌入式软核处理器,它是Qsys嵌入式系统的核心部件,具有较强的性能和可定制特性。我们可以在一片FPGA内部构建多个Nios II处理器,它们可以作为主CPU,也可以是协处理器,在同一芯片内部协调有序地完成整个复杂系统的各项功能。Nios II处理器内核是32位RISC架构(精简指令集架构)处理器,它包含了大多数现代32位处理器中常见的基本架构元素,包括:

⚫ 32位指令大小

⚫ 32位数据线与地址线

⚫ 32个通用寄存器

⚫ 32个外部中断源

⚫ 可配置的指令高速缓存

⚫ 可配置的数据高速缓存

⚫ 用于集成定制外设的通用接口

Nios II处理器的结构框图如下所示,从图中我们还可以看到,Nios II提供了JTAG接口

供用户下载和调试程序。

2.2 Nios II软核特性

Nios II软核提供了一系列高级特性,包括:

- 流水线架构:支持从三级到八级流水线的配置,以平衡性能和资源消耗。

- 哈佛架构:具有独立的指令和数据缓存,提高了数据访问速度。

- 中断和异常处理:支持多达32个中断源和异常处理,增强了系统的响应能力。

- 丰富的外设支持:包括定时器、串口、JTAG调试等标准外设。

- 定制指令:允许用户根据自己的需求添加定制指令,进一步提升性能。

- 低功耗设计:优化了功耗管理,适合电池供电的便携式设备。

2.3 Nios II软核开发工具

开发Nios II软核应用程序涉及到以下工具:

- Nios II集成开发环境(IDE):提供了代码编辑、编译、调试和性能分析的集成解决方案。

- Qsys:一个基于图形的系统构建工具,用于快速集成Nios II软核与其他IP核。

- Nios II C/C++编译器:用于将编写的C/C++代码编译成FPGA可执行的机器代码。

- Nios II硬件仿真模型:在仿真环境中模拟Nios II软核的行为,便于早期设计验证。

2.4 Nios II软核在FPGA设计中的应用

在FPGA设计中,Nios II软核可以用于:

- 控制逻辑实现:通过编写C/C++代码实现复杂的控制逻辑,减轻硬件逻辑设计的负担。

- 数据处理:利用Nios II软核的计算能力,处理来自传感器或其他外设的数据。

- 通信协议处理:实现各种通信协议,如SPI、I2C、Ethernet等。

- 用户界面管理:通过连接显示器或其他输出设备,提供用户交互界面。

- 系统集成:作为系统的核心,集成多种外设和功能,构建完整的系统解决方案。

2.5 Nios II软核的学习和使用

为了充分利用Nios II软核的能力,需要:

- 理解计算机组成原理:掌握处理器的基本工作原理,包括指令执行、内存管理等。

- 学习Nios II体系结构:熟悉Nios II软核的特定特性和编程模型。

- 实践编程技能:通过编写和调试C/C++代码,提高软件编程能力。

- 掌握系统设计方法:学习如何使用Qsys工具进行系统级别的设计和集成。

通过深入学习和实践,可以充分发挥Nios II软核在FPGA设计中的潜力,实现高效、可靠的定制化系统解决方案。

三、Qsys

Qsys是什么

Qsys的前身是“SOPC Builder”,在最新的Quartus版本中,Qsys再次被升级为“Platform Designer”。因此在我们看到“Platform Designer”时,要知道它实际上就是我们所常用的Qsys。

Qsys是Quartus II中的一个系统集成工具,它是用来搭建、开发以及维护“系统”的平台,这个系统通常是指以Nios II处理器为核心的嵌入式系统,当然它也可以不包含Nios II处理器。我们知道,嵌入式开发需要同时具备硬件环境和软件程序,Qsys就是用来创建硬件环境的。它不同于ARM、单片机等处理器的固定硬件环境,而是可以根据自己的需求来搭建硬件环境,这也这是它的独到和创新之处。一个基本的Qsys系统框图如下所示:

利用Qsys所搭建的一个基本的嵌入式系统包含系统时钟、Nios II处理器、JTAG接口、ROM和RAM等。其中,Nios II处理器是Qsys系统中最为核心的一个IP核,它是系统的调控中心,负责中断分配、地址管理、内存调度等控制任务。而GPIO(通用输入输出接口)、SDRAMController等外设控制器负责与外部设备连接,控制外设的行为。Nios II和各个外设控制器之间通过Avalon总线通信。

四、实验流程

4.1 硬件设计

4.1.2 创建工程

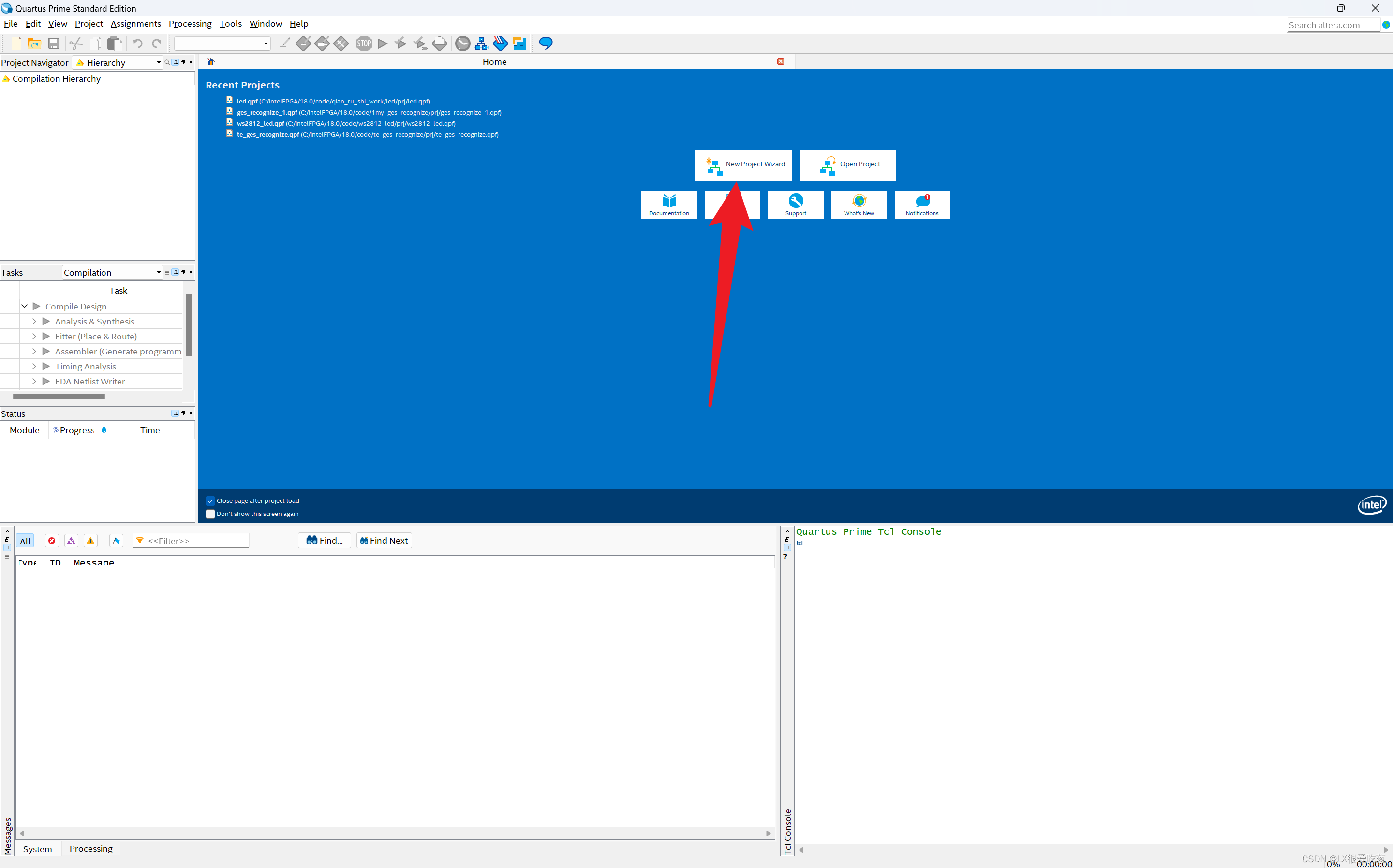

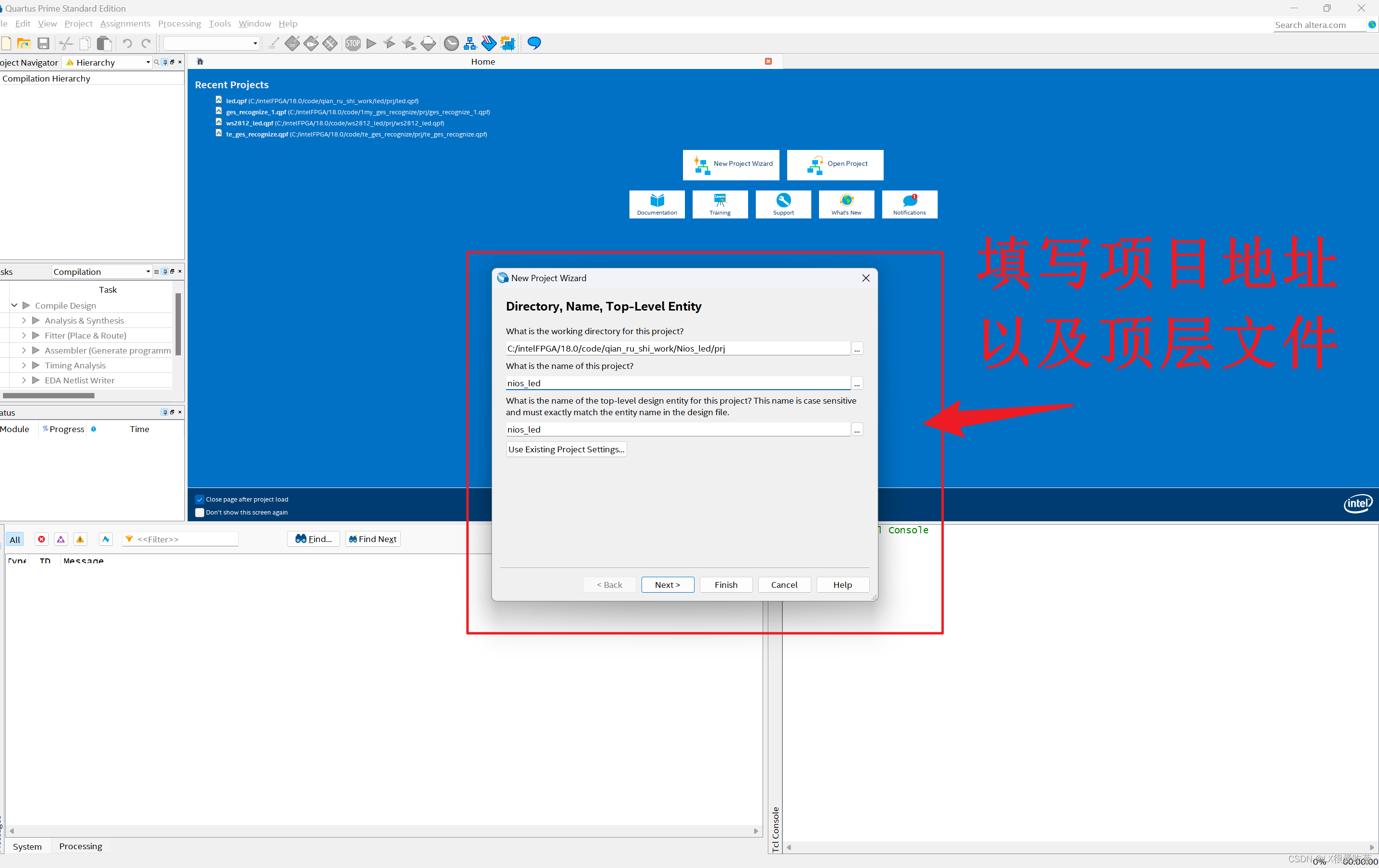

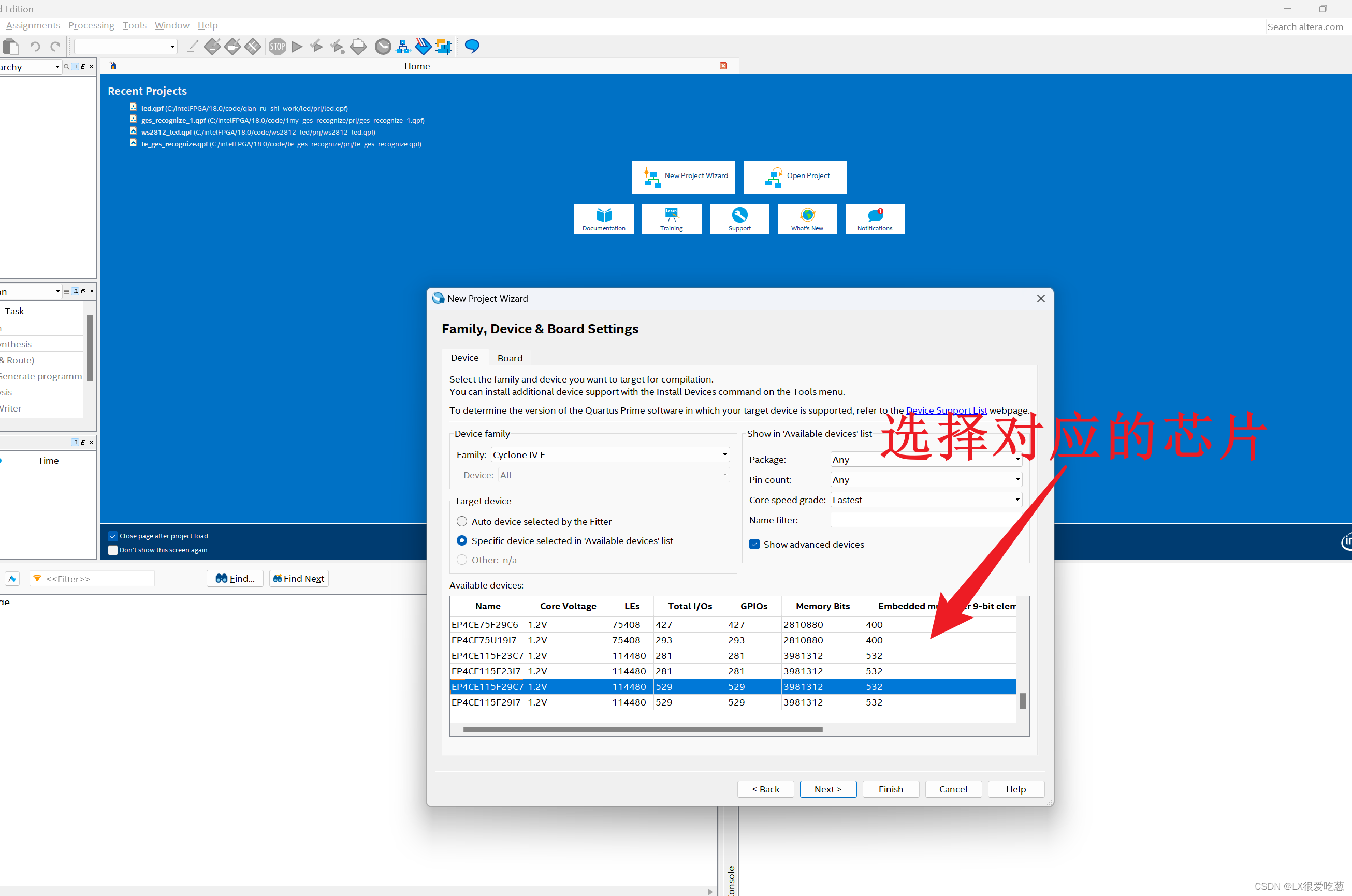

启动 Quartus II 软件,选择File->New Project Wizard,在出现的界面下先Next,填写工程的路径和名称,然后接着Next,直到出现下面界面并进行相应操作。接着一路Next,直到Finish,完成工程的创建。

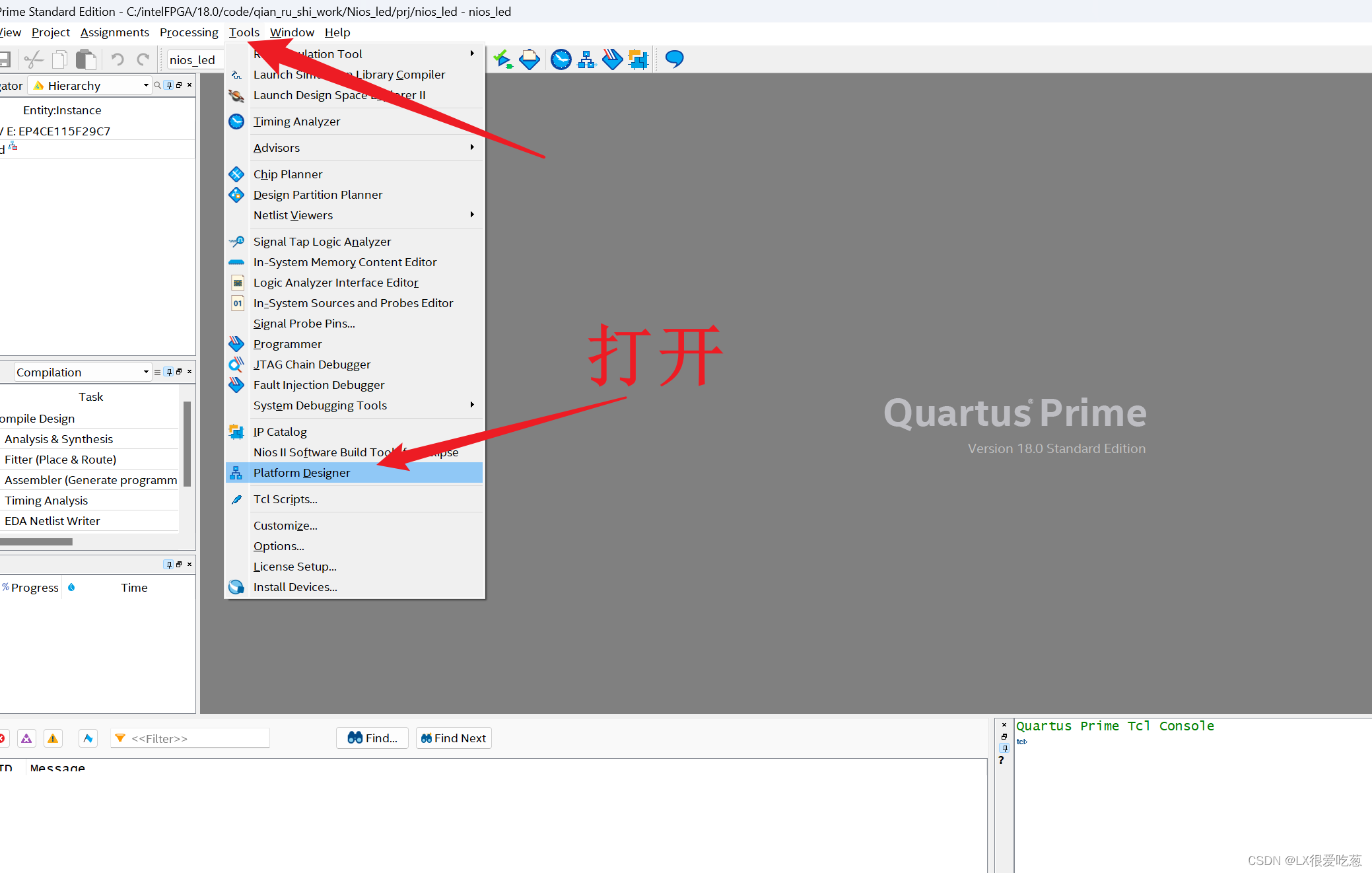

4.1.2 使用Qsys

选择Tools->Qsys

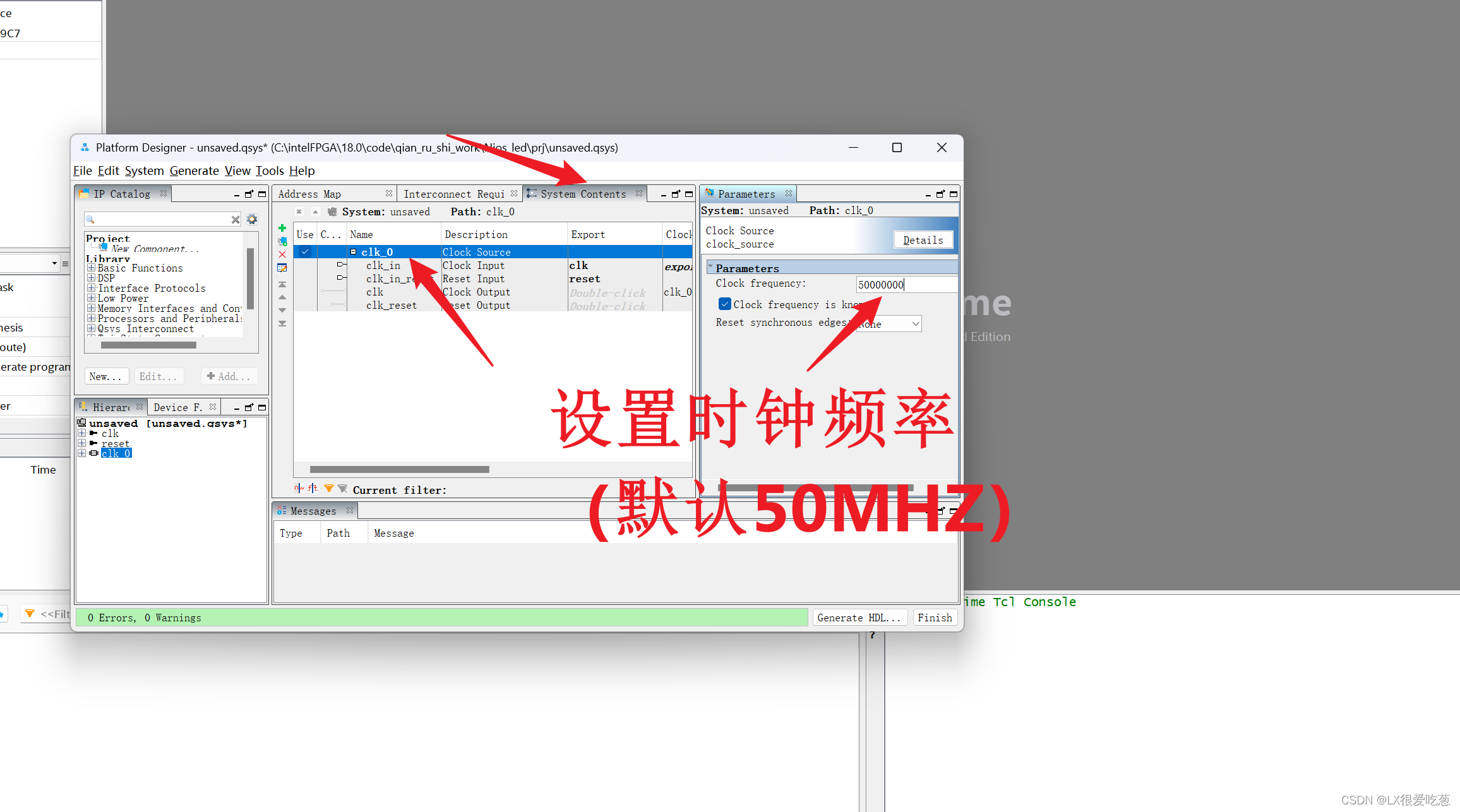

①系统时钟的设置

双击System Contents中的clk_0

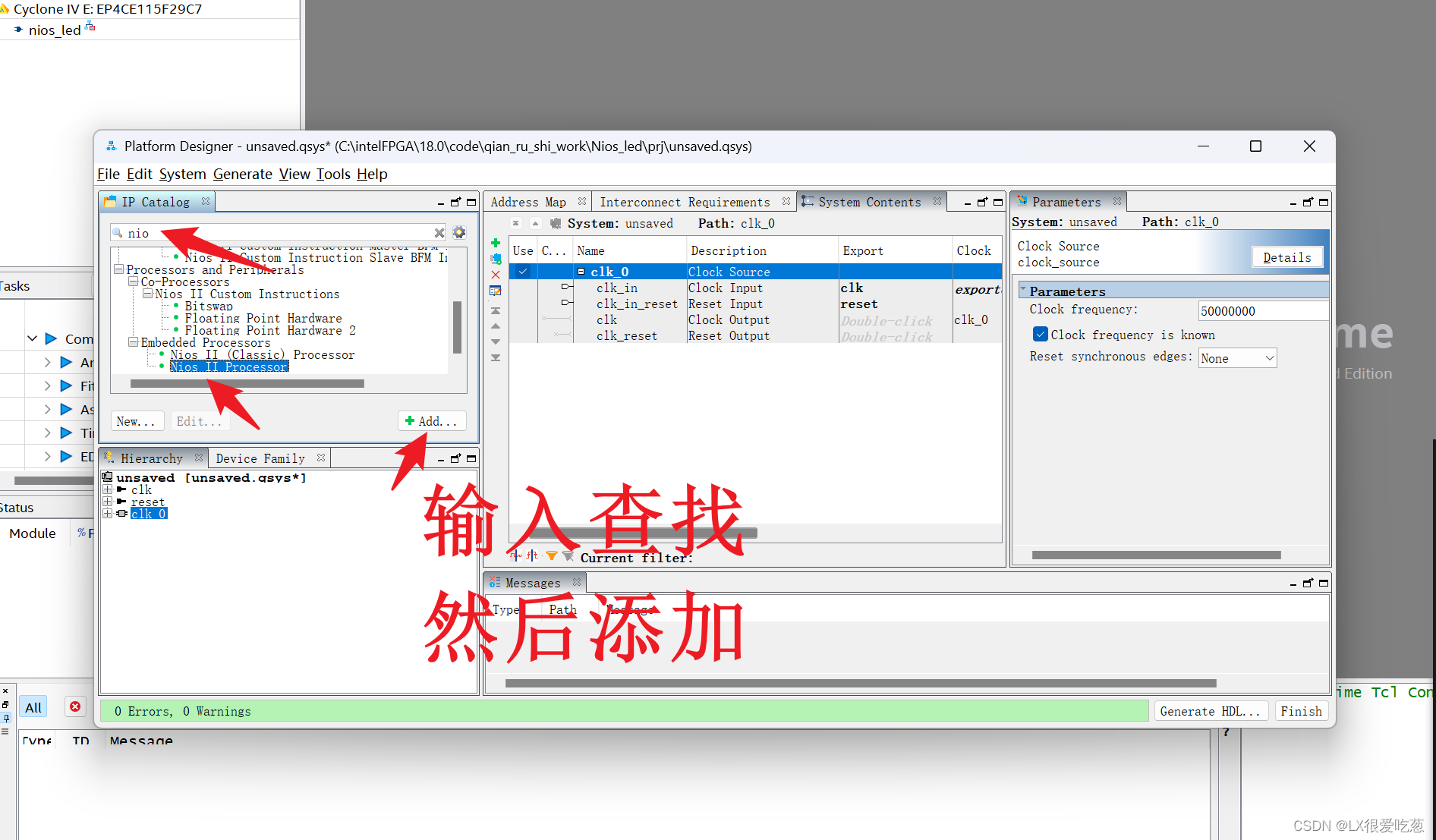

②Nios II Processor的添加

在搜索框中,输入nio,找到Nios II Processor,点击Add

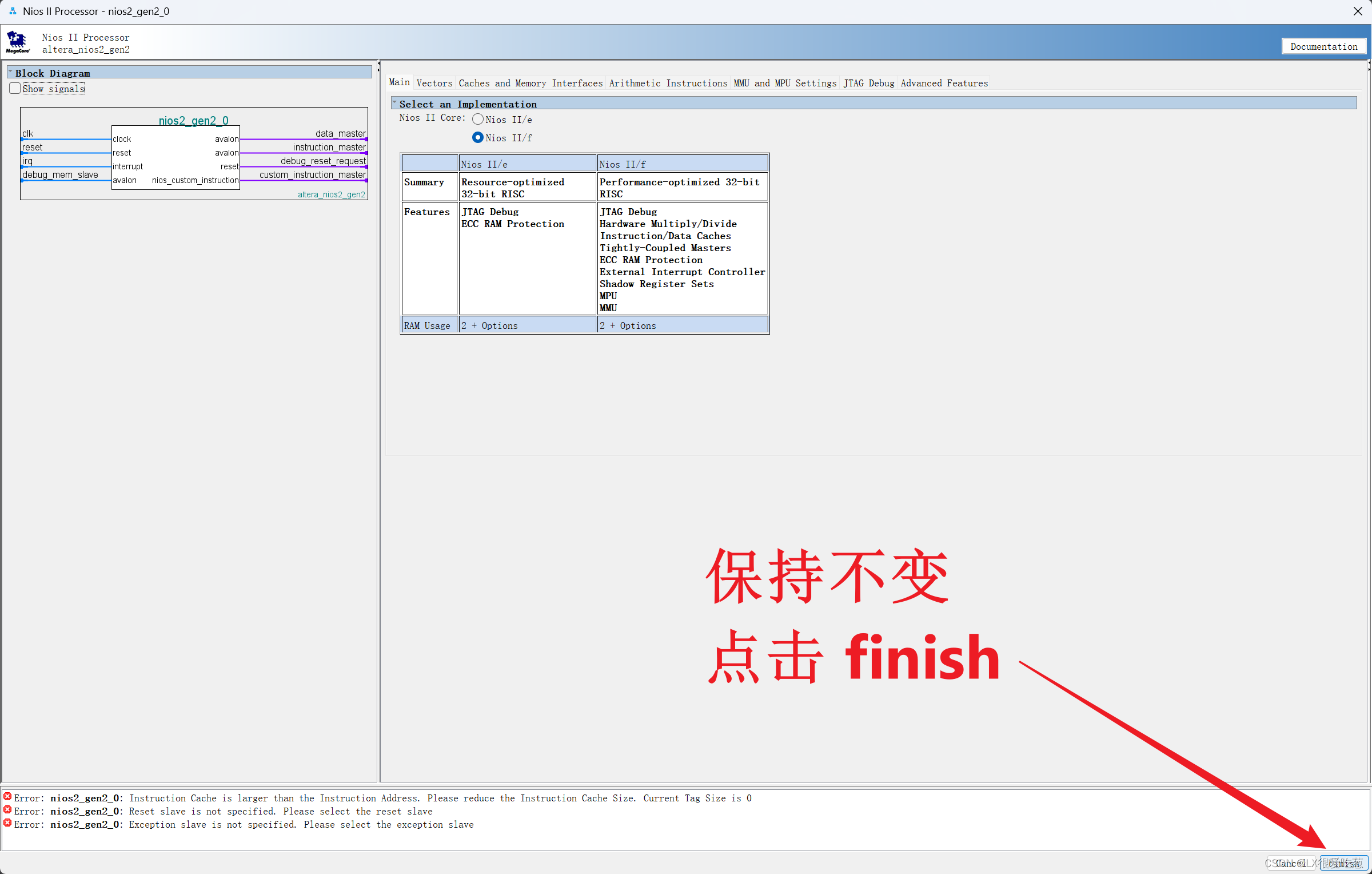

保持默认配置,选择Finish

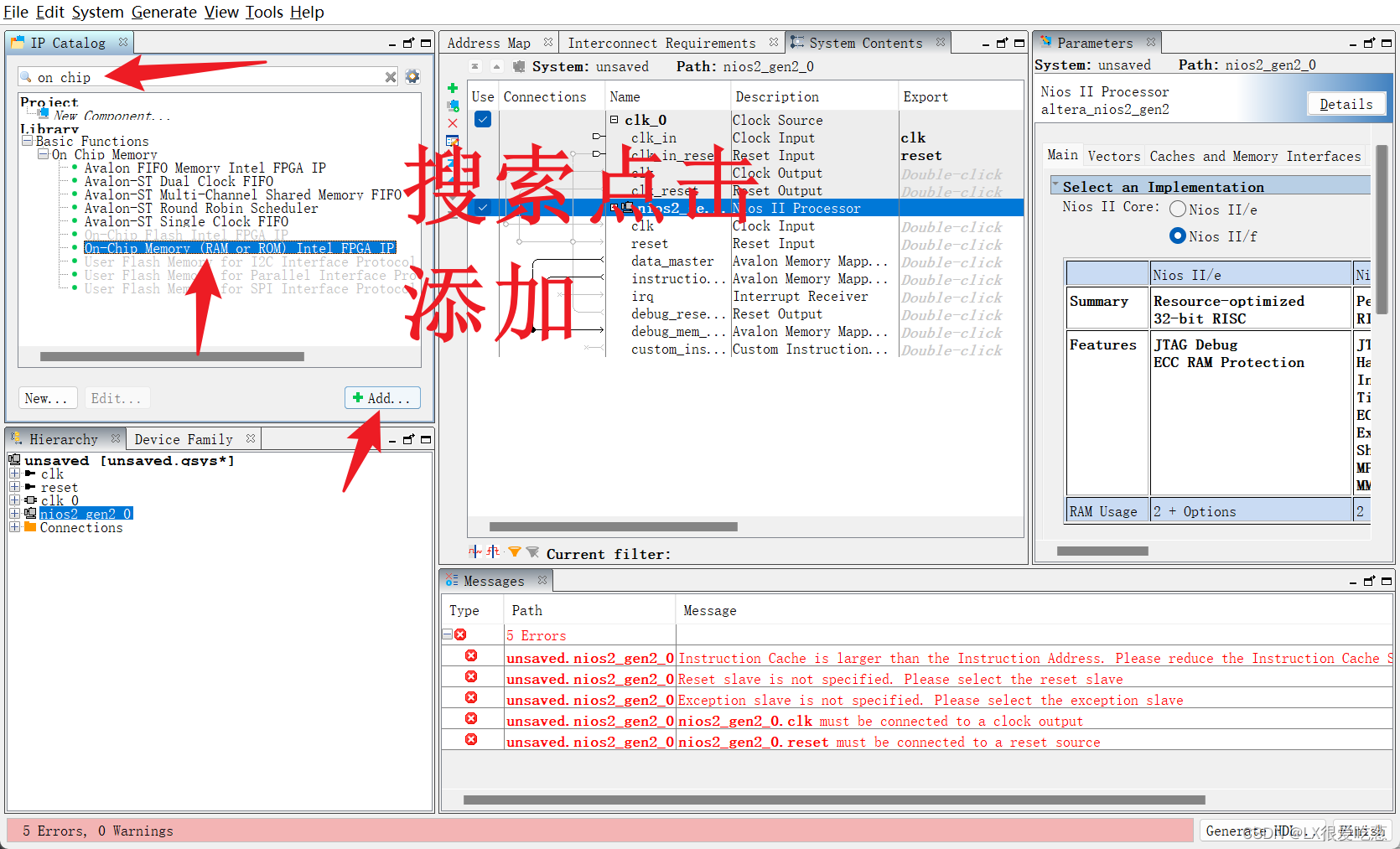

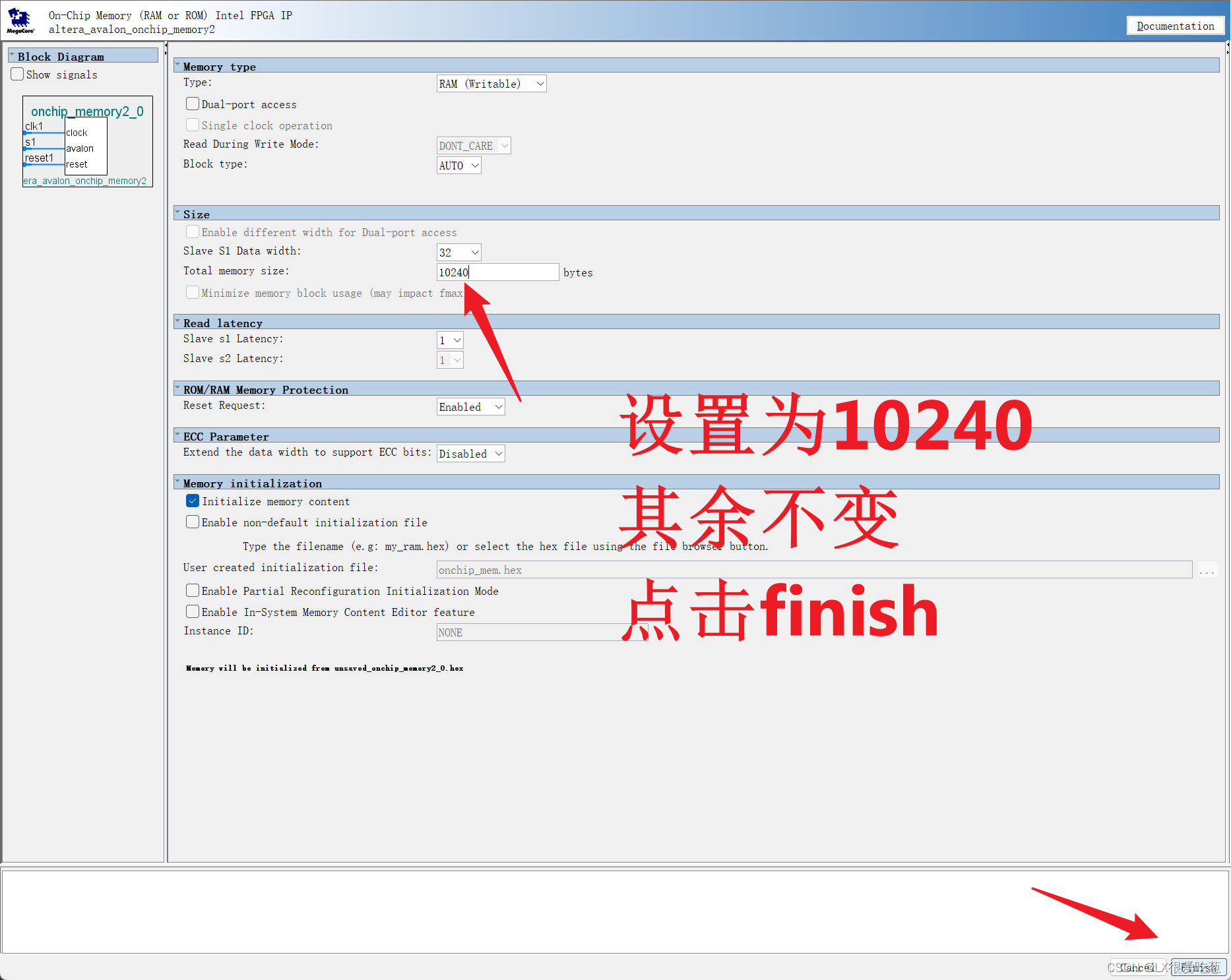

③On_Chip Memory的添加

在搜索框中,输入on_chip,找到On_Chip Memory,点击Add

设置大小为10K,其他保持默认设置

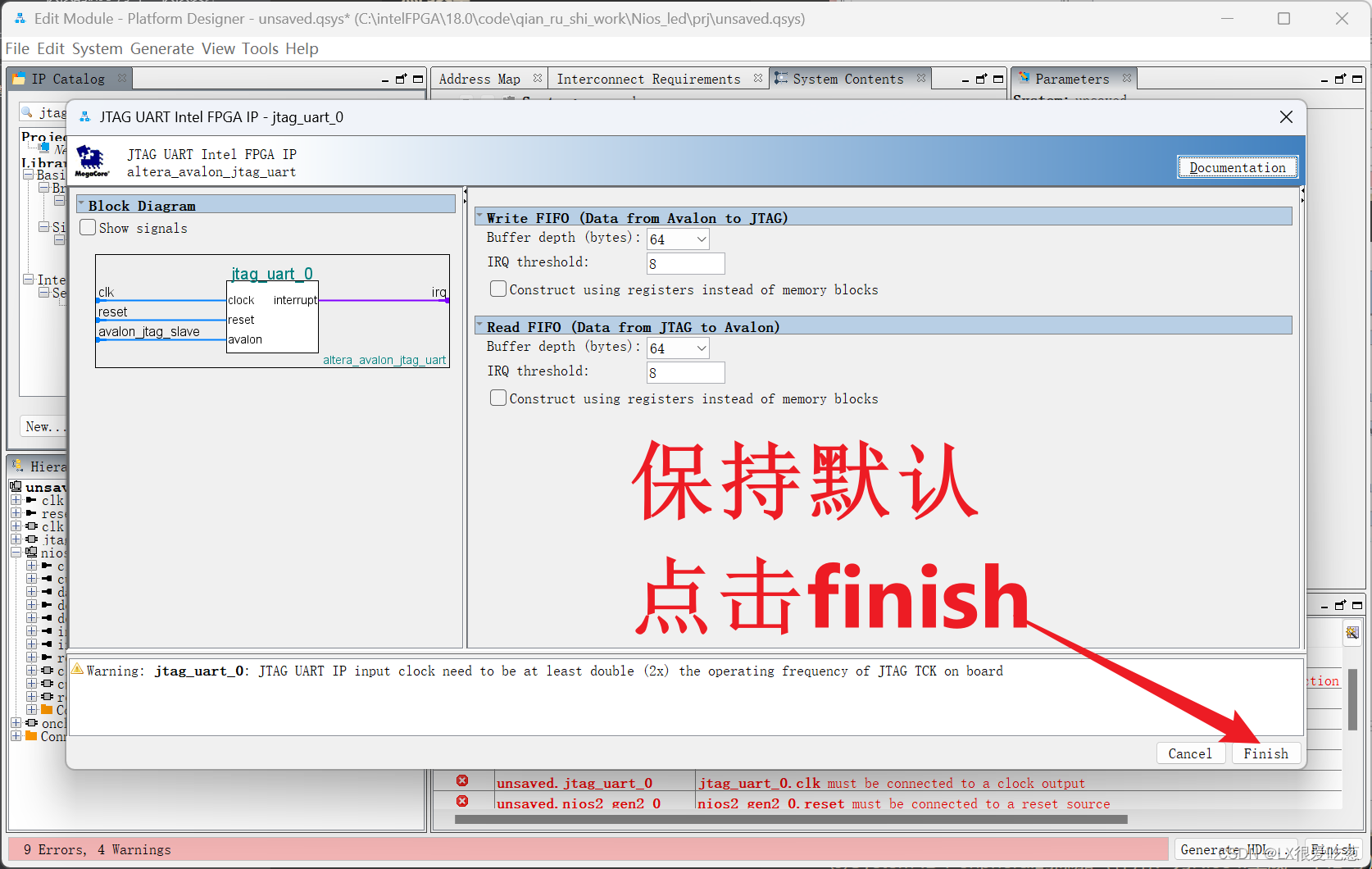

④JTAG UART的添加(作用:利用JTAG完成,URAT通信功能)

在搜索框中,输入jtag,找到JTAG UART,点击Add

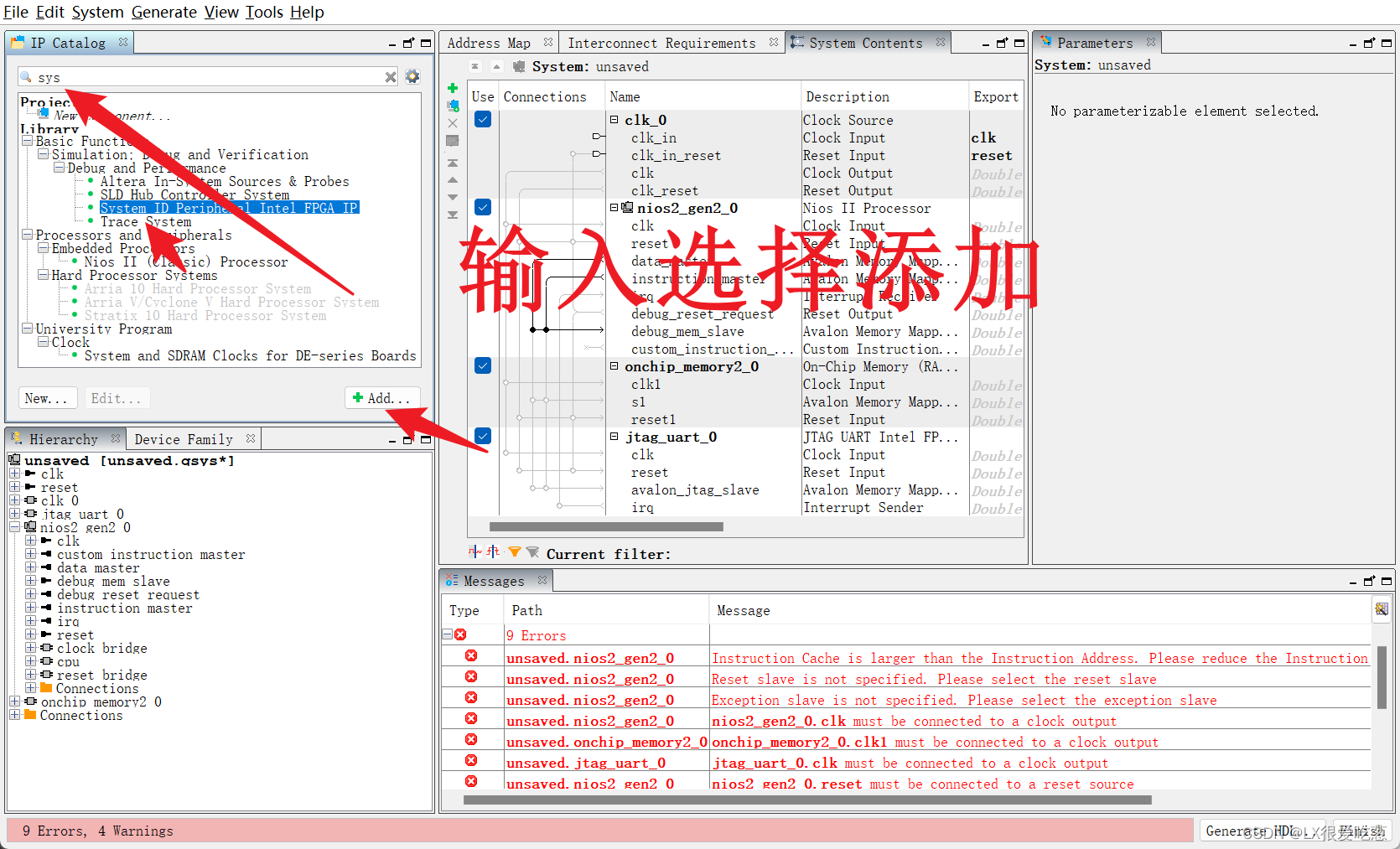

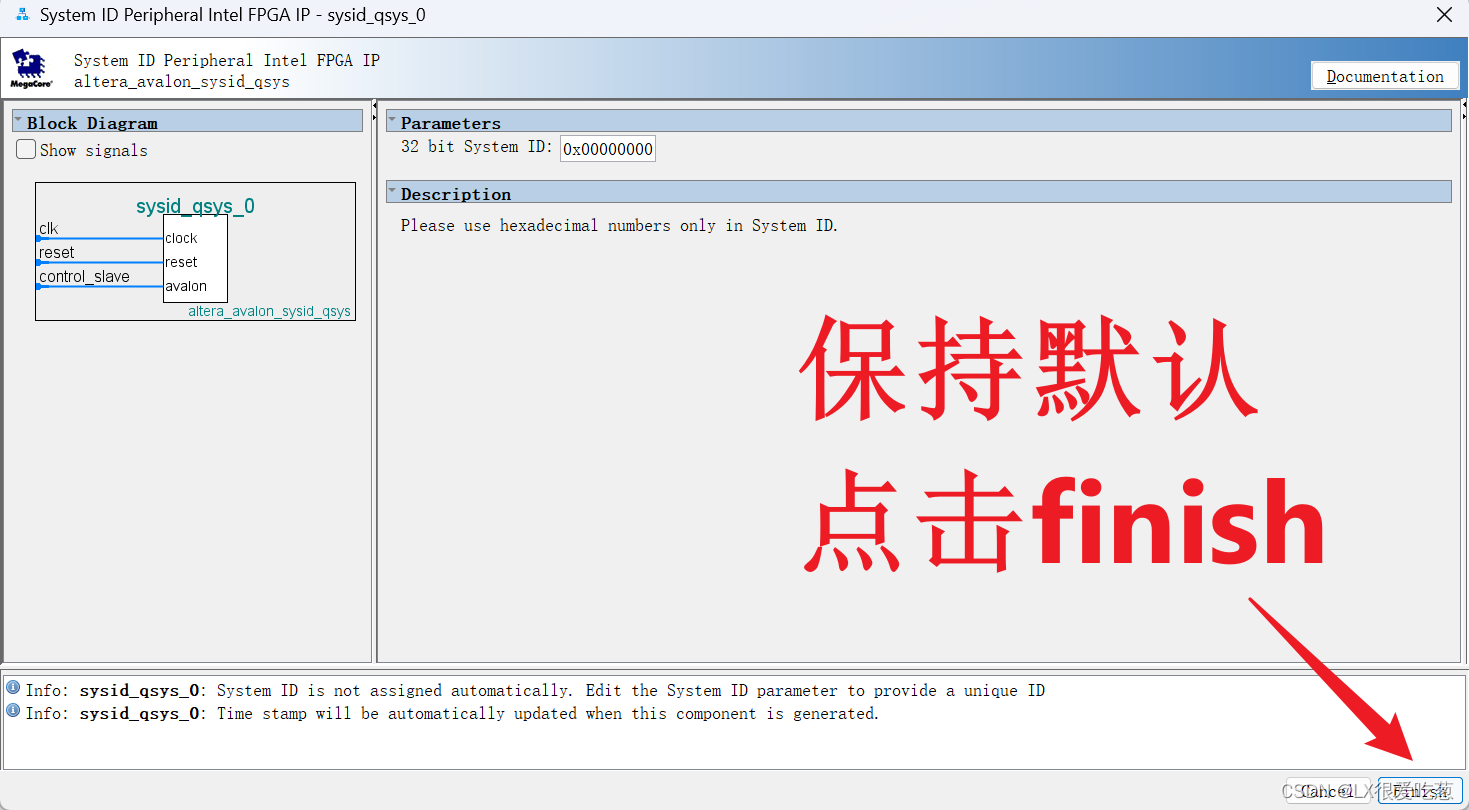

⑤System ID Peripheral的添加(作用:为Nios II生成一个ID号)

在搜索框中,输入sys,找到System ID Peripheral,点击Add

保持默认设置

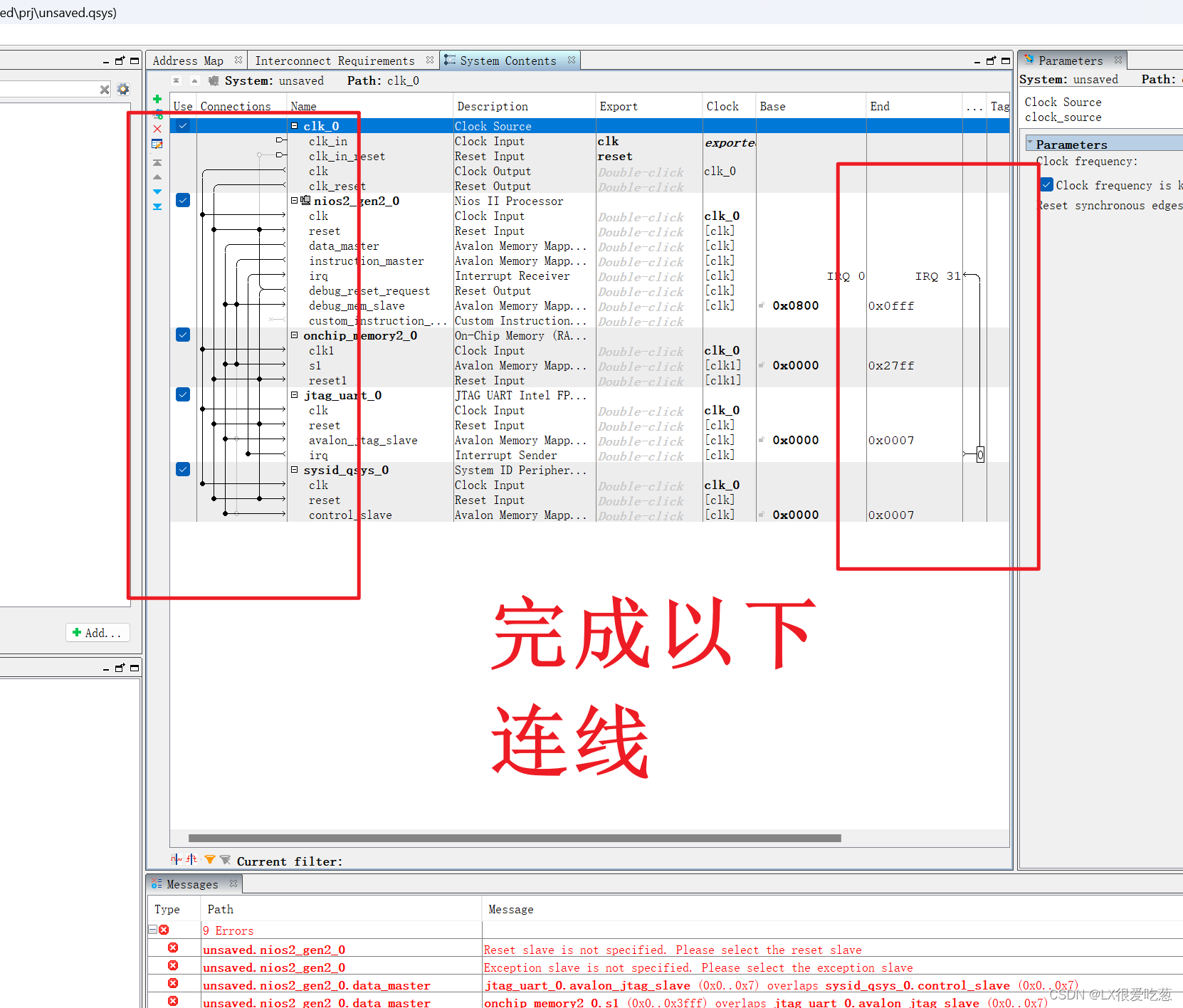

4.1.3 IP核的连接

clk,reset,datamaster需要和其他所有IP核连接,nios ii的指令端口(instruction_master)只与存储器进行连接,nios ii中的jtag_debug_model_reset与外部IP核进行连接 。jtag端口的中断信号的连接,其中0表示中断的优先级(可以进行设置)

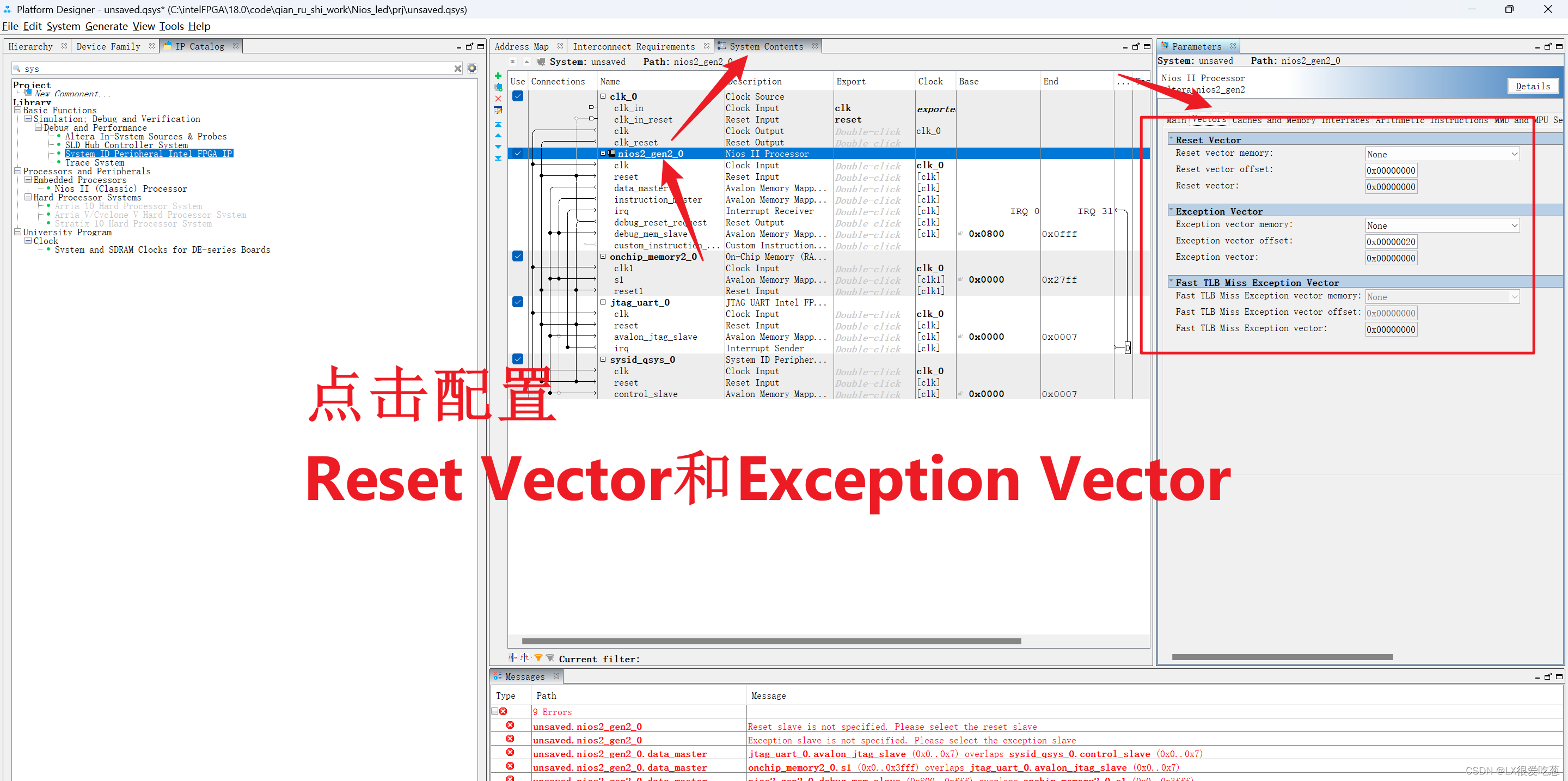

对Reset Vector和Exception Vector的设置

设置完成后,选择Finish

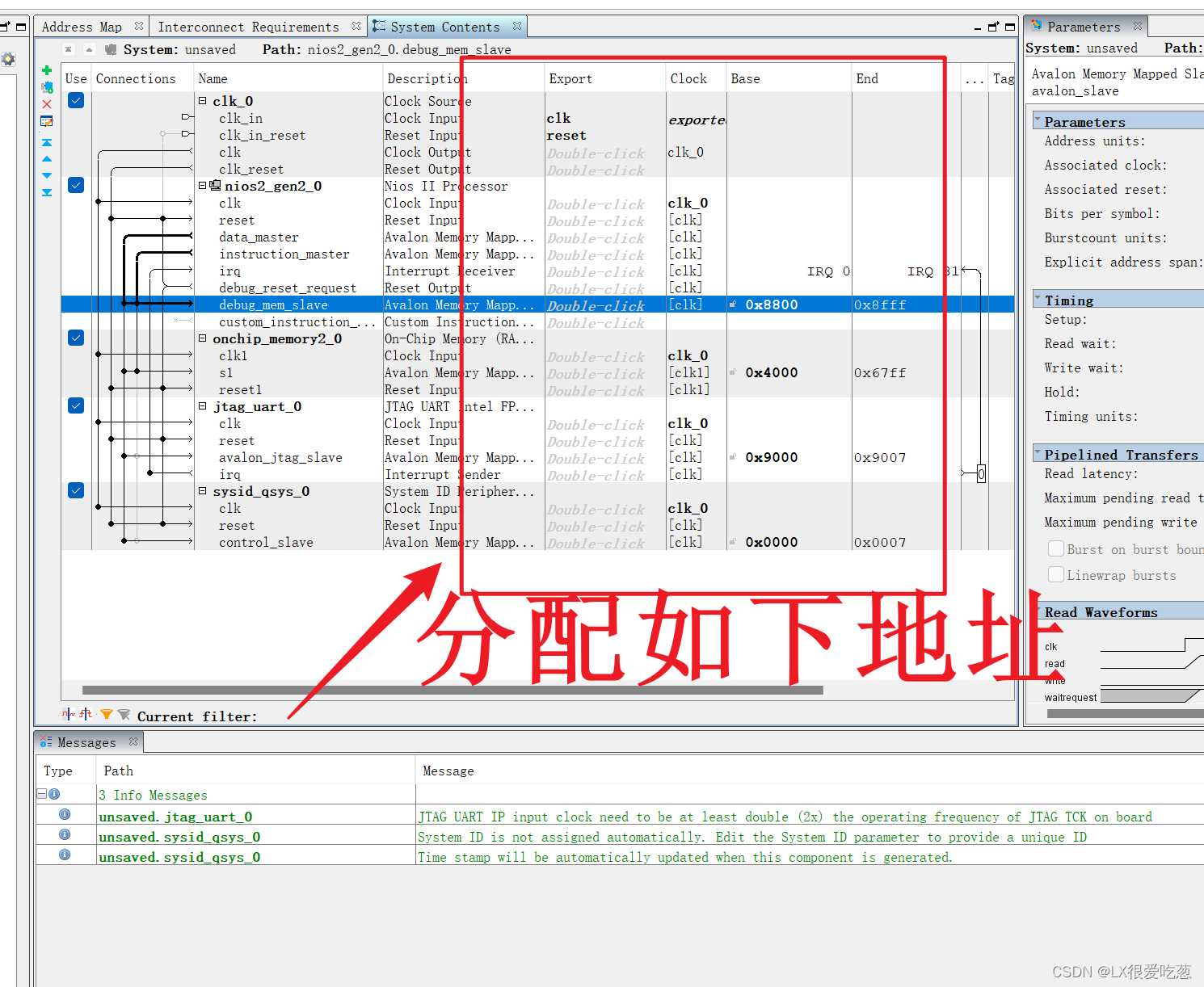

系统分配地址

选择System->Assign Base Address

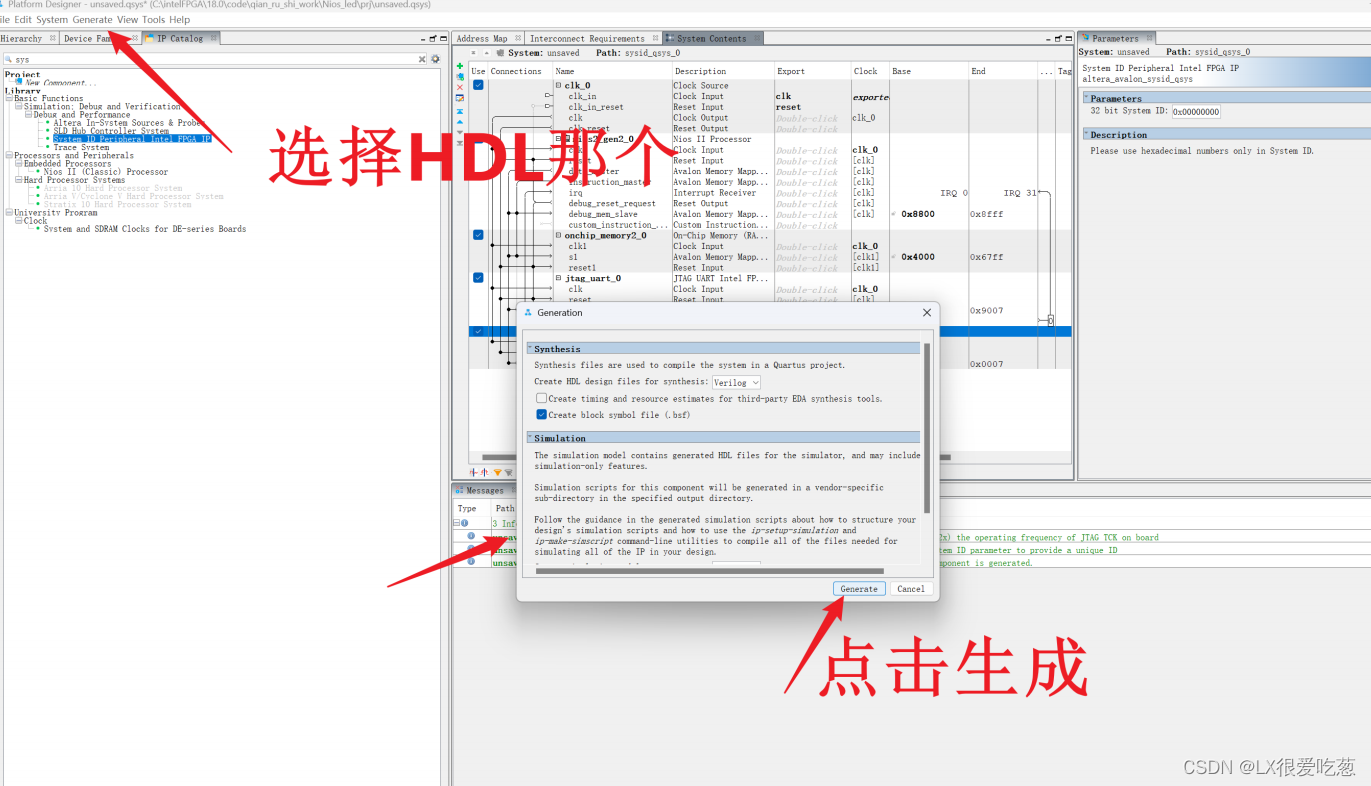

4.1.4使用FPGA资源

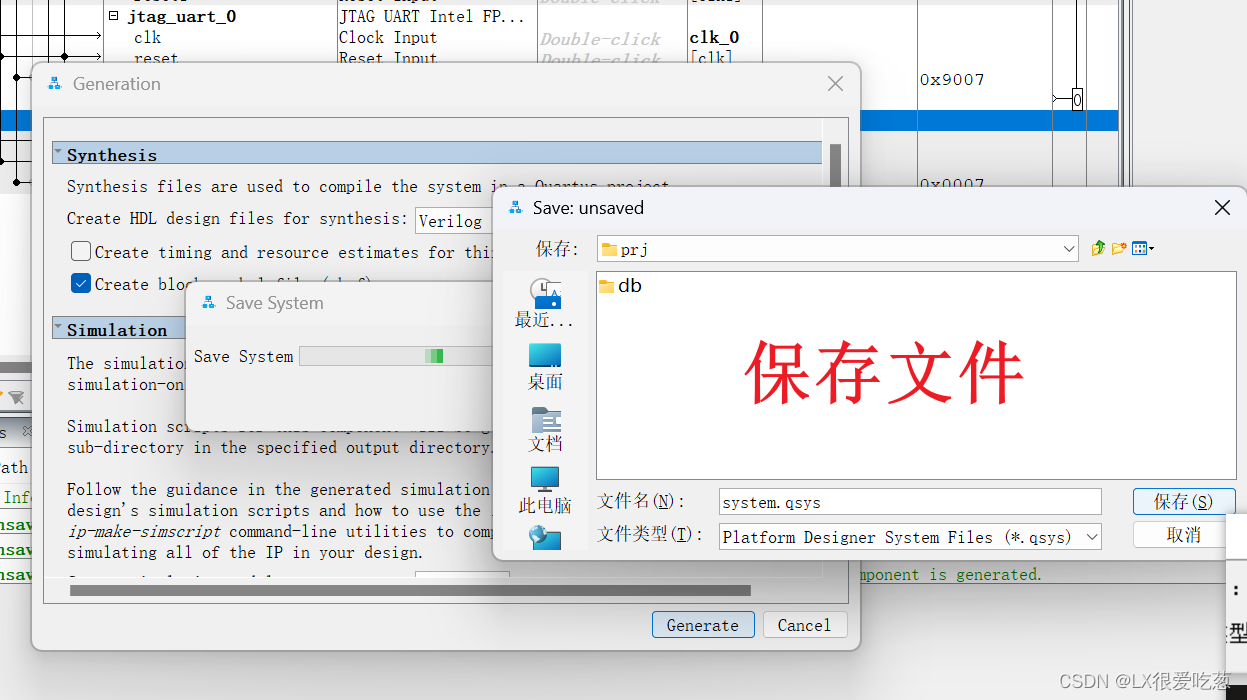

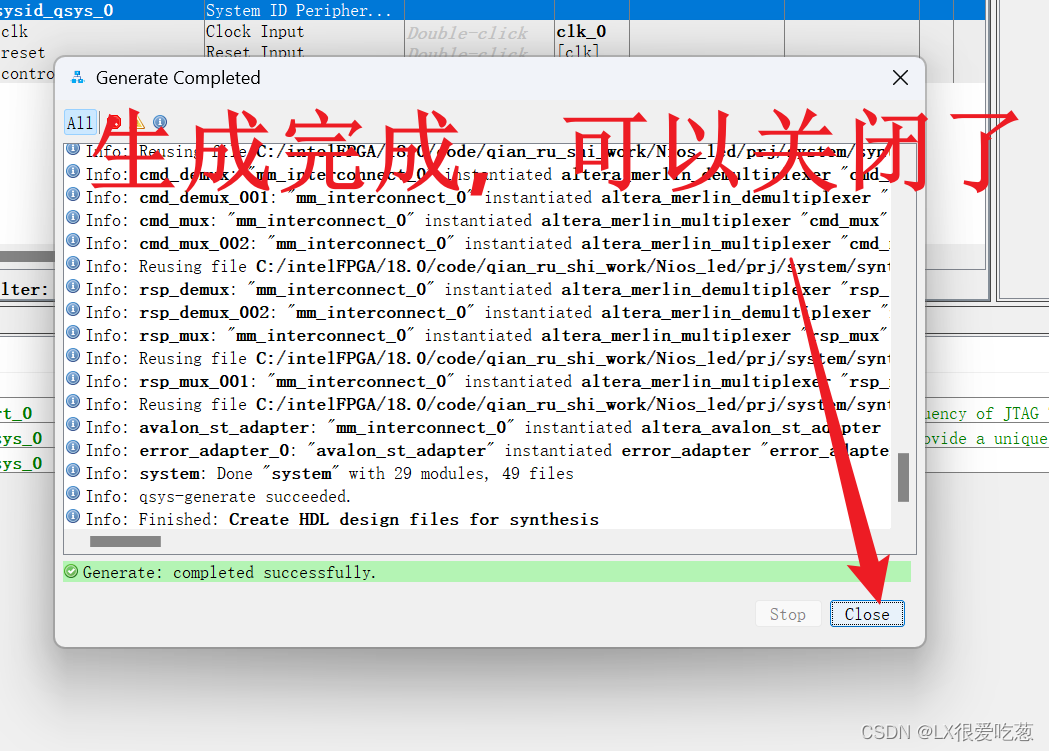

选择Generate->Generate,保持默认设置,点击Generate,选择Save

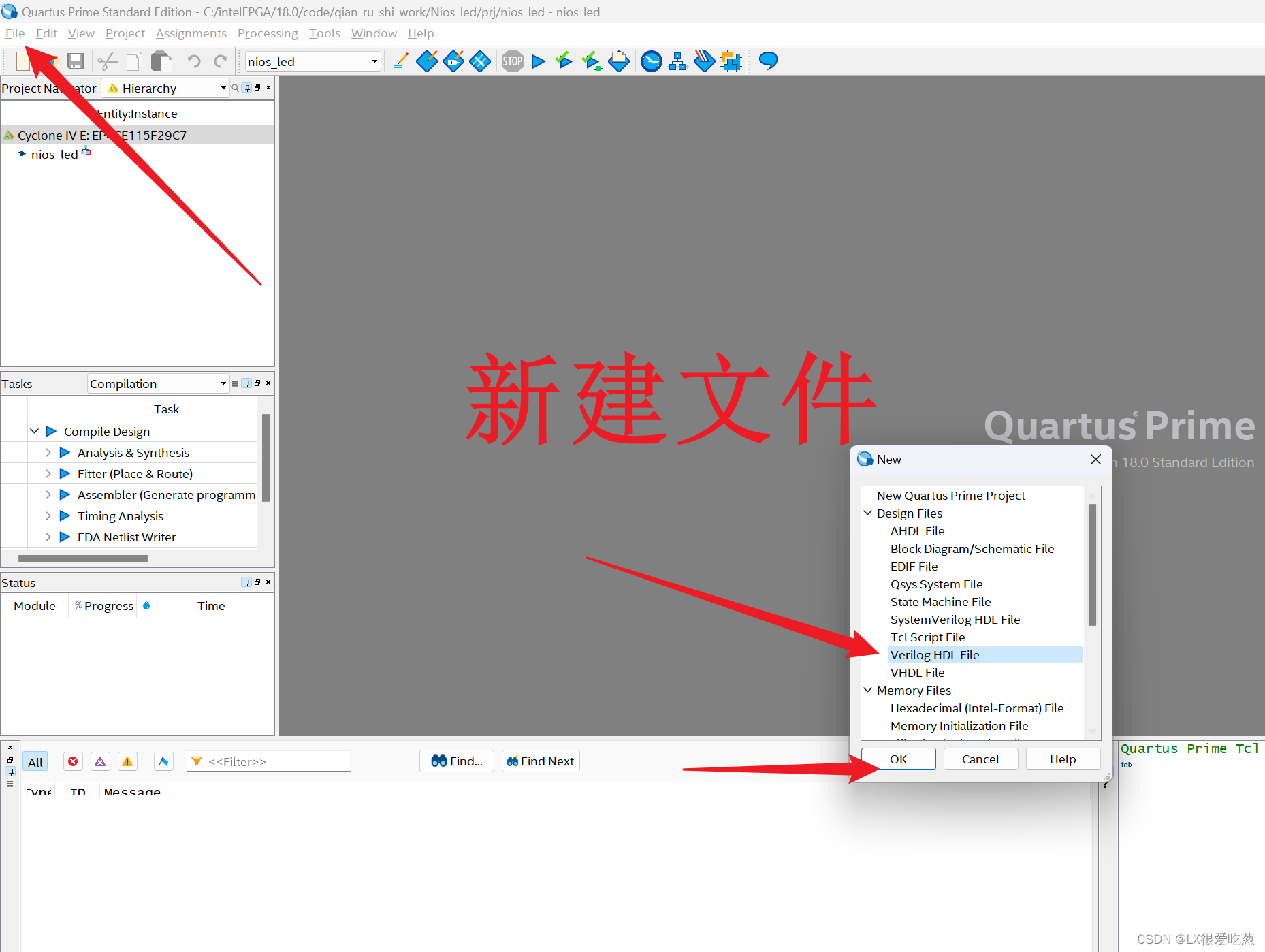

创建顶层文件

回到Quarters,选择New->Verilog HDL File

顶层文件内容

module hello_world(

input clk,

input reset_n

);

//此处的代码可以通过Qsys中的Generate->Generate Example,复制里面的内容,粘贴到此处,进行相应的修改

system u_qsys (

.clk_clk (clk), // clk.clk

.reset_reset_n (reset_n) // reset.reset_n

);

endmodule

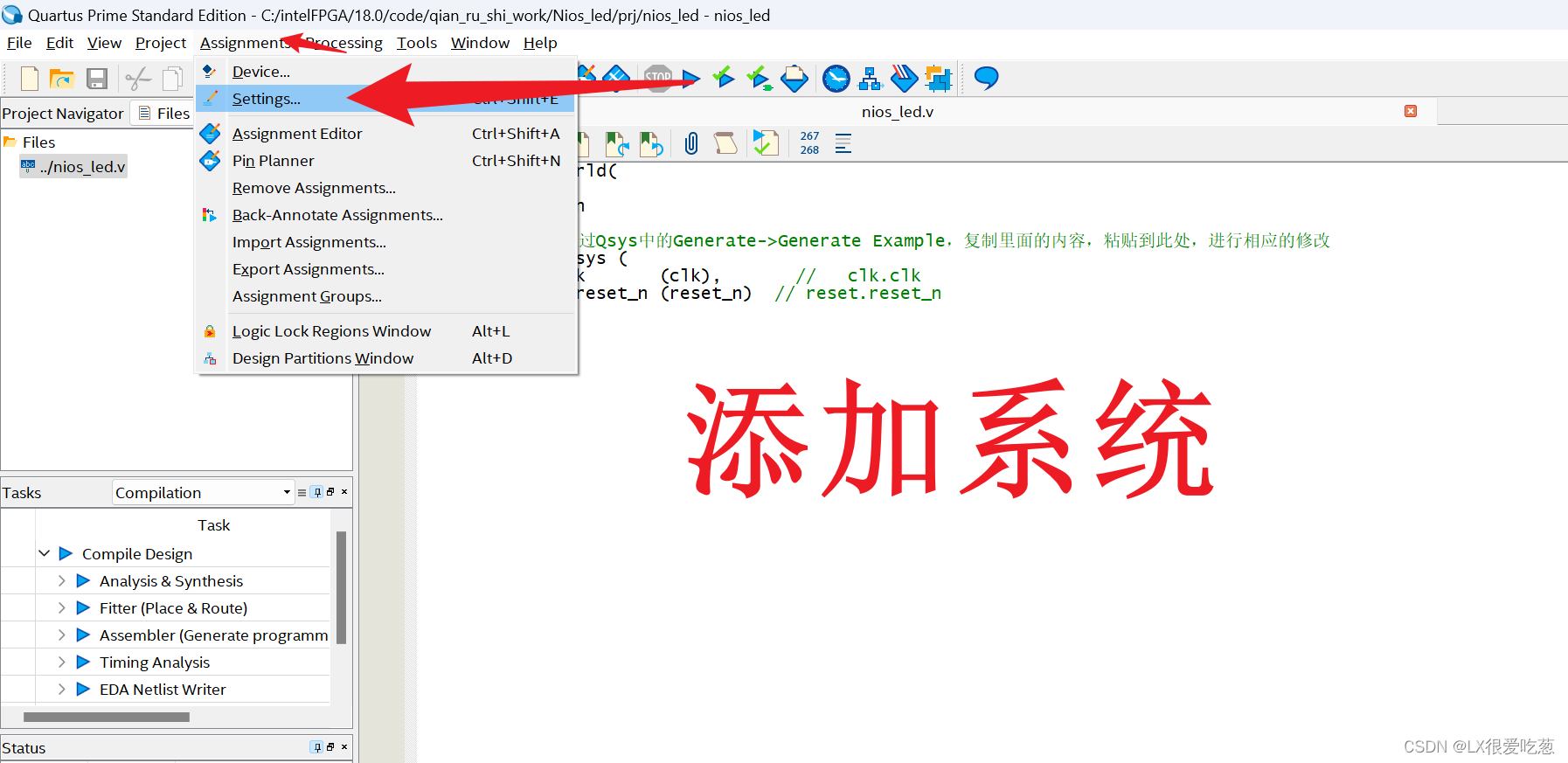

手动添加上面创建的系统

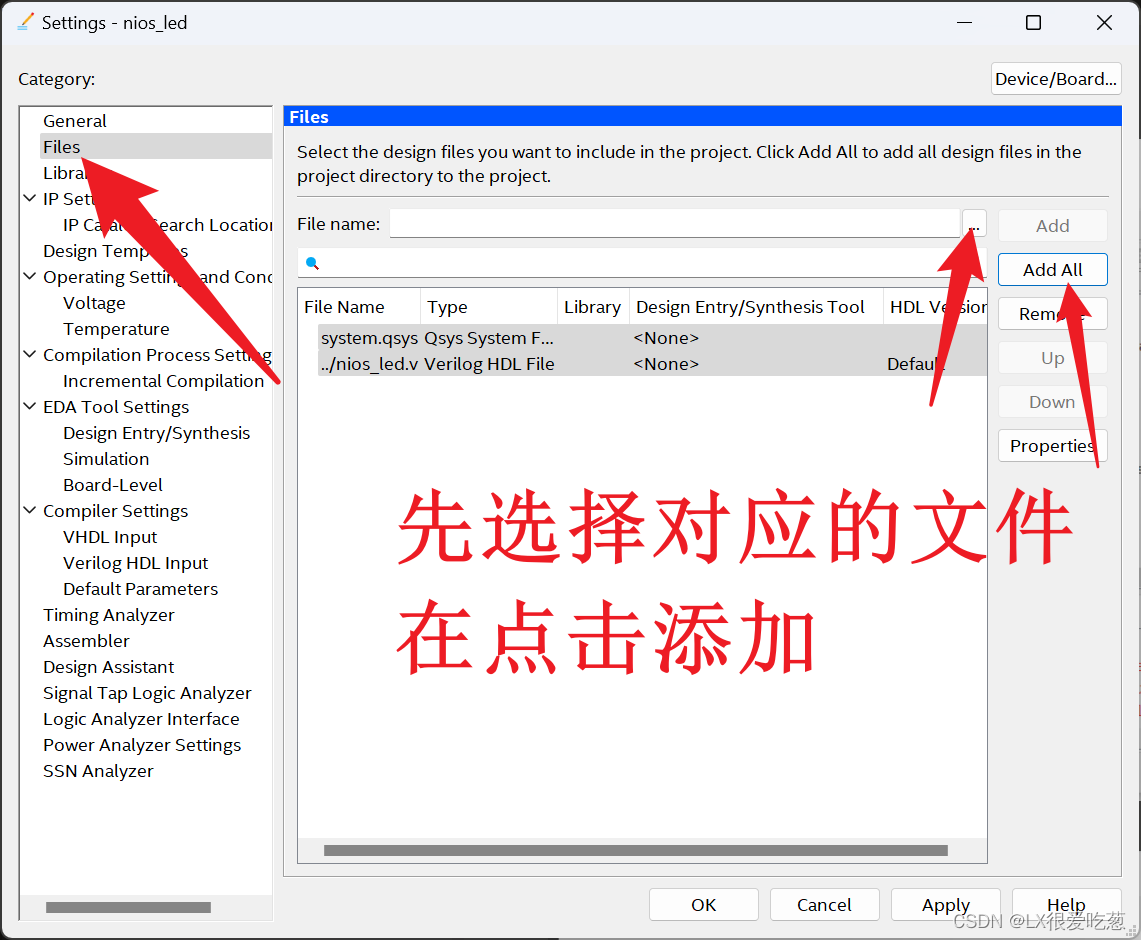

选择File->添加对应的文件->Add->Apply->关闭

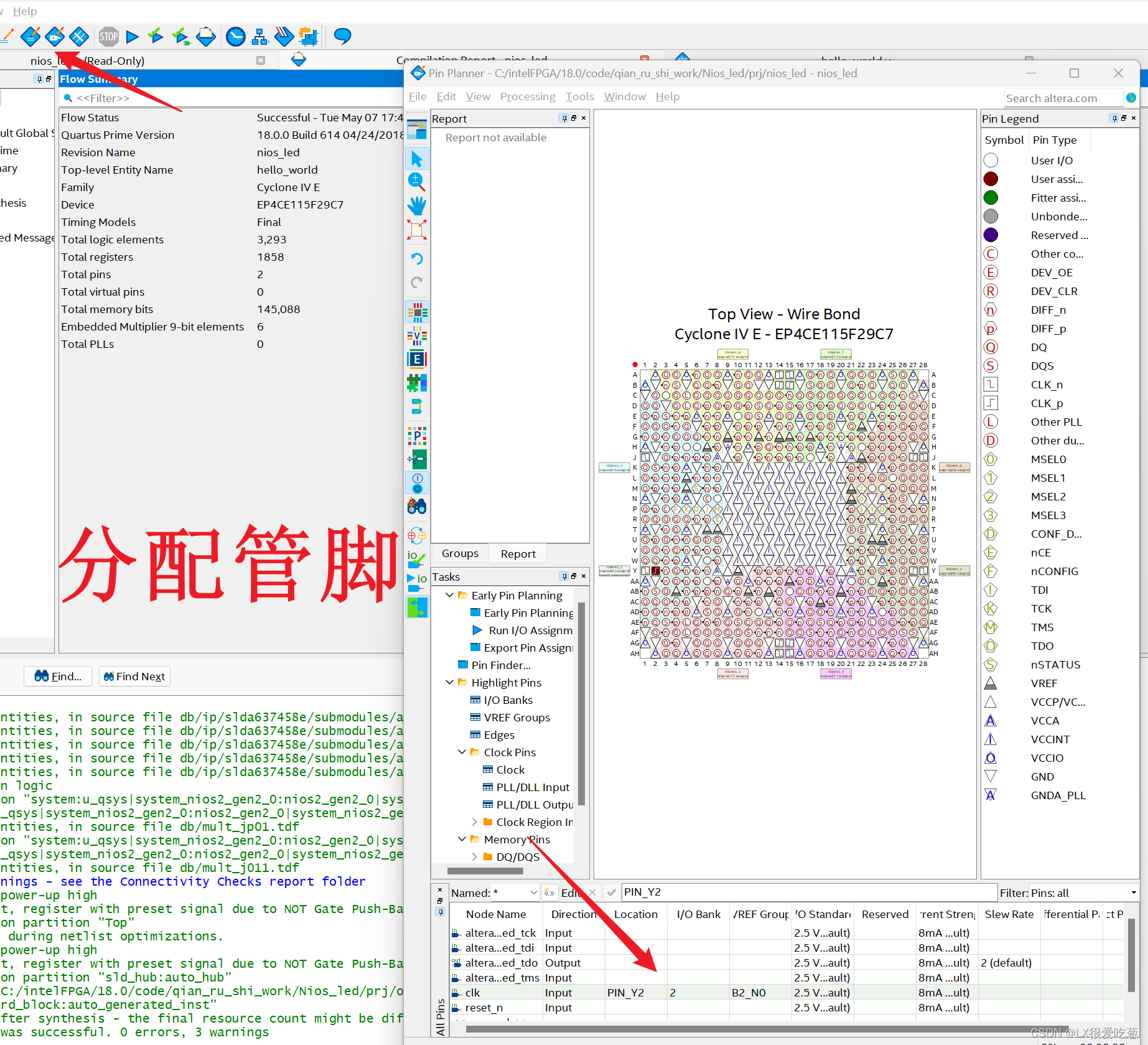

编译完成后,分配管脚

再次进行编译,成功后即可完成本阶段操作。

4. 2软件设计

4.2.1 打开软件

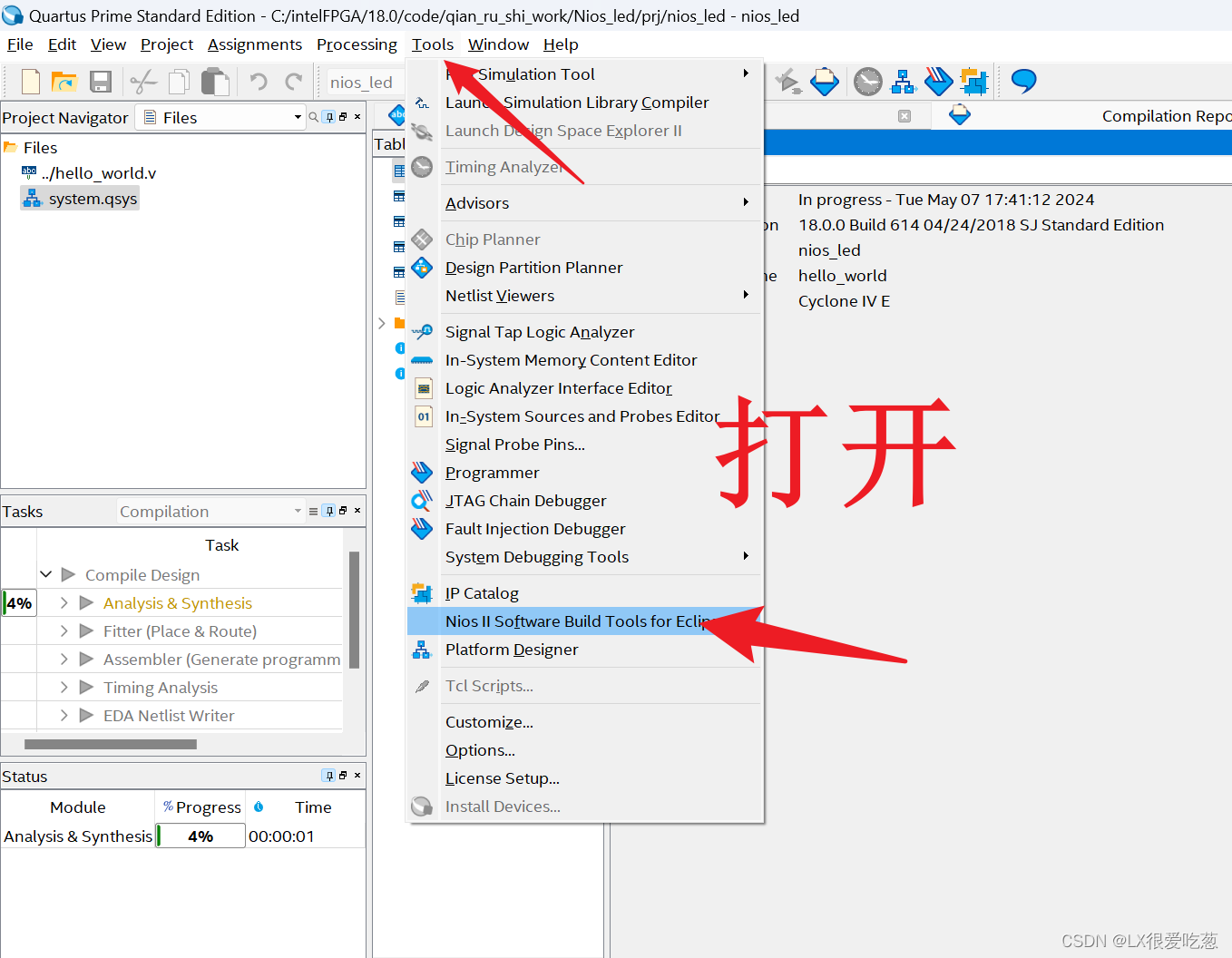

打开Nios II Software Build Tools for Eclipse

4.2.1 创建文件

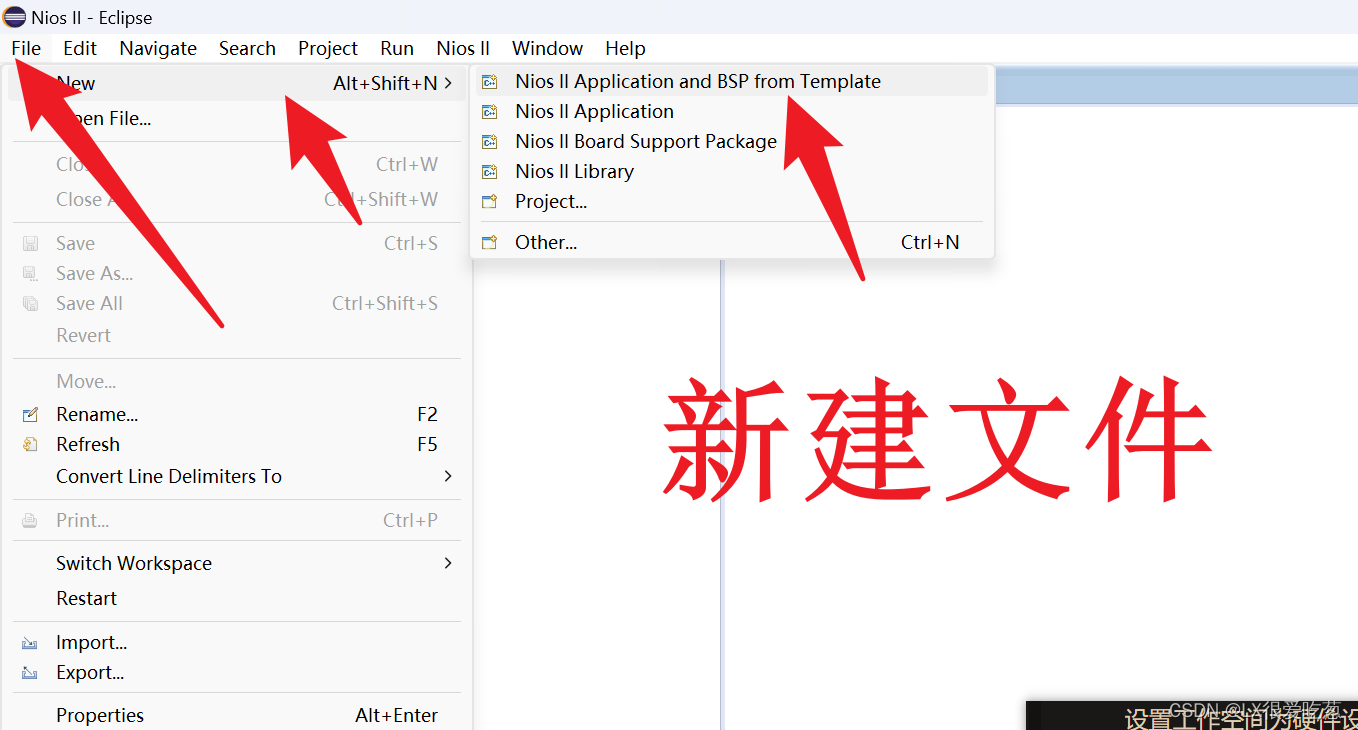

点击File->New->Nios II Application and BSP from Template

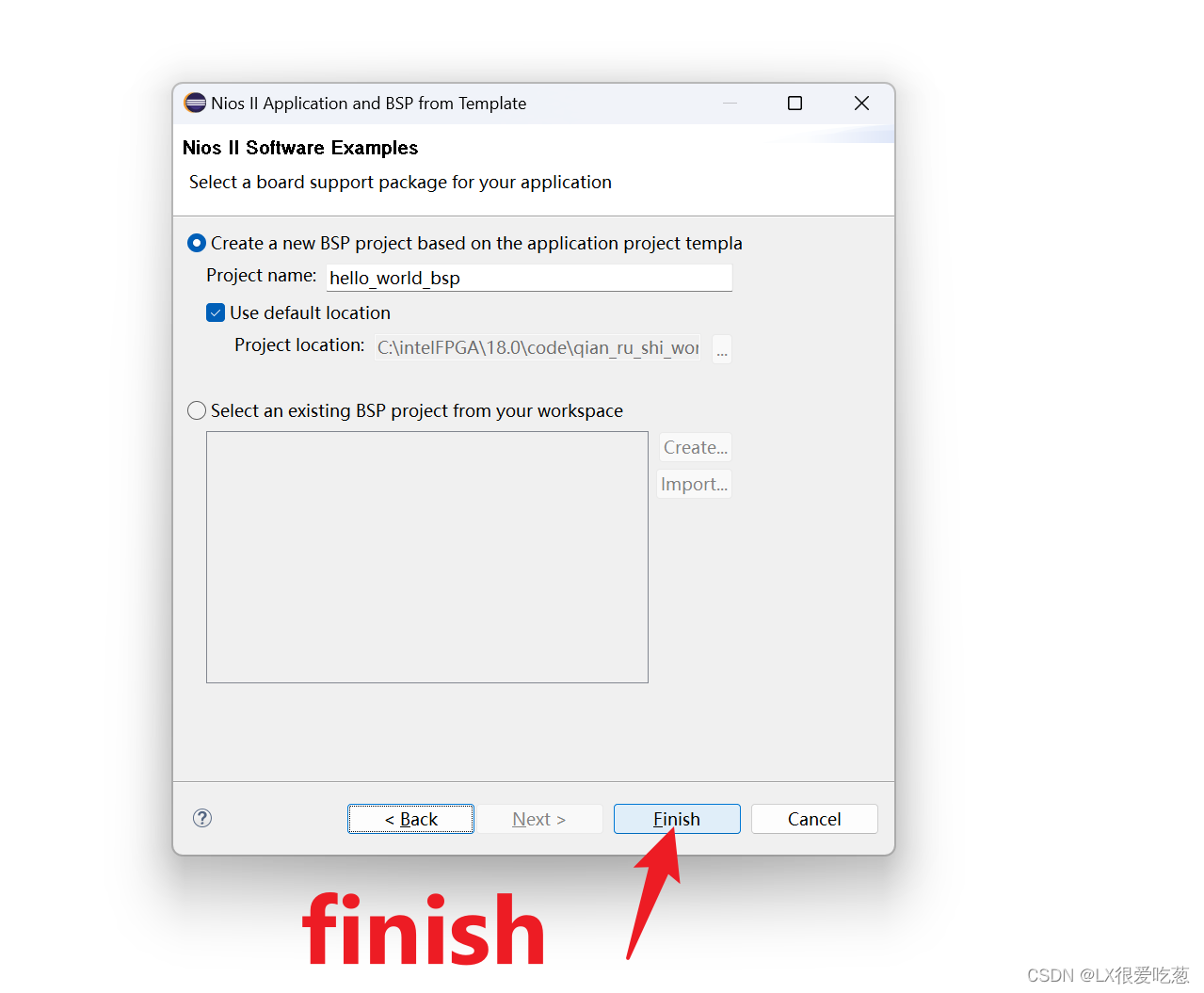

选择硬件设计部分的文件,填写工程名称以及工程Template

4.2.3 修改实现代码

打开hello_world中的.c文件

修改里面的内容如下

流水灯

#include "system.h"

#include "altera_avalon_pio_regs.h"

#include "alt_types.h"

const alt_u8

led_data[8]={0x01,0x03,0x07,0x0F,0x1F,0x3F,0x7F,0xFF};

int main (void)

{

int count=0;

alt_u8 led;

volatile int i;

while (1)

{ if (count==7)

{count=0;}

else

{count++;}

led=led_data[count];

IOWR_ALTERA_AVALON_PIO_DATA(PIO_LED_BASE, led);

i = 0;

while (i<500000)

i++;

}

return 0;

}

串口输出

#include "system.h"

int main (void)

{

volatile int i;

while (1)

{

printf("Hello from Nios II! 你干嘛,哎哟~~~ \n");

i = 0;

while (i<5000000)

i++;

}

return 0;

}

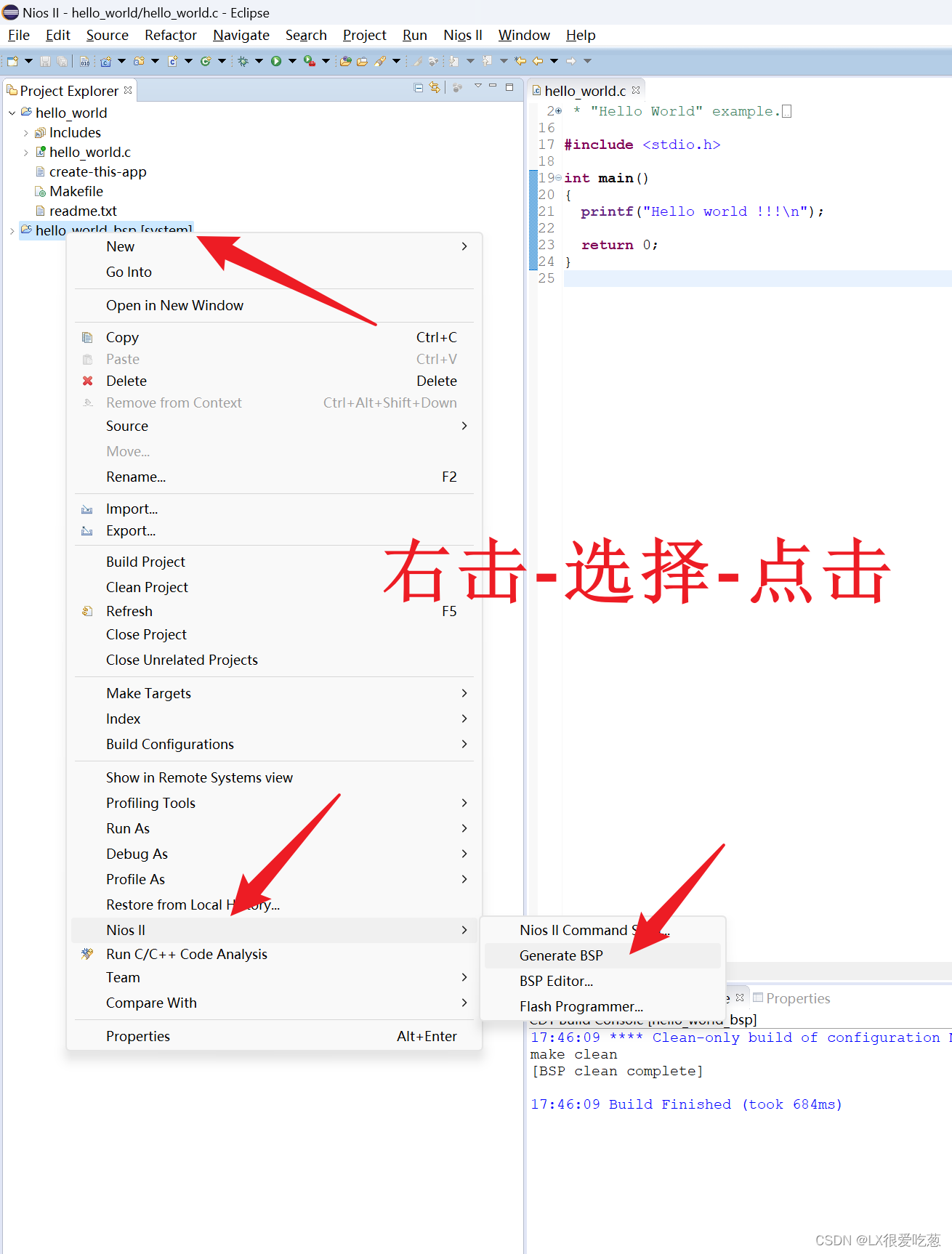

点击保存,选择hello_wold_bsp,右键后,选择Nios II中的Generate BSP

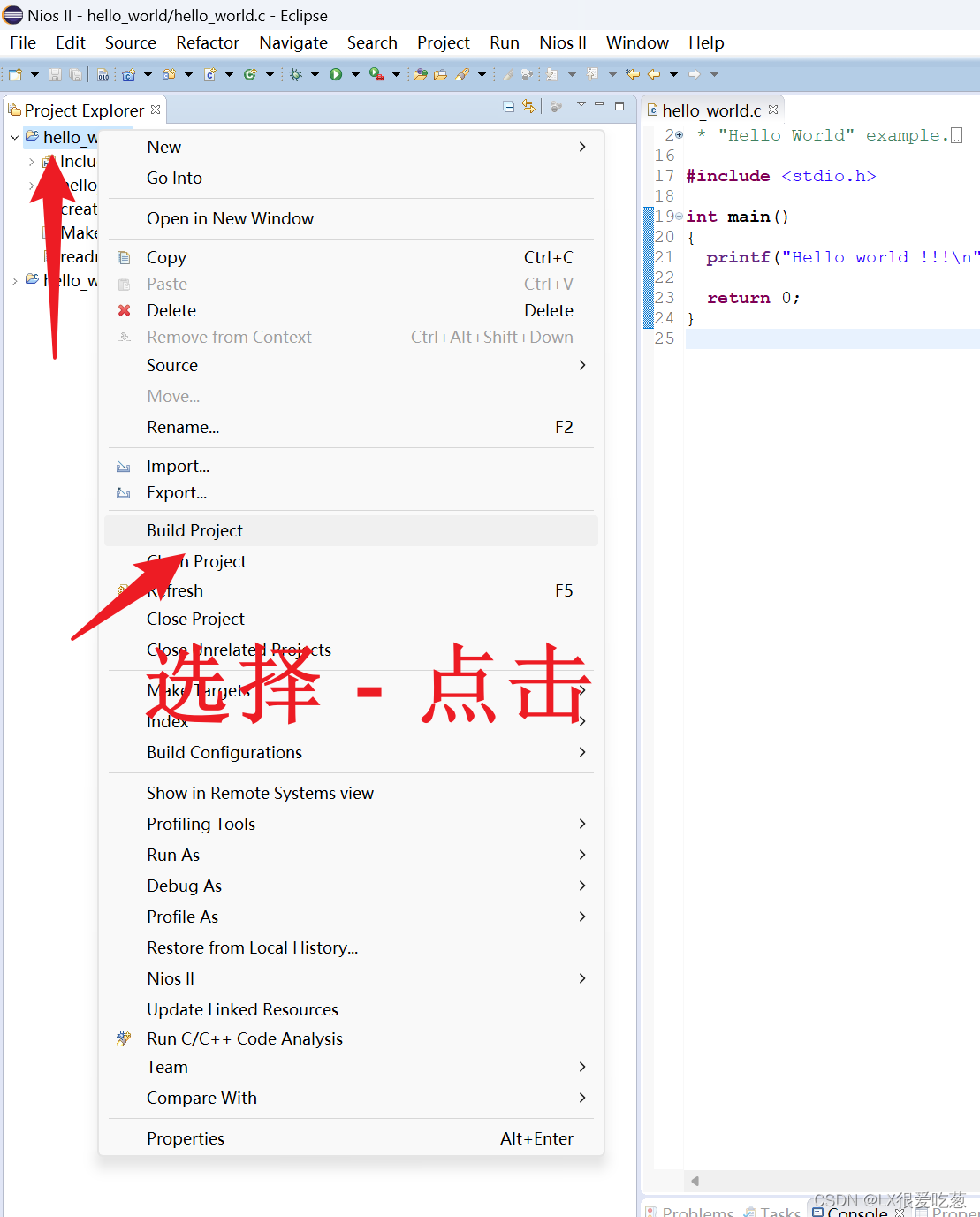

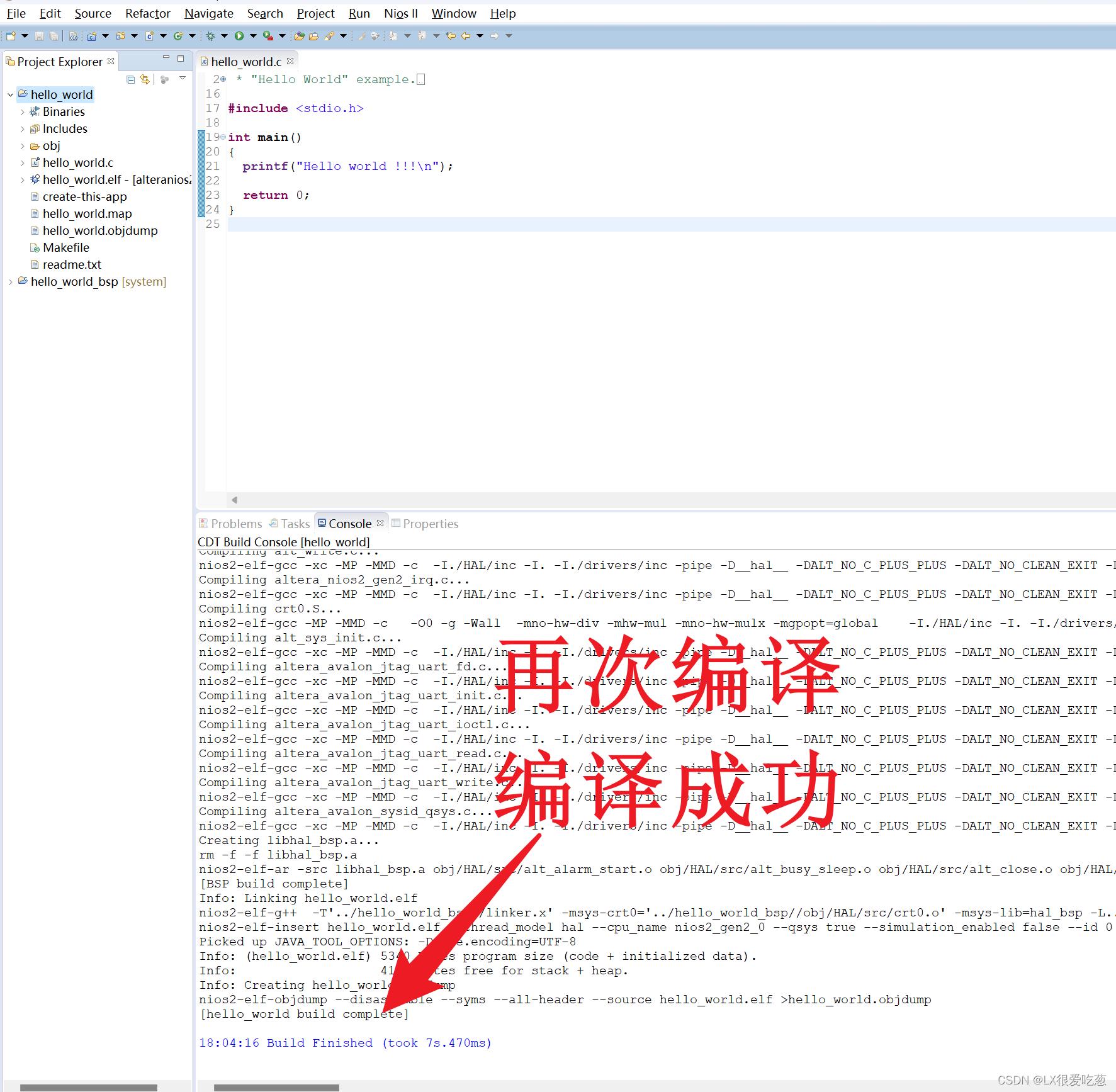

再次编译

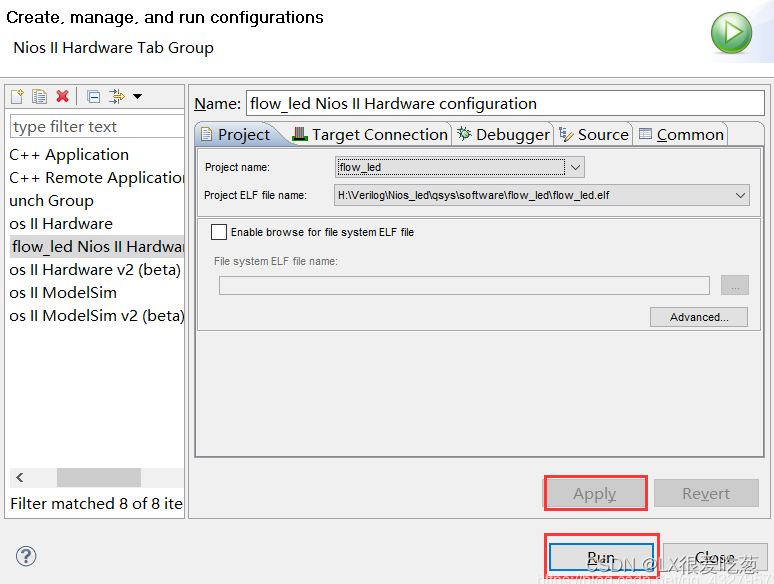

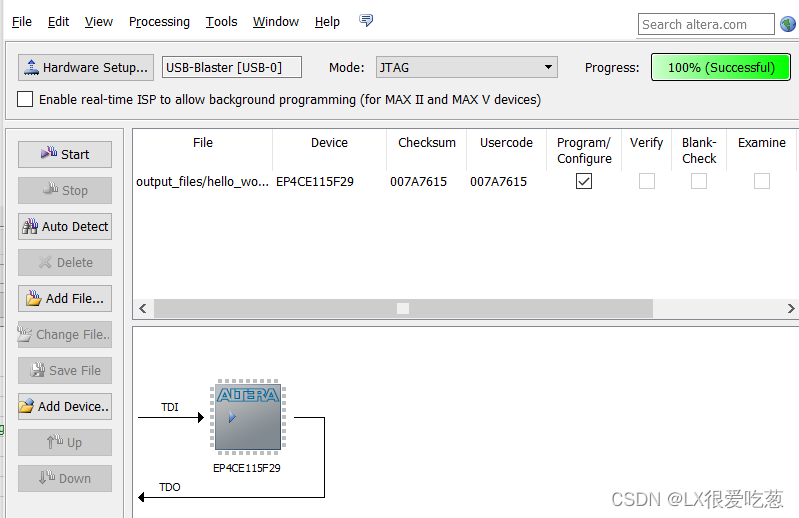

4.2.4 代码烧录

五、实验效果

1.流水灯

流水灯

2.串口输出字符

串口

六、实验心得

经过本次实验,我成功设计并实现了基于Nios II软核的FPGA流水灯控制和串口数据输出模块。这一过程不仅加深了我对Nios II软核处理器及其与硬件描述语言结合应用的理解,也锻炼了我的编程能力和硬件调试技巧。

实验过程回顾:

- Nios II软核与Qsys系统设计: 我首先利用Qsys工具,将Nios II软核与所需的外围设备进行集成,创建了一个定制化的系统。通过这一步骤,我学习了如何在系统级别上进行设计,并对Nios II软核的可配置性有了更深入的认识。

- 流水灯控制逻辑实现: 我编写了C代码来控制FPGA上的LED灯,实现了流水灯效果。这一过程中,我练习了基本的输入输出操作和时间控制逻辑,理解了如何通过软件控制硬件行为。

- 串口通信编程与实现: 我实现了一个波特率发生器,并编写了用于串口数据发送的状态机逻辑。通过实例化

uart_tx模块,我掌握了串口信号的输出控制,包括数据位的串行化和波特率的匹配。 - 硬件与软件的协同调试: 在整个实验过程中,我不断在硬件描述语言的硬件实现与Nios II软件编程之间进行切换和调试,这一经历极大地提升了我的综合设计能力。

实验成果:

通过本次实验,我不仅掌握了Nios II软核处理器的编程技巧,还学会了如何将理论知识应用到实际的硬件设计中。我能够独立完成从设计、仿真到硬件测试的整个FPGA设计流程,并且能够通过外部串口工具接收发送的数据。

实验反思:

在实验过程中,我遇到了一些挑战,包括数据时序的准确性以及串口通信的调试。通过不断测试和调整,我学会了如何对FPGA设计进行调试,解决可能出现的问题。这一过程锻炼了我的问题解决能力,也增强了我面对复杂问题时的耐心和信心。

未来展望:

尽管本次实验已经完成,但我意识到在FPGA设计和嵌入式系统开发方面还有许多值得学习和探索的地方。未来,我计划深入学习更高级的FPGA设计技术,探索更多的通信协议和接口,并将这些技术应用到更大型的项目中。

感谢与致谢:

最后,我要感谢所有在本次实验中提供帮助和支持的同学和老师,以及那些提供友情链接和资源的朋友们。是你们的帮助让这次学习之旅更加丰富和有趣。

最后感谢大佬友情链接:

2868

2868

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?