本原创文章由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处(www.meyesemi.com)

一:开发系统介绍

开发系统概述

MES2L676-100HP开发板采用紫光创 logos2系列 FPGA,型号:PG2L100H-6FBB676。开发板采用核心板+扩展板结构,核心板与扩展板之间使用高速板对板连接器进行连接,核 心 板 侧 连 接 器 型 号 : LB3524-G120P-WOR , 扩 展 板 侧 连 接 器 型 号 :LB3524-G120S-WOR。

核心板主要由FPGA+2 颗DDR3+2 颗 FLASH+电源及复位电路组成,承担了FPGA最小系统运行及高速数据处理及存储功能。FPGA选用紫光同创28nm工艺FPGA(logos2:PG2L100H-6FBB676);PG2L100H 与 DDR3 在数据交互时时钟频率最高可达1066Mbps,两颗DDR3 数据位宽共32bit,因此数据带宽可达(1066Mbps*32),充分满足高速多路数据存储的需求;另外 PG2L100H FPGA 带有8路HSST高速收发器,每路速度高达6.6Gbps,非常适用于光纤通信与 PCIe 通信;核心板上的两颗 FLASH 主要用于存储 FPGA配置文件 。

底板为核心板扩展了丰富的外围接口,其中包括 HDMI 输出接口、HDMI 输入接口、网口、串口,SD卡接口、光纤模块接口,SMA_HSST 接口、PCIe 接口,并配置了按键、LED 灯、EEPROM 器件。

二:开发系统简介

开发系统外设资源

HDMI 输出接口 *1

光纤接口 *2

SD 卡接口 *1

SMA_HSST 接口 *1

用户按键 *5

USB 转 UART *1

HDMI 输入接口 *1

PCIe 接口 *1

10/100/1000M 以太网接口 *1

Jtag 调试接口 *1

LED 灯 *8

FMC 扩展口 *1

开发系统功能框图

MES2L676-100HP 开发平台所能实现的功能描述如下:

Logos2 FPGA 核心板

由 PG2L100H-6IFBB676+2 片 512MB DDR3 + 2 片 128Mb QSPI FLASH 组成。

10/100M/1000M 以太网 RJ-45 接口 *1

网口 PHY 芯片采用 RTL8211F,RTL8211F 支持 10/100M/1000Mbps 网络传输数据率;支持全双工工作模式及数据率自适应。

PCIe X4 接口 * 1

支持 PCI Express 2.0 标准,提供 PCIe X4 高速数据传输接口,单通道通信速率可高达5GTbps。

SFP 高速光纤接口 * 2

Logos2 FPGA 的 HSST 收发器的 2 路高速收发器连接到 2 个光模块的发送和接收,实现 2 路高速的光纤通信接口。每路的光纤数据通信接收和发送的速度高达 6.6Gb/s。

SMA_HSST 接口 * 1

Logos2 FPGA 的 HSST 收发器的 1 路高速收发器连接到 SMA 接口,数据通信接收和发送的速度高达 3.125Gb/s。

HDMI 输出 * 1

选用了国产宏晶微公司的 MS7210 HDMI 发送芯片,兼容 HDMI1.4b 及 HDMI 1.4b下标准视频的 3D 传输格式。支持的最高分辨率高达 4K@30Hz,最高采样率达到 300MHz;支持 HBR 音频。

HDMI 输入 * 1

选用了国产宏晶微公司的 MS7200 HDMI 接收芯片,兼容 HDMI1.4b 及 HDMI 1.4b下标准视频的 3D 传输格式。支持的最高分辨率高达 4K@30Hz,最高采样率达到 300MHz;支持 HBR 音频。

USB 转串口 * 1

用于与电脑进行串口通信,方便用户进行调试。串口芯片采用 Silicon Labs 的USB-UART 芯片: CP2102 , USB 接口采用 USB Type C 接口。

Micro SD 卡座

支持 SDIO 模式和 SPI 模式。

EEPROM

板载一片 IIC 接口的 EEPROM:24C02;

JTAG 接口

10 针 2.54mm 间距的双排排针口,用于 FPGA 程序的下载和调试。

LED 灯

8 个用户发光二极管;

按键

5 个用户按键,1 个硬件复位按键;

FMC 扩展口

FMC 扩展口共扩展 34 对差分 IO,1 路 I2C 总线信号,一路 HSSTLP 高速串行数据收发信号以及一路 HSSTLP 的参考时钟信号。

三:核心板

核心板概述

MES2L676-100HP 核心板是“小眼睛科技”基于多年 FPGA 开发经验,采用紫光同创logos2 系列 PG2L100H-6IFBB676 作为主控芯片而开发的全新国产高性能 FPGA 核心板,具有高数据带宽、高存储容量的特点,适用于视频图像处理、高速数据采集、工业控制等多元应用场景。

MES2L676-100HP 核心板使用了 2 片 DDR3 芯片, DDR3 总容量 8Gbit,组合数据总线宽度为 32bit,最高速率支持 1066Mbps,满足用户高带宽的数据缓存需求。

MES2L676-100HP 核心板扩展出 8 对 HSST TX/RX 信号,用于光纤通信、PCIe 通信、FMC 接口通信,且硬件上 FPGA 芯片到接口之间走线做了等长和差分处理,非常适合二次开发。

MES2L676-100HP 核心板尺寸结构图如下图所示:

系统描述

FPGA

FPGA 型号为 PG2L100H-6IFBB676,属于紫光同创 logos2 系列产品,速度等级为 6,温度范围:工业级(-40~100°C),FBB 封装,管脚数目 676。

紫光同创 Logos2 系列 FPGA 产品型号的编号内容及意义如下:

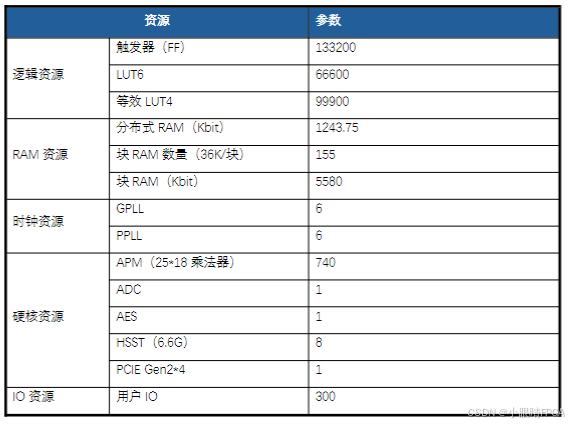

PG2L100H-6IFBB676 主要参数如下:

电源接口

MES2L676-100HP 核心板供电电压为 VCCIN,输入电压为 5V,需通过板对板连接器对应管脚供电,连接底板时通过底板供电。且 BANK_L6 和 BANK_L7 电源也需通过板对板连接器对应管脚供电,连接底板时通过底板供电。板上的电源设计示意图如下图所示:

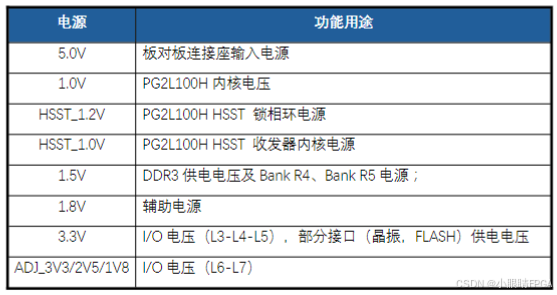

各电源的功能如下表所示:

时钟

MES2L676-100HP 核心板上配有 1 个有源差分晶振,1 个单端 27MHz 晶振。差分晶振用于 DDR3 的参考时钟输入,单端 27MHz 用于 FPGA 的系统时钟源。

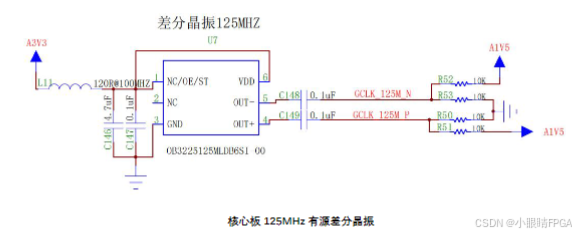

125MHz 差分晶振

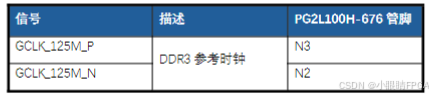

下图中 U7 为 125MHz 有源差分晶振,此时钟为 DDR3 提供输入参考时钟,晶振输出到 FPGA DDR3 信号所在 BANK 上。

具体的管脚约束如下表所示:

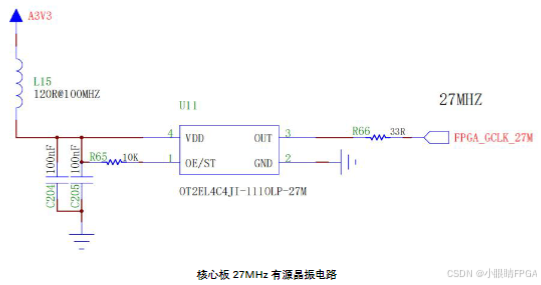

27MHz 单端时钟

下图 U11 为 27MHz 有源晶振电路,此时中连接至 FPGA 的全局时钟管脚上,可为FPGA 提供输入参考时钟。

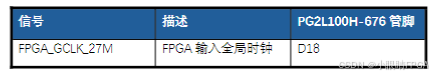

具体的管脚约束如下表所示:

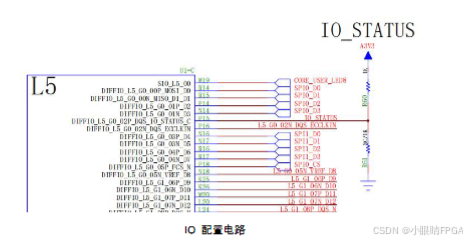

上电 IO Status

在 Logos2 器件上有一个功能复用 IO,控制从上电完成后到进入用户模式之前中所有用户 IO 的弱上拉电阻是否使能。此管脚在配置之前或是配置过程中,该引脚不允许悬空,此 IO 在上电后的对应功能如下:

(1)“0”,使能所有用户 IO 内部上拉电阻。

(2)“1”,不使能所有用户 IO 内部上拉电阻。

MES2L676-100HP 核心板将此管脚的功能默认接 GND,用户可根据需求,自行焊接电阻选择上电后初始的 IO 状态;

功能电路如下:

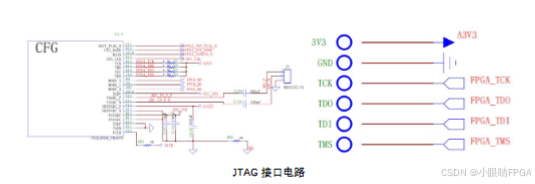

JTAG 接口

MES2L676-100HP 核心板正面左上角预留 JTAG 触点,可在没有底板的情况下调试核心板。FPGA 的 JTAG 信号通过高速板对板连接器与底板 JTAG 接口相连,用于下载FPGA 位流文件或在线调试。

DDR3

MES2L676-100HP 核心板配了两个 4Gbit(512MB)的 DDR3 芯片(共计 8Gbit),两个 DDR 的总数据位宽为 32bit,DDR3 型号采用芯存 XCCC256M16EP-EINAY,(兼容Micron MT41K256M16TW-107:P 、 Micron MT41K256M16HA-125 、 WinbongW634GU6NB-11)。DDR3 SDRAM 的最高运行时钟速度可达 533MHz(数据速率)。

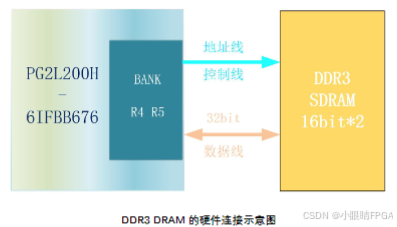

该 DDR3 存储系统直接连接到了 FPGA 的 R4、R5 BANK,DDR3 SDRAM 的硬件连接示意图如下图所示:

DDR3 布线采用 50 欧姆走线阻抗用于单端信号,DCI 电阻(VRP / VRN)以及差分时钟设置为 100 欧姆。每个 DDR3 芯片在 ZQ 上采用 240 欧姆电阻下拉。DDR-VDDQ设置为 1.5V,以支持所选的 DDR3 器件。DDR-VTT 是与 DDR-VDDQ 始终电压跟随,保持为 1/2 倍 DDR-VDDQ 的电压值。DDR-VREF 是一个独立的缓冲输出,等于 1/2 倍DDR-VDDQ 的电压。DDR-VREF 是隔离的,可为 DDR 电平转换提供更清晰的参考。

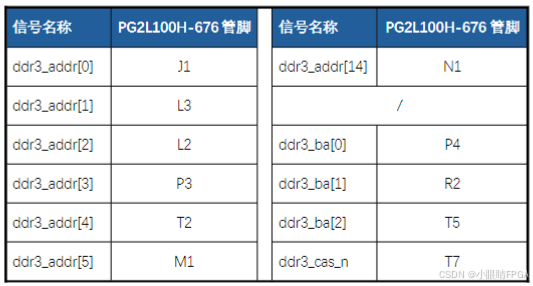

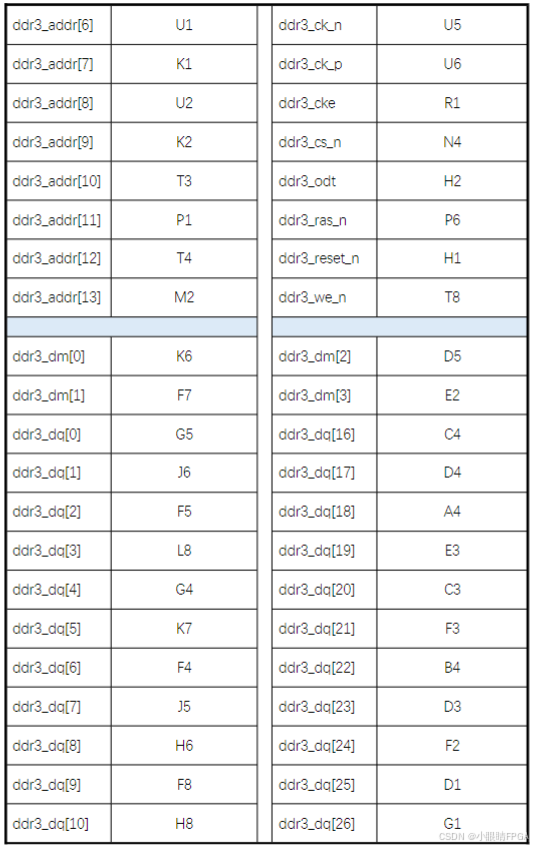

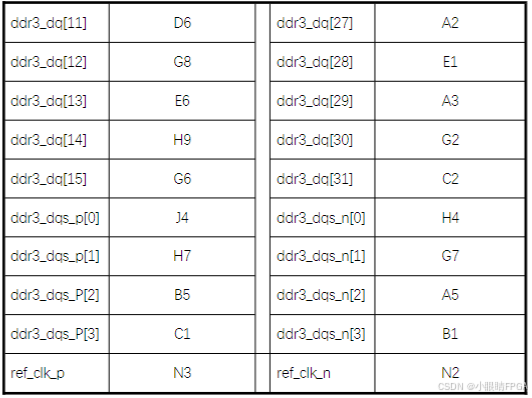

具体的管脚分配如下表所示:

1586

1586

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?