文章目录

一、全加器的概念

1.1 半加器

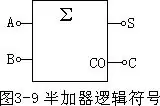

1.1.1何为半加器

半加器电路是指对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。 是实现两个一位二进制数的加法运算电路。

1.1.2 原理图

1.1.3 实现

半加器不考虑低位向本位的进位,因此它不属于时序逻辑电路,有两个输入端和两个输出。

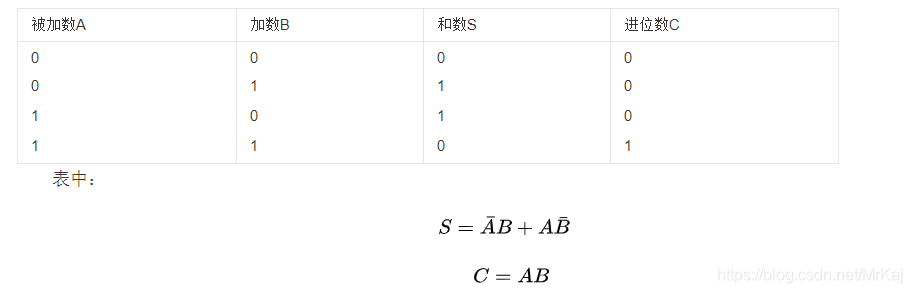

设加数(输入端)为A、B ;和为S;向高位的进位为Ci+1

逻辑表达式:

S = A ⨁ B ; C = A ⋅ B 。 S=A\bigoplus B;C =A\cdot B。 S=A⨁B;C=A⋅B。

1.1.4 输入和输出:

半加器有两个输入和两个输出,输入可以标识为A、B,输出通常标识为求和(Sum)和进位(Carry)。输入经异或(XOR)运算后即为S,经和(AND)运算后即为C。

半加器有两个二进制的输入,其将输入的值相加,并输出结果到和(Sum)和进位(Carry)。半加器虽能产生进位值,但半加器本身并不能处理进位值。

1.1.5 与全加器的区别

半加器没有接收进位的输入端,全加器有进位输入端,在将两个多位二进制数相加时,除了最低位外,每一位都要考虑来自低位的进位,半加器则不用考虑,只需要考虑两个输入端相加即可。

1.2 全加器

1.2.1 概念

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

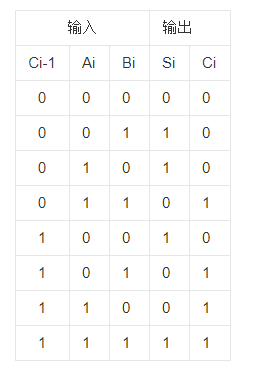

1.2.2 真值表

一位全加器的真值表如下图,其中Ai为被加数,Bi为加数,相邻低位来的进位数为Ci-1,输出本位和为Si。向相邻高位进位数为Ci 。

1.2.3 描述

一个全加器的表达式如下:

S i = A i ⨁ B i ⨁ C i − 1 ; C i = A i B i + C i − 1 ( A i +

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2579

2579

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?