#芯片 #功能ECO #ICG

前文《数字后端APR要撒哪些sparecell,撒多少合适》中提到一种需要ICG的情况:最近遇到一个需求,需要ECO来插入门控时钟,降低功耗。如果sparecell list里没有提前放置ICG将会比较麻烦。

文章里给出的方法是:一种可能的方法是把综合自动插入的ICG挪来用用。但综合时一般是多bit一起插一个ICG,要挪出来的话,就需要把多个DFF的D端全部加MUX。而sparecell list里的MUX一般也不会太多,所以这种方法能不能实现就看运气了。

最后的建议就是:能提前放置几个ICG还是有必要的。

今天要说的是,如果我们是用重新综合的网表作为参考来做功能ECO,由于寄存器DFF位宽可能发生变化,不一定符合Design Compiler的插入ICG的规则,所以,两次插入的ICG的位置和个数并不完全一致。当提前放置的Spare Cell里ICG数量太少,或者位置太远,我们就需要把ICG等价换成MUX了。

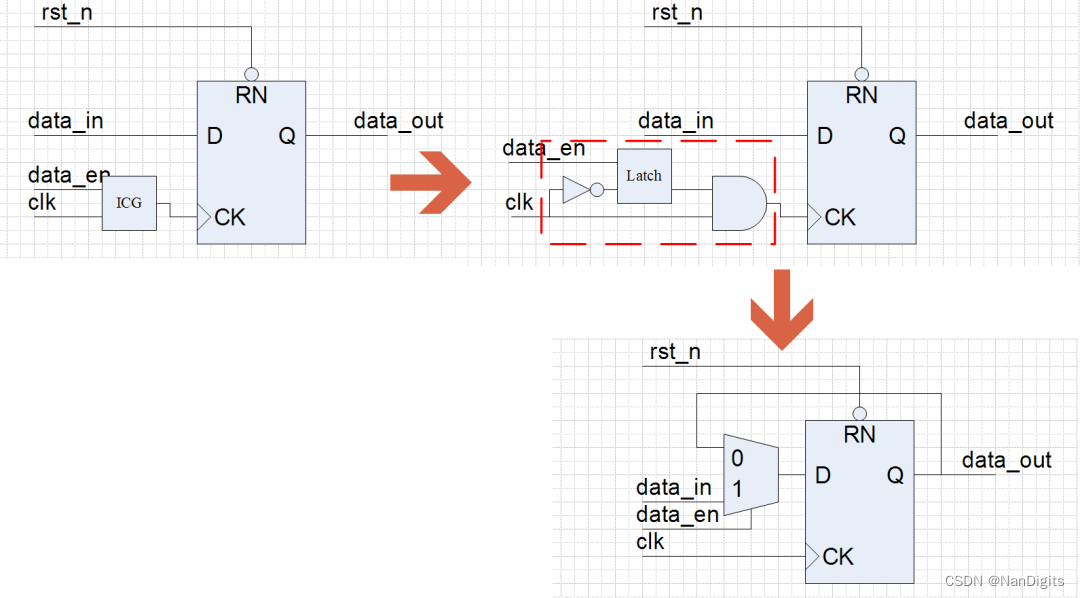

ICG与MUX的等价替换关系如下图,手工替换的话可以照着下图直接替换DFF类型、加MUX和连线。

NanDigits GOF ECO也提供了自动替换ICG的方法。在进行Spare Cell映射时,convert_gated_clocks()会自动把icg映射到dff+mux。参考脚本如下:

get_spare_cells("*/*_SPARE*");

convert_gated_clocks();

map_spare_cells();这种全自动的修改方法相比手工修改,速度快了很多,同时也大大减少了出错的几率。

1810

1810

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?