参考链接:晶振负载电容外匹配电容计算与晶振振荡电路设计经验总结 (sohu.com) https://www.sohu.com/a/230413766_629440前面对于晶振的匹配电容选取一直模棱两可,选一个1.5倍负载电容的电容上去芯片也能用,后面觉得这样对自己和对项目都不负责任,所以仔细研究了一下选取的大致步骤,在这里做一下记录。

https://www.sohu.com/a/230413766_629440前面对于晶振的匹配电容选取一直模棱两可,选一个1.5倍负载电容的电容上去芯片也能用,后面觉得这样对自己和对项目都不负责任,所以仔细研究了一下选取的大致步骤,在这里做一下记录。

首先我们拿到一个晶振的资料时,首先应该找到晶振的负载电容和并联电容

(有些资料上并联电容也叫晶振静态电容,管脚间寄生电容,英文名为shunt capacitance)

确定这两个值以后,我们来看一下晶振的等效模型,不懂的可以看一下这位大佬的文章

(5条消息) 晶振详解之工作原理_sternlycore的博客-CSDN博客 https://blog.csdn.net/sternlycore/article/details/102534554

https://blog.csdn.net/sternlycore/article/details/102534554

负载电容的计算公式如下:

(公式1)

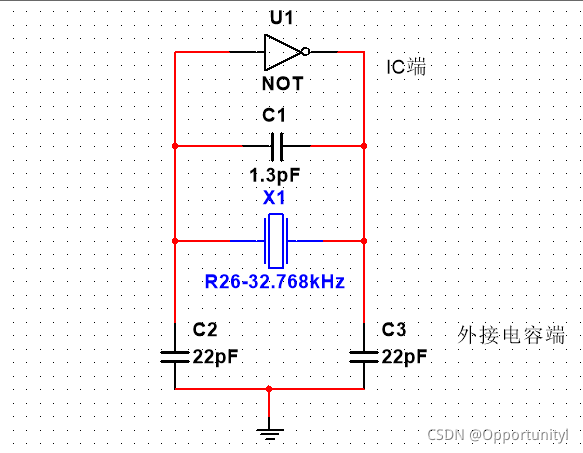

即负载电容跟晶体振荡电路输入管脚到GND的总电容 、晶体振荡电路输出管脚到GND的总电容

以及晶体本身的并联电容

有关。

我们知道晶体振荡电路输入管脚到GND的总电容一般由以下几部分组成:

1.需要外加晶振的单片机或其他IC管脚到GND之间的寄生电容 ;

2.振荡输入端OSC_IN的PCB走线到GND之间的寄生电容 ;

3.电路上额外需要增加的并联到GND的外匹配电容 。

即:

=

+

+

(公式2)

同样的,晶体振荡电路输出管脚到GND的总电容一般由以下几部分组成:

1.需要外加晶振的单片机或者其他IC管脚到GND之间的寄生电容 ;

2.振荡输出端OSC_OUT的PCB走线到GND之间的寄生电容 ;

3.电路上额外需要增加的并联到GND的外匹配电容 。

即:

=

+

+

(公式3)

如上所述,我们应该通过需要外接晶振的单片机或者其他IC的资料确认寄生电容和

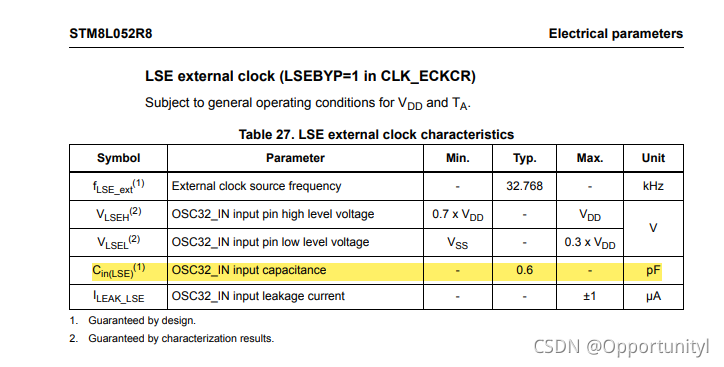

以STM8L052R8T6为例,手册77页详尽的描述了低速外部时钟引脚的寄生电容值为0.6pF。

我们知道,在平时的电路设计中会要求晶体尽可能的靠近振荡电路,即走线尽量短并且对称,所以和

的值应该很小,这里按照经验一般取0.2pF。

为了保持晶体的负载平衡,即晶振电路输入输出的电容需保持一致,所以在实际应用中,往往取

=

。

由此,我们将该例中用到的晶振并联电容以及负载电容值,单片机的寄生电容值代入公式1可以得到:

即:

由公式2或公式3可以推算出:

我们取21.6pF相近的值即22pF作为最终的外匹配电容值。

本文详细介绍了如何根据晶振的负载电容和并联电容来计算匹配电容的具体步骤,并提供了计算公式及实例。了解这些内容有助于提高晶振振荡电路的设计效率。

本文详细介绍了如何根据晶振的负载电容和并联电容来计算匹配电容的具体步骤,并提供了计算公式及实例。了解这些内容有助于提高晶振振荡电路的设计效率。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?