之前有介绍过《Intel的第一款CPU长啥样?Intel 4-Bit的CPU简介》,有了CPU按照今天台式机的配置,还需要主板、内存等配件才能完成整机的搭建,当然对于Inlel 4004来说,这些也是必须的,下面就介绍现代计算机的雏形-微型计算机MCS-4(基于Intel 4004)。

古老CPU启示录-微型计算机MCS-4

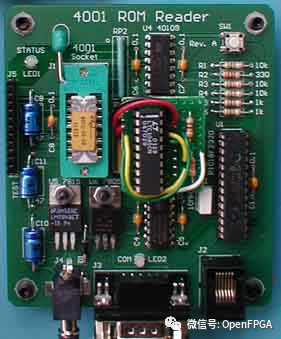

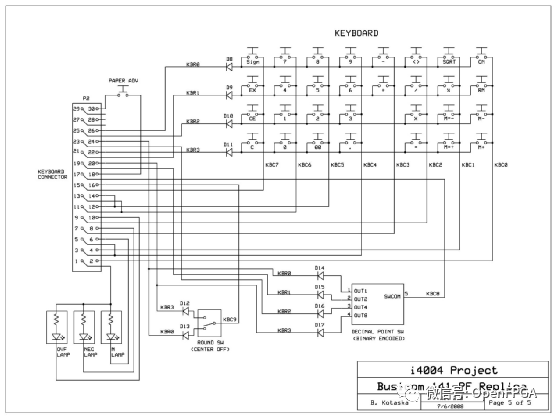

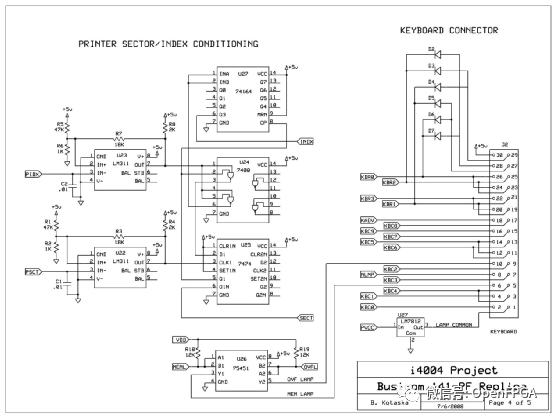

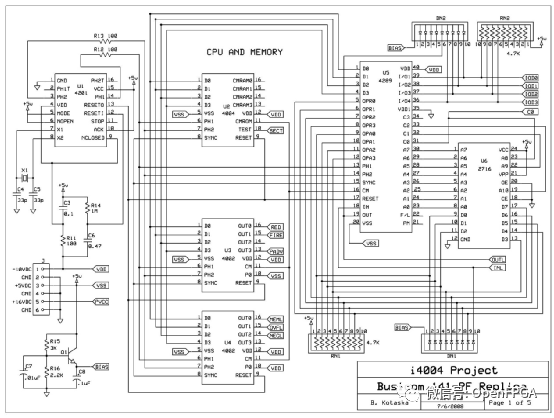

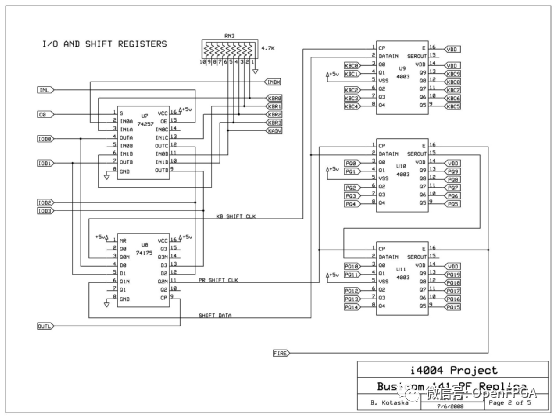

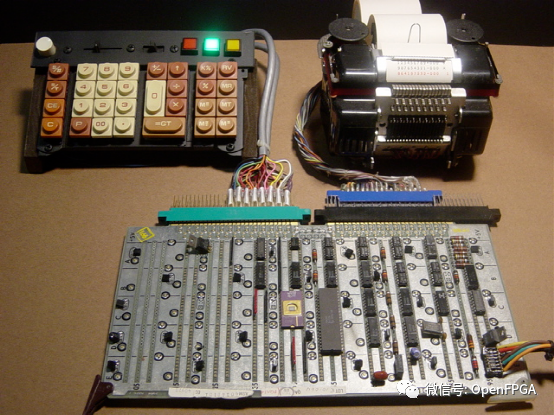

Busicom 141-PF *打印计算器

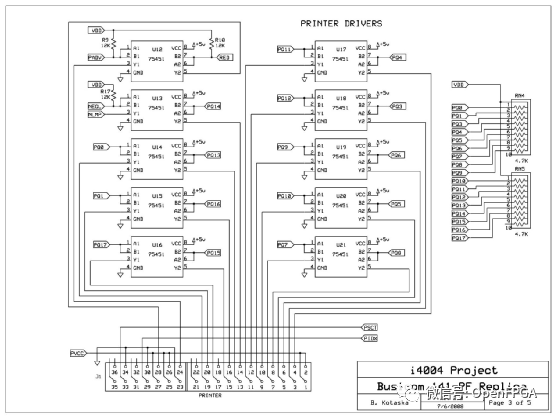

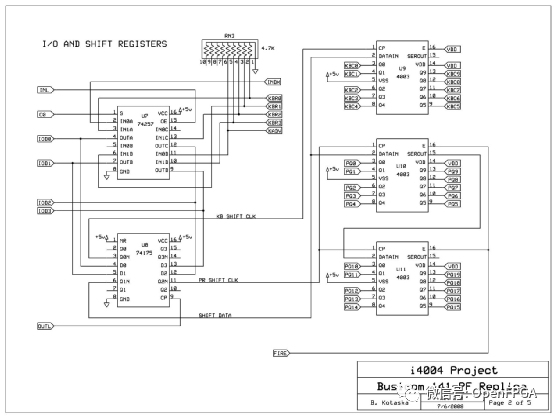

上面就是Busicom 141-PF *打印计算器(一套四块芯片组成的微型计算机,称为MCS-4。它包括一个中央处理单元(CPU)芯片-4004,以及一个用于定制应用程序的支持的只读存储器(ROM)芯片,一个用于处理数据的随机存取存储器(RAM)芯片以及一个移位存储-输入/输出(I / O)端口的寄存器芯片。),经过国外大神进行逆向过程,得到了原理图,如下:

逆向出来的计算器

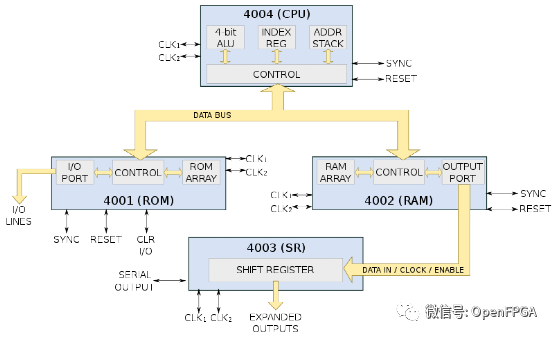

MCS-4只能在4001 ROM和4004 CPU上最低限度地运行(最小系统),但是其设计可以在RAM和移位寄存器中正常运行。另外,两个芯片4008和4009扩展了系统,使其可以与Intel现有的任何内存芯片选择配合使用。

| 部分 | 描述 |

| 4001 | 只读存储器 |

| 4002 | 内存 |

| 4003 | 移位寄存器 |

| 4004 | 主控板 |

| 4008 | 地址锁存器 |

| 4009 | I / O介面 |

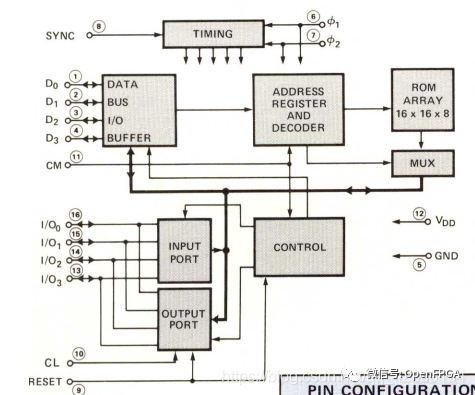

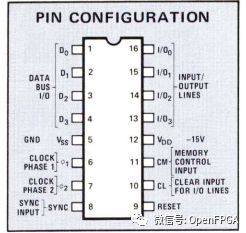

4001(ROM)

4001是一个256x8位掩模可编程ROM和4位I/O端口

4001是一个2048位的金属掩模可编程ROM,为MCS-4微型计算机提供定制的微程序显示功能。

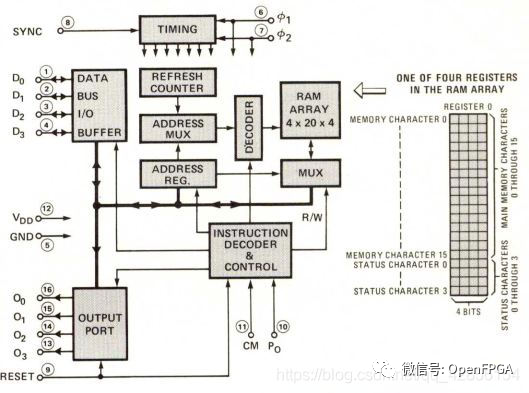

4002(RAM)

320位RAM和4位输出端口

4002执行两个函数。作为RAM,它将320位存储在4个寄存器中,每个寄存器包含24个4位字符(16个主存字符和4个状态字符)。作为与周边设备通信的载体,它具有4条输出线路和相应的控制逻辑来执行输出。

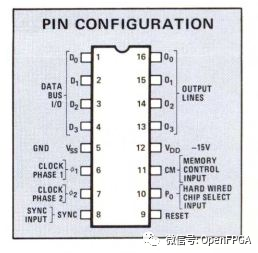

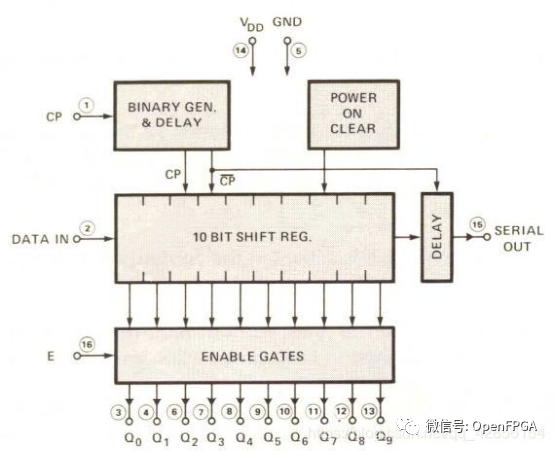

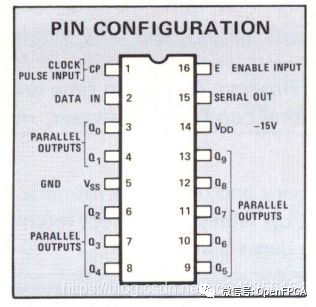

4003(SR)

10位串行进/并行串行出移位寄存器(SR)

4003是一个10位静态移位寄存器,具有串行输入、并行和串行输出数据,其功能是增加输出行数,与键盘、显示器、打印机、电传打字机、开关、读卡器、A-D转换器等 I/O设备进行接口。公众号:OpenFPGA

4004(CPU)

Intel的第一款CPU长啥样?Intel 4-Bit的CPU简介

指令执行周期

详细的功能规范描述了系统的操作、指令集、每条指令的CPU活动以及一些编程和硬件示例,这些详细的功能规范是单独发布的,可根据要求提供。

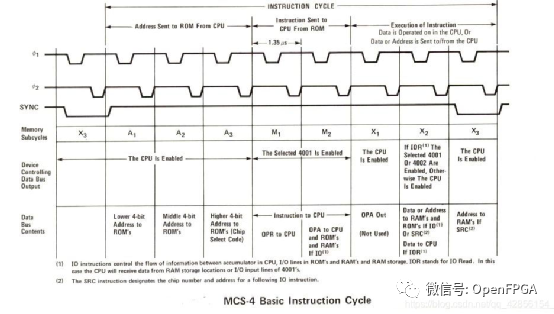

下面是系统运行的简要概述MCS-4使用10.8 usec指令周期。CPU(4004)生成同步信号(SYNC),指示指令周期的开始,并将其发送到ROM(4001)和RAM(4002)。公众号:OpenFPGA

基本指令执行需要8或16个周期的750千赫时钟。在一个典型的序列中,CPU在前三个周期(A1, A2, A3)向ROM发送12位地址。所选ROM芯片在接下来的两个周期(M1. M2)中向CPU发送8位指令(OPR, OPA),然后在最后三个周期(X1. X2. X3)中对指令进行解释和执行。

CPU、RAM和ROM可以由外部复位线控制。当复位被激活时,寄存器和触发器的内容被清除。重置后,CPU将从地址0和CM-RAM0开始。

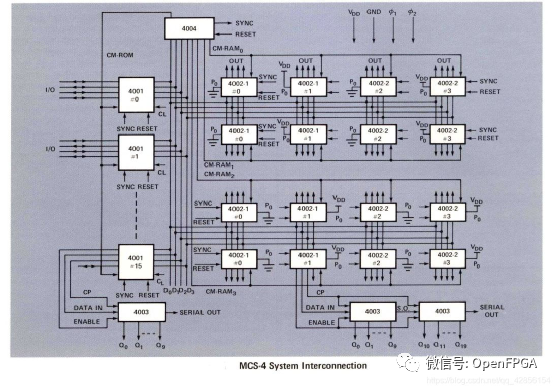

MCS-4可以有多达4K x 8位ROM字,1280 x 4位RAM和128 I/O行,不需要任何连接逻辑。通过添加一些简单的门,MCS-4可以有多达48个RAM和ROM的任何组合和192 I/O行。

4001、4002和4004由4线数据总线(D0、D1、D2、D3)连接,用于芯片之间的所有信息流,除了CPU在另外6条线路上发送的控制信号。MCS-4系统的互连如上图所示。显示了一个扩展配置。最小系统配置由一个CPU(4004)和一个ROM组成(4001)。指令周期图显示了每个时钟周期内数据总线上的活动,以及如何细分基本指令周期。公众号:OpenFPGA

每个数据总线输出缓冲区都有三个可能的状态“1”、“0”和浮点数。在给定的时间内,只允许一个输出缓冲区驱动数据线,因此,所有其他缓冲区必须处于浮动状态。但是,每个数据行可以同时接收多个输入缓冲区MCS-4有一个非常强大的指令集,允许二进制和十进制算术。它包括条件分支。跳转到子例程,并提供了通过间接获取有效使用ROM查找表。通常,850 usec中可以添加两个8位数字。

通过上面可以得到下图的系统互联

参考链接:https://www.4004.com/busicom-replica.html

http://www.intel4004.com/

http://e4004.szyc.org/

https://en.wikichip.org/wiki/intel/mcs-4

NOW现在行动!

推荐阅读

【Vivado那些事】如何查找官网例程及如何使用官网例程【Vivado使用误区与进阶】总结篇【Vivado那些事】Vivado下头文件使用注意事项【Vivado那些事】Vivado中常用的快捷键(一)F4键【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键

HDL Designer Series(HDS)介绍

SystemVerilog数字系统设计_夏宇闻 PDF

Verilog 里面,always,assign和always@(*)区别

FPGA上如何求32个输入的最大值和次大值:分治一文读懂TCP/IP!《RISC-V on T-Core》学习笔记新年愿望是什么?先送大家一波开发软件谈谈FPGA(入门)学习的两种方式ZYNQ-迷恋ZYNQ-FPGA开发板资源分享

零基础入门FPGA,如何学习?

黑金全部开发板资料(FPGA+ZYNQ)分享

【Vivado那些事】FPGA配置失败,无法启动怎么办

你会在github上找项目吗?

图书推荐|ARM Cortex-M0 全可编程SoC原理及实现

简谈:如何学习FPGARISC-V再进阶!世界首款5纳米RISC-V SOC成功流片!

几款开源SDR平台

Xilinx 推出 Kria 自适应系统模块产品组合,在边缘加速创新和 AI应用

RISC-V指令集架构介绍及国内外厂商介绍

Vitis尝鲜(一)

SDR/无线设计中LNA和PA的基本原理

拆解1968年的美国军用电脑,真的怀疑是“穿越”啊!

一文最全科普FPGA技术知识

首个中文CPU指令规范 龙芯推出LoongArch基础架构手册

你见过1-bit CPU吗?高级FPGA设计技巧!多时钟域和异步信号处理解决方案

【Vivado那些事】Vivado中电路结构的网表描述

ZYNQ中裸机开发和Linux开发有什么区别?

点击上方字体即可跳转阅读哟

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?