Verilog数字系统基础设计-奇偶校验

奇偶校验是一种简单、实现代价小的检错方式,常用在数据传输过程中。对于一组并行传输的数据(通常为8比特),可以计算岀它们的奇偶校验位并与其一起传输。接收端根据接收的数据重新计算其奇偶校验位并与接收的值进行比较,如果二者不匹配,那么可以确定数据传输过程中岀现了错误;如果二者匹配,可以确定传输过程中没有出错或者出现了偶数个 错误(出现这种情况的概率极低)。奇偶校验包括奇校验和偶校验两种类型。

偶校验和奇校验

对于偶校验,包含校验比特在内,1的总数是偶数。在奇校验中,1的总数则为奇数。

例如:

data_in[7:0]=1010_1011

在该数据串中有5个1,偶校验时,校验结果为1,这样1的总个数为偶数;在奇校验时,校验比特为0,使得1的总个数为奇数。又如:

data_in[7:0]=0000_1111

在该数据串中有4个1,偶校验时,校验结果为0,使得1的总个数仍为偶数;在奇校验时,校验比特为1,使得1的总个数为奇数。

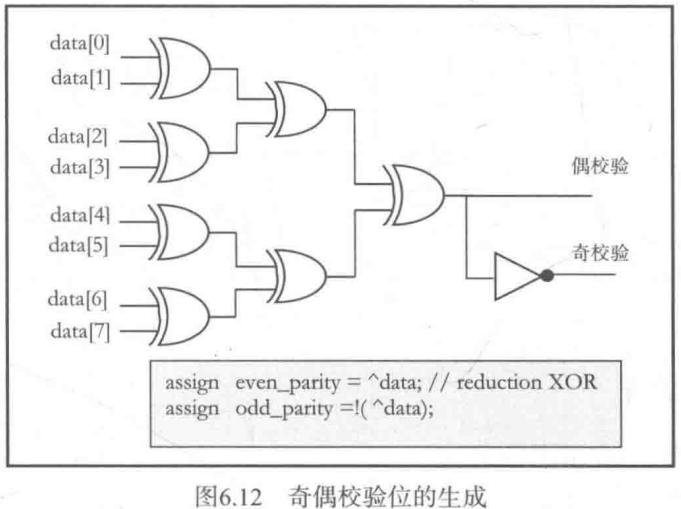

奇偶校验位的生成

将所有的用户信息按比特异或可以得到偶校验结果,将偶校验结果取反就可以得到奇校验结果,具体电路如图6.12所示。

奇偶校验的应用

在具体应用奇偶校验时,在发送端,奇偶校验电路计算每一组发送数据的奇偶校验位,将其与数据一起发送;在接收端,奇偶校验电路重新计算所接收数据的奇偶校验值,并将其与收到的校验值进行比较,如果二者相同,可以认为没有发生错误,如果二者不同,可以认为发生了传输错误。需要说明的是,如果错误比特数为偶数(2,4,6等),那么奇偶校验是无法发现这类错误的。例如,发送的数据为8’bl010_1011此时计算出的偶校验值是1。如果在传输中比特3和比特2的值从10跳变为01,那么此时接收到的数据为8’bl0100111,接收的偶饺验值仍然为1。对接收的数据进行偶校验计算,得到的结果仍然为1,这与收到的校验值是相同的,接收电路无法检测出接收数据中岀现的错误。

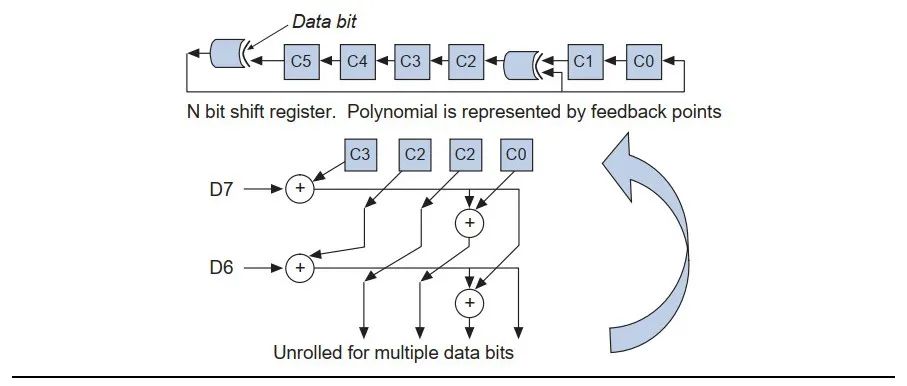

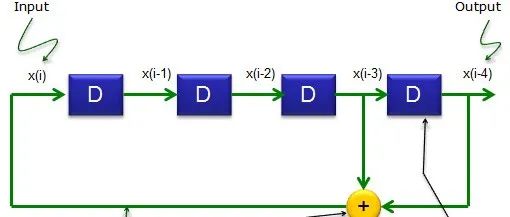

目前还有很多检错能力更强的编码方式,如CRC(循环冗余校验)。奇偶校验常常用在芯片内部数据传输或者外部数据总线上的数据传输中,如传统的PCI总线中就使用了奇偶校验。CRC更适用于以帧为单位的数据传输中(如PCIe)奇偶校验结果需要和原始数据一起在每个时钟周期进行传送,而针对每个帧的CRC校验结果,通常出现在一个帧的尾部,跟随数 据巾贞一起传输。

虽然奇偶校验能够发现单比特错误,但却不能纠正任何错误。前面描述过的纠错码(Error Correction Codes,ECC)可以发现并纠正错误。

关于CRC校验可以查看之前的文章。

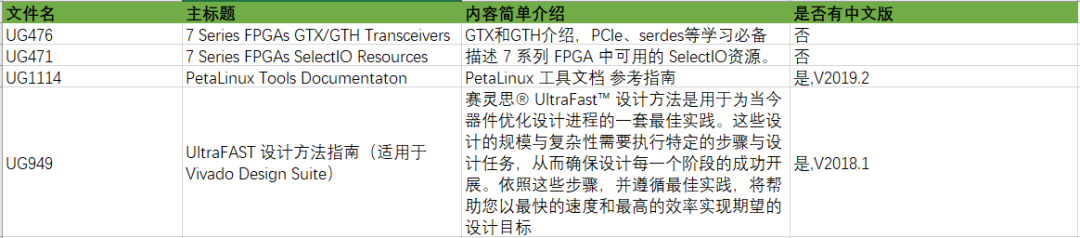

学习Xilinx FPGA最好的资料其实就是官方手册,下表总结了部分手册的主要介绍内容,关注我,持续更新中......

推荐阅读

【Vivado那些事】Vivado中常用的快捷键(二)其他常用快捷键

图书推荐|ARM Cortex-M0 全可编程SoC原理及实现

1202年了,还在使用虚拟机吗?Win10安装Ubuntu子系统及图形化界面详细教程

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?