今天给大家带来DeepSeek推荐的开源项目,因为有些项目已经失效了,所以会替代为一些相近项目。

一、基础入门项目

1. 数字逻辑与Verilog/VHDL入门

项目名称: FPGA 101

https://github.com/mmicko/fpga101-workshop

简介: 包含基础组合逻辑、时序逻辑、状态机、计数器等设计。

学习内容:

Verilog/VHDL语法

组合逻辑(加法器、多路选择器)

时序逻辑(计数器、分频器)

有限状态机(FSM)设计

学习路线:

学习数字电路基础(布尔代数、触发器、寄存器)。

掌握Verilog/VHDL基础语法。

实现简单电路(如7段数码管驱动、PWM生成)。

完成状态机项目(如交通灯控制、自动售货机)。

2. 基于FPGA的简单游戏

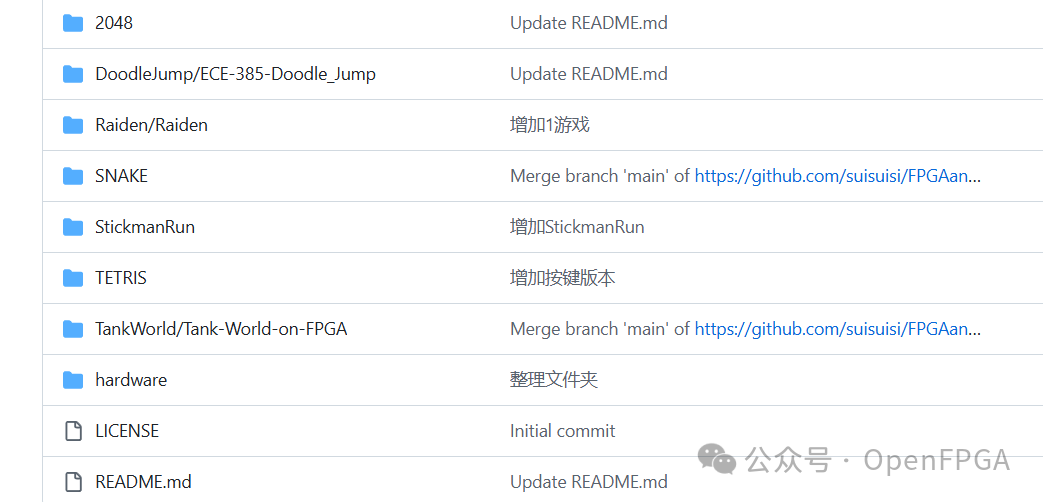

项目名称: FPGAandGames

https://github.com/suisuisi/FPGAandGames

简介: 用FPGA实现经典游戏,通过VGA输出显示。

学习内容:

VGA时序控制

简单图形渲染

按键输入消抖

### 学习路线:

学习VGA显示原理。

实现基础图形生成(矩形、线条)。

添加游戏逻辑(球拍移动、碰撞检测)。

二、中级项目(处理器与接口)

3. RISC-V CPU设计

项目名称: PicoRV32 或 SERV(超小型RISC-V核)

https://github.com/cliffordwolf/picorv32

https://github.com/olofk/serv

简介: 轻量级RISC-V处理器实现,适合学习CPU架构。

学习内容:

CPU流水线设计

总线协议(Wishbone/AXI)

指令集架构(ISA)

学习路线:

学习计算机组成原理(冯·诺依曼架构、流水线)。

研究RISC-V指令集手册。

分析PicoRV32代码,理解取指-译码-执行流程。

扩展功能(添加中断支持或自定义指令)。

4. FPGA与外设通信

项目名称: LiteX

https://github.com/enjoy-digital/litex

简介: 开源FPGA SoC构建框架,支持多种外设(UART、SPI、DDR)。

学习内容:

SoC设计方法

外设驱动开发

软核CPU(如VexRiscv)集成

学习路线:

学习SoC基本概念(CPU、总线、外设)。

用LiteX生成最小系统(CPU + UART)。

添加自定义外设(如LED控制器)。

三、进阶项目(算法加速与系统设计)

5. 图像处理加速

项目名称: Open Source Image Processing on FPGA

https://github.com/hdl-util/hdmi

简介: 实现摄像头采集、图像处理(边缘检测、滤波)、HDMI输出。

学习内容:

视频流协议(HDMI、MIPI)

并行计算优化(流水线、并行计算单元)

算法硬件化(如Sobel算子、高斯滤波)

学习路线:

学习图像处理基础算法。

实现单帧图像处理(如灰度转换)。

扩展为实时视频流处理。

6. 神经网络加速器

项目名称: VTA (Versatile Tensor Accelerator)

https://github.com/apache/tvm-vta

简介: 支持TVM框架的深度学习加速器,适合AI硬件加速研究。

学习内容:

张量计算单元设计

内存层级优化

软硬件协同(TVM编译器与FPGA联动)

学习路线:

学习神经网络计算图与硬件映射。

部署预训练模型(如MNIST分类)到VTA。

优化计算单元(如矩阵乘法并行化)。

四、专业级项目(高速接口与复杂系统)

7. 高速通信协议

项目名称: FPGA PCIe/USB 3.0 Core

https://github.com/enjoy-digital/litepcie

简介: 实现PCIe或USB 3.0通信,适合数据中心或高速传输场景。

学习内容:

高速SerDes技术

PCIe/USB协议栈

DMA数据传输

学习路线:

学习高速接口协议(物理层、数据链路层)。

实现FPGA与PC间简单数据通信。

设计高性能DMA引擎。

8. 开源FPGA工具链

项目名称: Yosys + NextPnR

https://github.com/YosysHQ/yosys

简介: 开源综合与布局布线工具,支持Lattice/Lattice ECP5等FPGA。

学习内容:

FPGA工具链流程(综合、映射、布线)

约束文件(SDC)编写

时序分析优化

学习路线:

学习FPGA开发全流程。

用Yosys综合简单设计。

对比开源与商业工具(如Vivado)的差异。

五、学习路线总结

阶段1:基础(1-3个月)

目标: 掌握数字电路与HDL语言。

步骤:

学习《数字电子技术基础》(阎石)。

完成Verilog/VHDL基础项目(计数器、状态机)。

使用开发板(如Basys3、DE10-Nano)验证设计。

阶段2:中级(3-6个月)

目标: 掌握处理器与外设交互。

步骤:

学习计算机体系结构(推荐《计算机组成与设计:RISC-V版》)。

实现RISC-V软核并运行简单程序。

集成UART、SPI等外设。

阶段3:进阶(6-12个月)

目标: 复杂系统与算法加速。

步骤:

学习算法硬件化(如FFT、CNN)。

实现高速接口(PCIe、DDR3)。

参与开源社区项目(如LiteX、VTA)。

阶段4:专业(1年以上)

目标: 全栈FPGA开发(RTL到物理实现)。

步骤:

研究时序约束与低功耗设计。

掌握开源工具链(Yosys、SymbiFlow)。

贡献代码或发布自己的开源项目。

六、工具与资源推荐

开发工具:

仿真: Verilator、ModelSim

综合与实现: Vivado、Quartus、Yosys

调试: SignalTap、ILA(集成逻辑分析仪)

学习资源:

书籍: 《FPGA原理与结构》《RISC-V架构与嵌入式开发》

社区: FPGA4Fun、RISC-V International、GitHub FPGA主题仓库。

总结

总结的项目基本符合我们之前推荐的STAR数比较多的项目,适合新手学习和复刻,尤其感觉总结的内容比较符合项目

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?