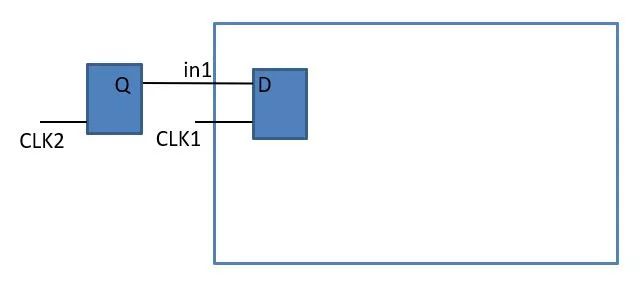

今天我们介绍的时序分析基本概念是Virtual Clock,中文名称是虚拟时钟。我们通常说的create_clock, create_generated_clock 都是real clock。而virtual clock则不挂在任何port或者pin上,只是虚拟创建出来的时钟。如下所示:

#定义虚拟时钟

create_clock -name VCLK -period 10 -waveform {0 5}

为什么我们要定义virtual clock?

我们通常会把input/output delay挂在virtual clock上,因为input/output delay约束本来就是指片外的时钟,所以挂在virtual clock上较为合理。

如上图所示:片外的时钟CLK2和片内的时钟CLK1频率不同。这样的情况下,如何来定义input port {in1}上的约束?

这时,我们就可以给input port {in1}创建一个virtual clock。

create_clock -name VCLK2 -period 10 -waveform {2 8}

create_cloc

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3632

3632

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?