本人初次接触AXI接口,在了解了AXI接口读写时序后,计划使用AXI接口对BRAM进行读写,并进行仿真测试,AXI接口有三种类型:AXI4、AXI-lite、AXI-stream,我一开始成功对AXI4进行了读写测试,在了解读写时序后这是很简单的,但是在对AXI-lite进行读写测试时,本以为读写时序与AXI4一致,并且端口数量大大减少,实验应该会很快做完,但却出现了下图所示情况:

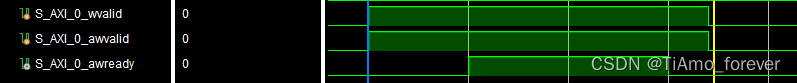

图中即使使awvalid信号一直为高,awready信号却迟迟无法拉高,这与AXI4仿真时情况不符,之后再一次偶然打包AXI接口的ip时,发现了原因,如下图所示:

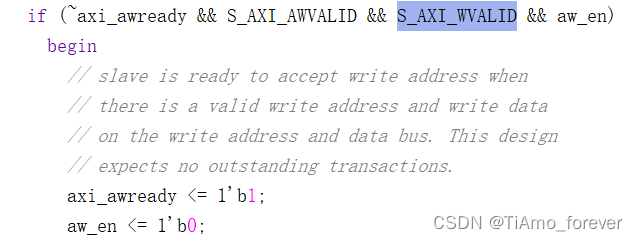

此处展示的是模拟AXI-lite的有关代码,可以看到,要想拉高awready,不仅需要拉高awvalid,而且wvalid信号 也要同时为高,再来看模拟AXI-full的有关代码:

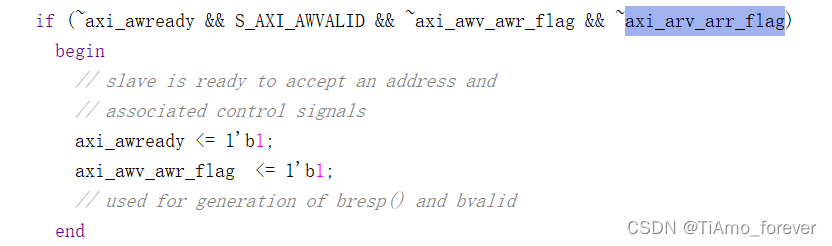

可以看到AXI-full中拉高awready的条件仅仅是awvalid拉高即可(其中的awr_flag和arr

_flag信号在复位时会自动置0),接下来我尝试把awvalid和wvalid 同时拉高仿真AXI-lite,结果如下:

可以看到awready信号成功拉高。

由于作者为初学者,这个问题困扰了我几天时间,且在网上找了很久没能获得答案,仅以此文做一个记录,若并不是您要找的答案,请忽略。

6954

6954

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?