前 言

本文主要介绍HLS案例的使用说明,适用开发环境:Windows 7/10 64bit、Xilinx Vivado 2017.4、Xilinx Vivado HLS 2017.4、Xilinx SDK 2017.4。

Xilinx Vivado HLS(High-Level Synthesis,高层次综合)工具支持将C、C++等语言转化成硬件描述语言,同时支持基于OpenCL等框架对Xilinx可编程逻辑器件进行开发,可加速算法开发的进程,缩短产品上市时间。

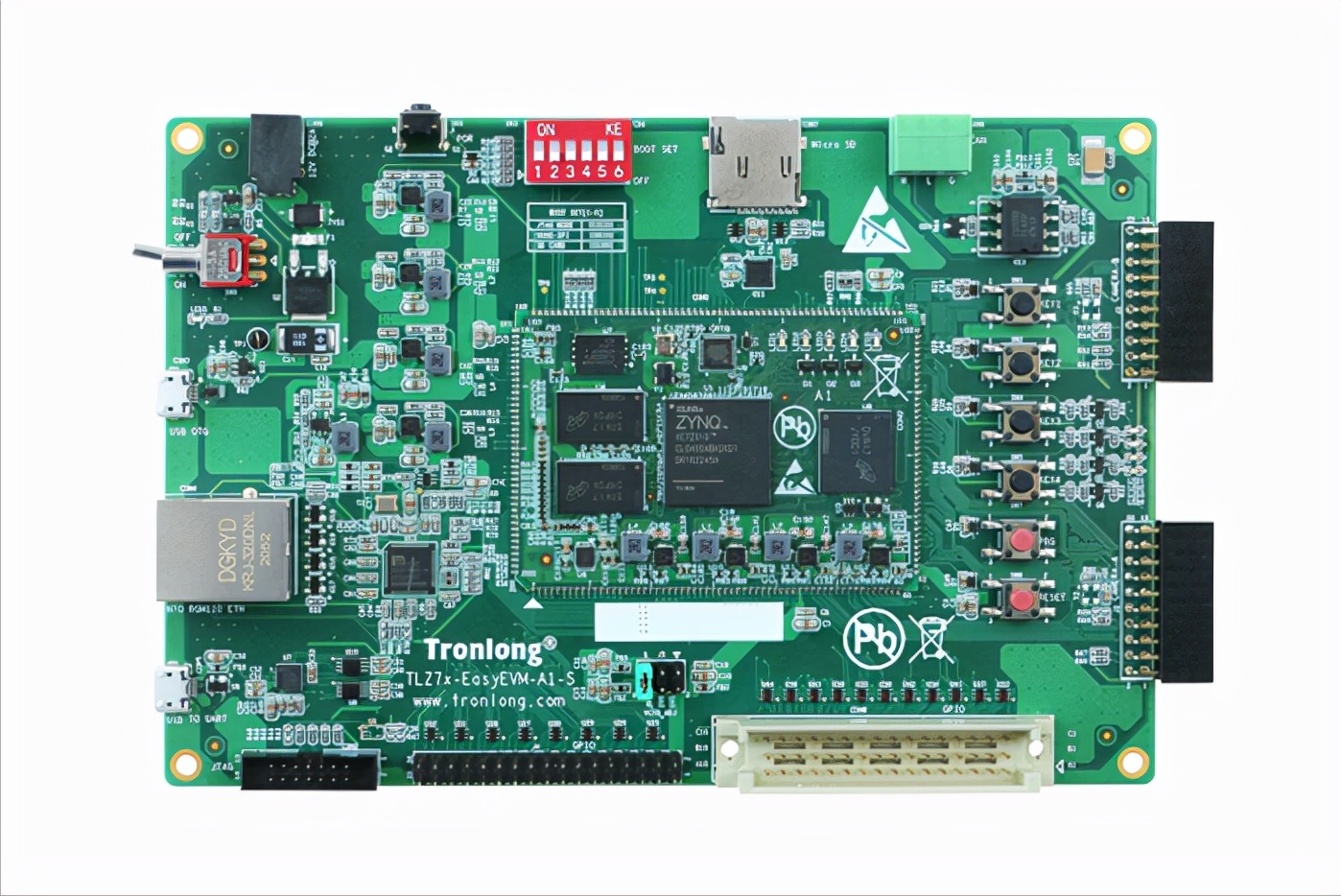

本次案例用到的是创龙科技的TLZ7x-EasyEVM-S开发板,它是一款基于Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC评估板,处理器集成PS端双核ARM Cortex-A9 + PL端Artix-7架构28nm可编程逻辑资源,评估板由核心板和评估底板组成。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。

TLZ7x-EasyEVM-S评估板

TLZ7x-EasyEVM-S评估板评估板接口资源丰富,引出千兆网口、双路CAMERA、USB、Micro SD、CAN、UART等接口,支持LCD显示拓展及Qt图形界面开发,方便快速进行产品方案评估与技术预研。

HLS基本开发流程如下:

- HLS工程新建/工程导入

- 编译与仿真

- 综合

- IP

订阅专栏 解锁全文

订阅专栏 解锁全文

9110

9110

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?