写在前面——

DDR3的英文全称是Double-Data-Rate Three Synchronous Dynamic Random Access Memory——第三代双倍数据率同步动态随机存取存储器。外观看上去就是内存条,属于SDRAM。简单介绍他的原理和功能就是:通过预读取和CQS的产生以及DLL的延时功能传输2倍于芯片位宽的数据。

一、工作流程的介绍【下面图片来源于网络】

①工作时首先进行芯片的初始化,这一点和SDRAM的MRS一样。

②如上图(左),进行Bank的选择和行地址的选择【同时进行】。

③tRCD(RAS和CAS之间的延迟),DDR3的tRCD可选1.5、2、2.5、3。就是延迟几个时钟周期。

④如上图(右),进行列地址和操作命令(是读还是写)发出【同时进行】。行地址和列地址共用一根地址线,但是可以通过行地址选通信号(RAS)以及列地址选通信号(CAS)区分,都是低电平有效。

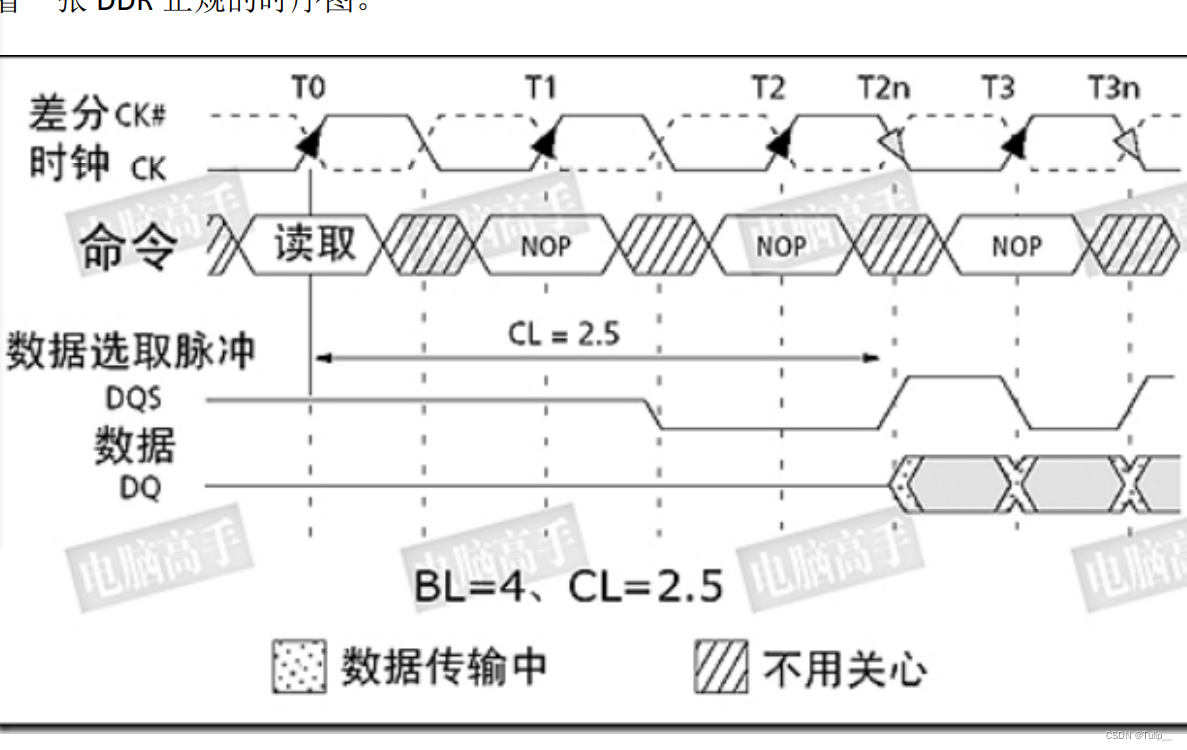

读取数据时

⑤‘CL【CAS Latency】列寻址到数据发送之间的潜伏期【CAS到生成DQS之间的间隔】DQS下文提到。

CL存在的意义在于 寻址完成以后获取到了芯片内部的数据,要实现预读取。在这一阶段要预读取完成同时完成 DQS的导入

【重点介绍】DQS——数据选取脉冲

如上图可以看出来,在读取内存时,数据和DQS在差分信号交叉点处同时产生。

⑥’tAC【数据真正传到I/O接口与触发DQS之间的时间间隔】

tAC的存在在于 数据传到I/O接口的时间有快有慢,但是要同步向外发出数据,这个间隔就是保证所有数据都到达I/O口

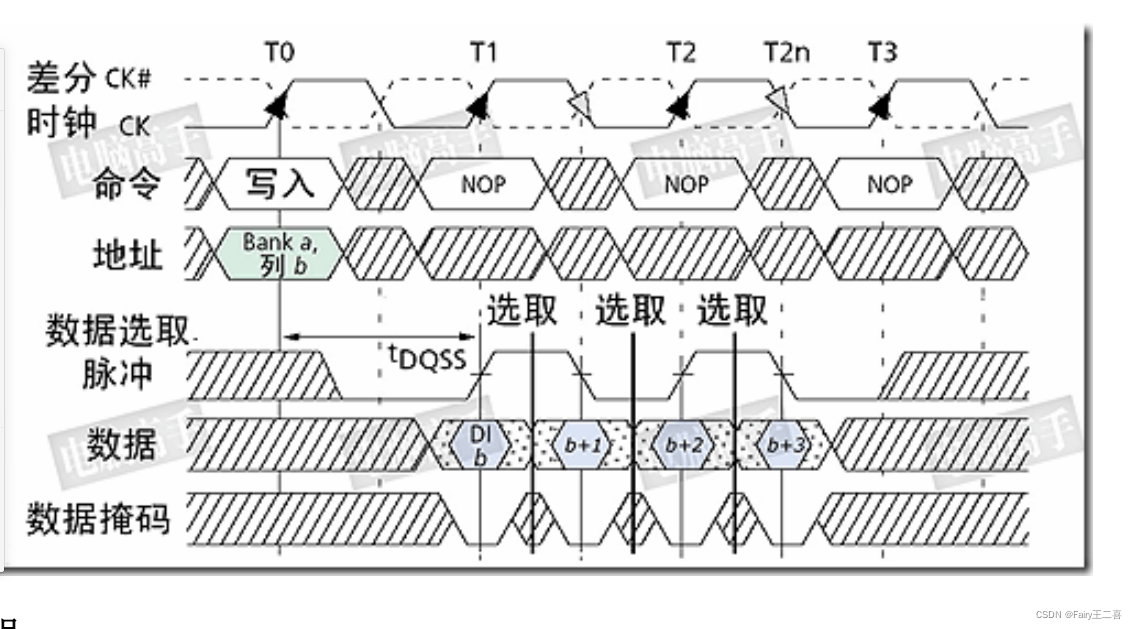

写入数据

⑤‘’tDQSS(DQS相对于写命令的延迟时间)

tDQSS的存在意义在于 同步 在写入状态时DQS不是芯片内部产生的,是按发送方的DQS来。

数据和DQS要等一段时间才能全部送达

在写入数据的时候,为了获取稳定的数据,我们都是在数据的电平处将数据取出来,所以CQS的边沿对着的是数据的电平处而不是边沿处。

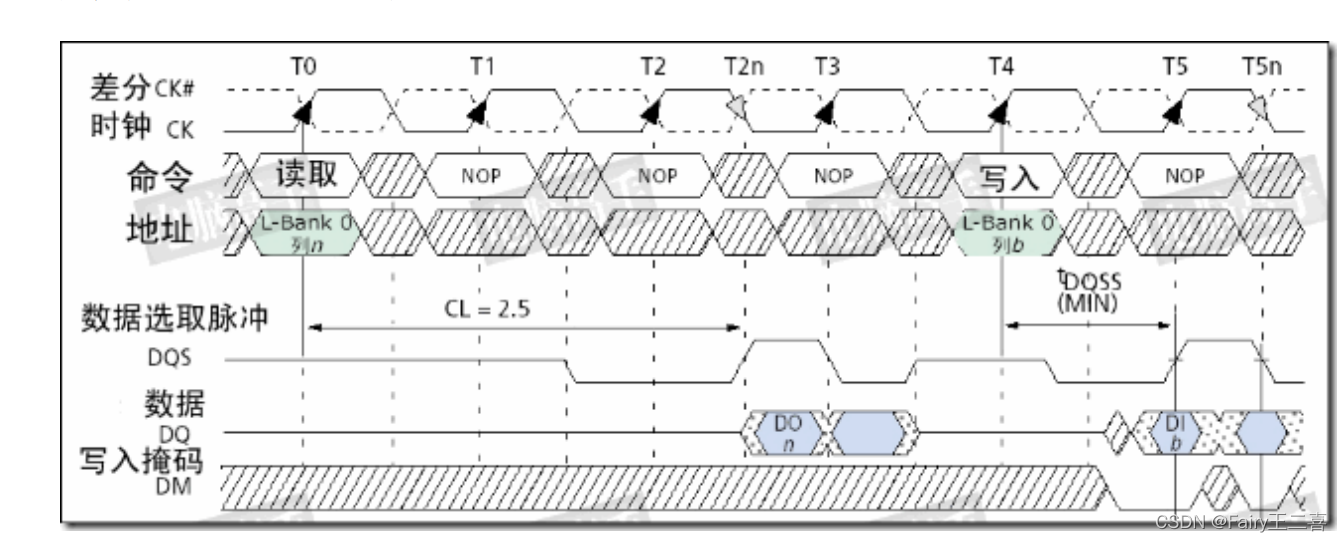

⑥‘’读后写操作

如上图读 取内存的时候要同步发送出去的数据而延迟CL

以及写入数据时候要同步接收的数据而延迟tCQS

以及如果CL=2.5时两者之间还要延迟半个周期(原因是写入命令的发送必须在时钟上升 沿,而CL是2.5恰好让最后一个数据的发出是在CQS的上升沿)

二,重点概念的介绍

1、CQS

通过从L-Bank中一次性取出来内部的数据给到锁存器(8bit),锁存器将他们分成两部分(两个4bit)给复用器,复用器先后将他们发给发送器,每当CQS发生器产生CQS的边沿(上下边沿都算)的时候就发出去这两部分。

由此可知在DDR中

内部存储单元容量(芯片内部总线位宽)=2*芯片位宽(芯片I/O总线位宽)

2、突发长度和写入掩码

突发长度指的是连续传输的周期数【有2、4、8】

用DM信号屏蔽(外部输入),在CQS的边沿看DM的信号,高电平就屏蔽数据。

3、延迟锁定回路DLL

DDR有两个时钟,一个是内部一个是外部。个人理解是内部时钟控制读,外部负责写,但是要求内外部时钟是同步的。但是绝对的同步时无法做到的(因此会有tAC),唯一能做到的就是两个时钟上升沿和下降沿的状态同步——方法就是延迟内部时钟使两时钟边沿同步——用到的就是DLL。

有两种方法,分别时CC和CMS。

三、硬件实现

1、用vivado IP core中自带的功能实现MIG。

2、如果设置的输入时钟频率和开发板上的不一样记得加锁相环。

clk period 是指期望多大的频率传输数据

input clk period是输入频率,与开发板一样,如果不一样加锁相环。

system clock选择No Buffer表示差分

Reference clock表示DLL延迟时钟

3、驱动代码见下一篇笔记

841

841

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?