riscv 32单周期处理器cpu,工程基于vivado,指令集rv32i,systemverilog编写,结构简单,指令存在ram中,可仿真,代码结构清晰,适合初学者学习,并赠送包括riscv中文手册和riscv指令集文档的中文版本

YID:7396793298620018

两点一线

RISC-V(Reduced Instruction Set Computer - V)是一种开放标准指令集架构(ISA),它以其简洁、灵活、可扩展的特点在近年来逐渐受到广大程序员和学习者的关注。本文将围绕RISC-V 32位单周期处理器CPU展开讨论,介绍其工程基于Vivado,指令集为RV32I,使用SystemVerilog编写的特点,以及其适合初学者学习的优势。同时,我们还会为读者赠送RISC-V中文手册和RISC-V指令集文档的中文版本,以帮助更多人深入了解和学习RISC-V架构。

首先,我们来了解一下RISC-V架构的背景和特点。作为开放的指令集架构,RISC-V允许任何人使用、研究和修改其指令集,这与传统闭源的指令集相比具有明显的优势。RISC-V的指令集被设计为模块化和可扩展的,可以根据应用的需求选择不同的扩展指令集,使得RISC-V架构适用于广泛的应用场景。

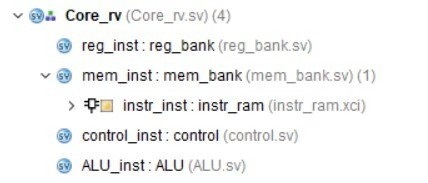

本文要介绍的是基于RISC-V的32位单周期处理器CPU。该处理器的工程基于Vivado,Vivado作为一种高度集成的设计工具,可以提供全面的设计和验证功能。在这个处理器中,我们采用了RV32I指令集,即RISC-V的基本整数指令集。这个指令集包含了简单、常用的整数操作指令,如加载、存储、算术运算等。采用RV32I指令集的优势在于其简洁性和易于理解性,非常适合初学者学习。

该处理器的代码是使用SystemVerilog编写的,SystemVerilog是一种硬件描述语言(HDL),可以方便地描述和设计数字电路。通过使用SystemVerilog,我们可以清晰地描述整个处理器的结构和功能,并且可以使用仿真工具来验证其正确性。处理器的代码结构清晰,易于阅读和理解,对于初学者来说是一个非常好的学习案例。

在这里,我们想特别强调一下这个处理器适合初学者学习的优势。由于这个处理器的结构简单、代码清晰,通过学习和阅读处理器的代码,初学者可以深入了解和理解RISC-V架构的设计原理和工作方式。同时,我们还为读者赠送了RISC-V中文手册和RISC-V指令集文档的中文版本,这些资料将为读者提供更详细和全面的学习依据,帮助他们更好地掌握RISC-V的知识。

综上所述,本文围绕RISC-V 32位单周期处理器CPU展开讨论,介绍了其工程基于Vivado,指令集为RV32I,使用SystemVerilog编写的特点,以及其适合初学者学习的优势。通过学习这个处理器的代码,初学者可以深入了解和理解RISC-V架构的设计原理和工作方式。我们还赠送了RISC-V中文手册和RISC-V指令集文档的中文版本,为读者提供更详细和全面的学习资料。希望这篇文章能够帮助更多人进一步理解和学习RISC-V架构,并在实际应用中发挥出更大的作用。

以上相关代码,程序地址:http://wekup.cn/793298620018.html

543

543

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?