针对电路调试过程中遇到的问题,进行仿真试验。

以下实验结论:在一定条件下,电压较高,MOS管的电阻选择反而要选较小阻值的。

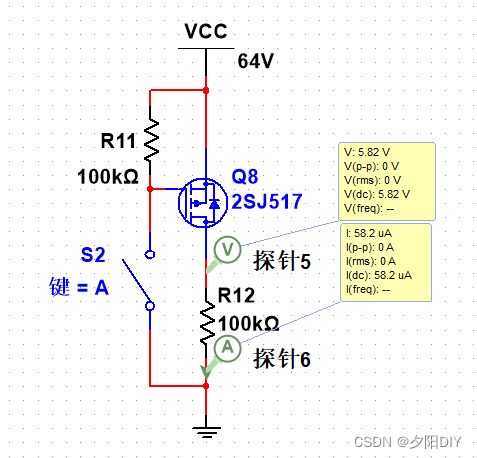

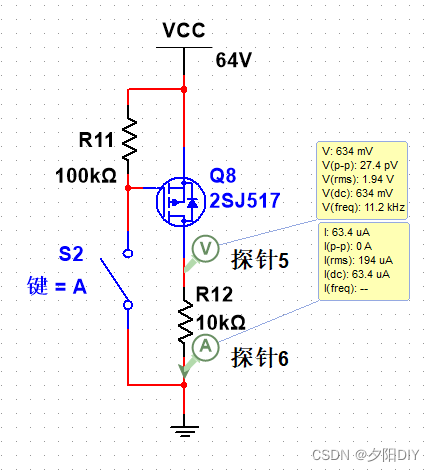

1.PMOS的输出电阻R12对比:

输出电阻100k,漏电压5.82V;输出电阻10k,漏电压0.63V。

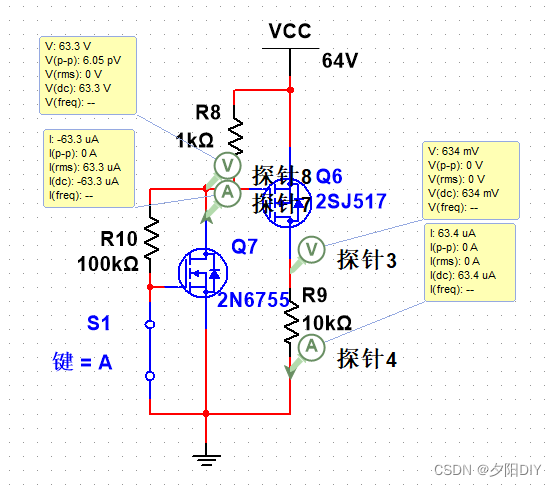

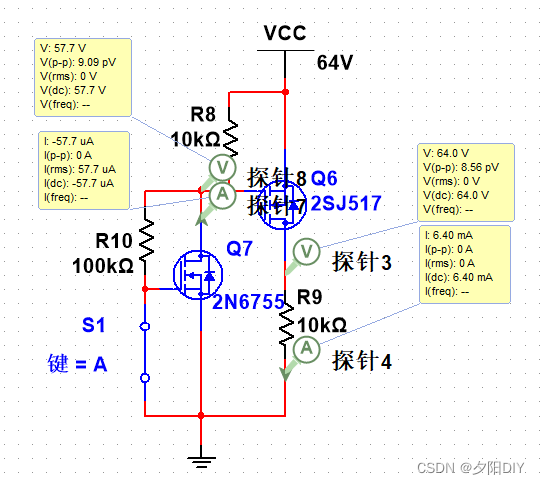

2.二级NMOS上拉电阻R8对比:

上拉电阻1k,PMOS的Vgs为63.3-64=-0.7V,未达到阈值电压-2.5V,未导通,漏电压0.63V;

上拉电阻10k,PMOS的Vgs为57.7-64=-6.3V,超过阈值电压-2.5V,已导通,漏电压64V。

在电路调试中,仿真结果显示,当电压升高时,MOS管的电阻选择应倾向于较小值。例如,PMOS的输出电阻从100k降低到10k,漏电压从5.82V减至0.63V。同样,NMOS的上拉电阻从1k增加到10k,导致PMOS的Vgs超过阈值,从未导通变为导通,漏电压由0.63V升至64V。

在电路调试中,仿真结果显示,当电压升高时,MOS管的电阻选择应倾向于较小值。例如,PMOS的输出电阻从100k降低到10k,漏电压从5.82V减至0.63V。同样,NMOS的上拉电阻从1k增加到10k,导致PMOS的Vgs超过阈值,从未导通变为导通,漏电压由0.63V升至64V。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?