实验原理

理论原理

超声波原理:

HC-SR04超声波测距模块可提供 2cm-400cm的非接触式距离感测功能,测距精度可达高到 3mm;模块包括超声波发射器、接收器与控制电路。图1为HC-SR04外观,其基本工作原理为给予此超声波测距模块触发信号后模块发射超声波,当超声波投射到物体而反射回来时,模块输出回响信号,以触发信号和回响信号间的时间差,来判定物体的距离。

硬件时序模块

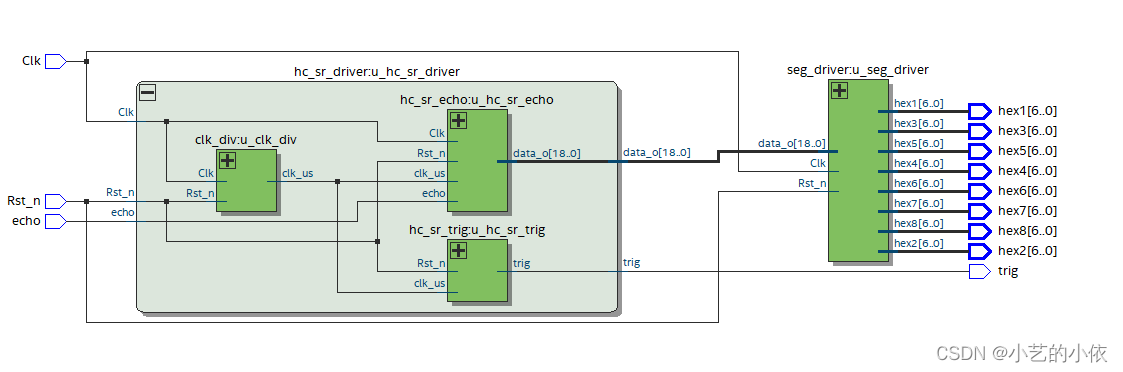

系统架构设计

模块说明

这里要求超声波模块的正负极分别接入5V和GND,其余trigger和echo自由接线,我这里使用的是GPIO[0]和GPIO[1]

设计文件

clk_div.v

module clk_div(

input wire Clk , //system clock 50MHz

input wire Rst_n , //reset ,low valid

output wire clk_us //

);

//Parameter Declarations

parameter CNT_MAX = 19'd50;//1us的计数值为 50 * Tclk(20ns)

//Interrnal wire/reg declarations

reg [5:00] cnt ; //Counter

wire add_cnt ; //Counter Enable

wire end_cnt ; //Counter Reset

//Logic Description

always @(posedge Clk or negedge Rst_n)begin

if(!Rst_n)begin

cnt <= 'd0;

end

else if(add_cnt)begin

if(end_cnt)begin

cnt <= 'd0;

end

else begin

cnt <= cnt + 1'b1;

end

end

else begin

cnt <= cnt;

end

end

assign add_cnt = 1'b1;

assign end_cnt = add_cnt && cnt >= CNT_MAX - 19'd1;

assign clk_us = end_cnt;

endmodule

hc_sr_trig.v

module hc_sr_trig(

input wire clk_us , //system clock 1MHz

input wire Rst_n , //reset ,low valid

output wire trig //触发测距信号

);

//Parameter Declarations

parameter CYCLE_MAX = 19'd300_000;

//Interrnal wire/reg declarations

reg [18:00] cnt ; //Counter

wire add_cnt ; //Counter Enable

wire end_cnt ; //Counter Reset

//Logic Description

always @(posedge clk_us or negedge Rst_n)begin

if(!Rst_n)begin

cnt <= 'd0;

end

else if(add_cnt)begin

if(end_cnt)begin

cnt <= 'd0;

end

else begin

cnt <= cnt + 1'b1;

end

end

else begin

cnt <= cnt;

end

end

assign add_cnt = 1'b1;

assign end_cnt = add_cnt && cnt >= CYCLE_MAX - 9'd1;

assign trig = cnt < 15 ? 1'b1 : 1'b0;

endmodule

hc_sr_echo.v

module hc_sr_echo(

input wire Clk , //clock 50MHz

input wire clk_us , //system clock 1MHz

input wire Rst_n , //reset ,low valid

input wire echo , //

output wire [18:00] data_o //检测距离,保留3位小数,*1000实现

);

/* S(um) = 17 * t --> x.abc cm */

//Parameter Declarations

parameter T_MAX = 16'd60_000;//510cm 对应计数值

//Interrnal wire/reg declarations

reg r1_echo,r2_echo; //边沿检测

wire echo_pos,echo_neg; //

reg [15:00] cnt ; //Counter

wire add_cnt ; //Counter Enable

wire end_cnt ; //Counter Reset

reg [18:00] data_r ;

//Logic Description

//如果使用clk_us 检测边沿,延时2us,差值过大

always @(posedge Clk or negedge Rst_n)begin

if(!Rst_n)begin

r1_echo <= 1'b0;

r2_echo <= 1'b0;

end

else begin

r1_echo <= echo;

r2_echo <= r1_echo;

end

end

assign echo_pos = r1_echo & ~r2_echo;

assign echo_neg = ~r1_echo & r2_echo;

always @(posedge clk_us or negedge Rst_n)begin

if(!Rst_n)begin

cnt <= 'd0;

end

else if(add_cnt)begin

if(end_cnt)begin

cnt <= cnt;

end

else begin

cnt <= cnt + 1'b1;

end

end

else begin //echo 低电平 归零

cnt <= 'd0;

end

end

assign add_cnt = echo;

assign end_cnt = add_cnt && cnt >= T_MAX - 1; //超出最大测量范围则保持不变,极限

always @(posedge Clk or negedge Rst_n)begin

if(!Rst_n)begin

data_r <= 'd2;

end

else if(echo_neg)begin

data_r <= (cnt << 4) + cnt;

end

else begin

data_r <= data_r;

end

end //always end

assign data_o = data_r >> 1;

endmodule

hc_sr_driver .v

module hc_sr_driver (

input wire Clk ,

input wire Rst_n ,

input wire echo ,

output wire trig ,

output wire [18:0] data_o

);

wire clk_us;

hc_sr_echo u_hc_sr_echo(

.Clk (Clk ), //clock 50MHz

.clk_us (clk_us ), //system clock 1MHz

.Rst_n (Rst_n ), //reset ,low valid

.echo (echo ), //

.data_o (data_o ) //检测距离,保留3位小数,*1000实现

);

hc_sr_trig u_hc_sr_trig(

.clk_us (clk_us ), //system clock 1MHz

.Rst_n (Rst_n ), //reset ,low valid

.trig (trig )//触发测距信号

);

clk_div u_clk_div(

.Clk (Clk ), //system clock 50MHz

.Rst_n (Rst_n ), //reset ,low valid

.clk_us (clk_us )//

);

endmodule

seg_driver.v

module seg_driver(

input wire Clk ,

input wire Rst_n ,

input wire [18:0] data_o ,

output wire [6:0] hex1 ,

output wire [6:0] hex2 ,

output wire [6:0] hex3 ,

output wire [6:0] hex4 ,

output wire [6:0] hex5 ,

output wire [6:0] hex6 ,

output wire [6:0] hex7 ,

output wire [6:0] hex8

);

parameter NOTION = 4'd10,

FUSHU = 4'd11;

parameter MAX20us = 10'd1000;

reg [9:0] cnt_20us;

reg [7:0] sel_r;

reg [3:0] number;

reg [6:0] seg_r;

reg [6:0] hex1_r;

reg [6:0] hex2_r;

reg [6:0] hex3_r;

reg [6:0] hex4_r;

reg [6:0] hex5_r;

reg [6:0] hex6_r;

reg [6:0] hex7_r;

reg [6:0] hex8_r;

//20微妙计数器

always @(posedge Clk or negedge Rst_n) begin

if (!Rst_n) begin

cnt_20us <= 10'd0;

end

else if (cnt_20us == MAX20us - 1'd1) begin

cnt_20us <= 10'd0;

end

else begin

cnt_20us <= cnt_20us + 1'd1;

end

end

//单个信号sel_r位拼接约束

always @(posedge Clk or negedge Rst_n) begin

if (!Rst_n) begin

sel_r <= 8'b11_11_11_10;

end

else if (cnt_20us == MAX20us - 1'd1) begin

sel_r <= {sel_r[6:0],sel_r[7]};

end

else begin

sel_r <= sel_r;

end

end

/*拿到数字*/

always @(*) begin

case (sel_r)

8'b11_11_11_10: number = NOTION ;

8'b11_11_11_01: number = data_o/10_0000 ;

8'b11_11_10_11: number = (data_o%10_0000)/1_0000 ;

8'b11_11_01_11: number = ((data_o%10_0000)%1_0000)/1000 ;

8'b11_10_11_11: number = FUSHU ;

8'b11_01_11_11: number = (((data_o%10_0000)%1_0000)%1000)/100 ;

8'b10_11_11_11: number = ((((data_o%10_0000)%1_0000)%1000)%100)/10 ;

8'b01_11_11_11: number = ((((data_o%10_0000)%1_0000)%1000)%100)%10 ;

default: number = 4'd0 ;

endcase

end

/*通过数字解析出seg值*/

always @(*) begin

case (number)

4'd0 : seg_r = 7'b100_0000;

4'd1 : seg_r = 7'b111_1001;

4'd2 : seg_r = 7'b010_0100;

4'd3 : seg_r = 7'b011_0000;

4'd4 : seg_r = 7'b001_1001;

4'd5 : seg_r = 7'b001_0010;

4'd6 : seg_r = 7'b000_0010;

4'd7 : seg_r = 7'b111_1000;

4'd8 : seg_r = 7'b000_0000;

4'd9 : seg_r = 7'b001_0000;

NOTION : seg_r = 7'b111_1111;

FUSHU : seg_r = 7'b011_1111;

default : seg_r = 7'b111_1111;

endcase

end

always @(*) begin

case (sel_r)

8'b11_11_11_10: hex1_r = seg_r;

8'b11_11_11_01: hex2_r = seg_r;

8'b11_11_10_11: hex3_r = seg_r;

8'b11_11_01_11: hex4_r = seg_r;

8'b11_10_11_11: hex5_r = seg_r;

8'b11_01_11_11: hex6_r = seg_r;

8'b10_11_11_11: hex7_r = seg_r;

8'b01_11_11_11: hex8_r = seg_r;

default: seg_r = seg_r;

endcase

end

assign hex1 = hex1_r;

assign hex2 = hex2_r;

assign hex3 = hex3_r;

assign hex4 = hex4_r;

assign hex5 = hex5_r;

assign hex6 = hex6_r;

assign hex7 = hex7_r;

assign hex8 = hex8_r;

endmodule

hc_sr_top.v

module hc_sr_top (

input wire Clk ,

input wire Rst_n ,

input wire echo ,

output wire trig ,

output wire [6:0] hex1 ,

output wire [6:0] hex2 ,

output wire [6:0] hex3 ,

output wire [6:0] hex4 ,

output wire [6:0] hex5 ,

output wire [6:0] hex6 ,

output wire [6:0] hex7 ,

output wire [6:0] hex8

);

wire [18:0] data_o;

hc_sr_driver u_hc_sr_driver(

.Clk (Clk ),

.Rst_n (Rst_n ),

.echo (echo ),

.trig (trig ),

.data_o (data_o )

);

seg_driver u_seg_driver(

.Clk (Clk ),

.Rst_n (Rst_n ),

.data_o (data_o ),

.hex1 (hex1),

.hex2 (hex2),

.hex3 (hex3),

.hex4 (hex4),

.hex5 (hex5),

.hex6 (hex6),

.hex7 (hex7),

.hex8 (hex8)

);

endmodule

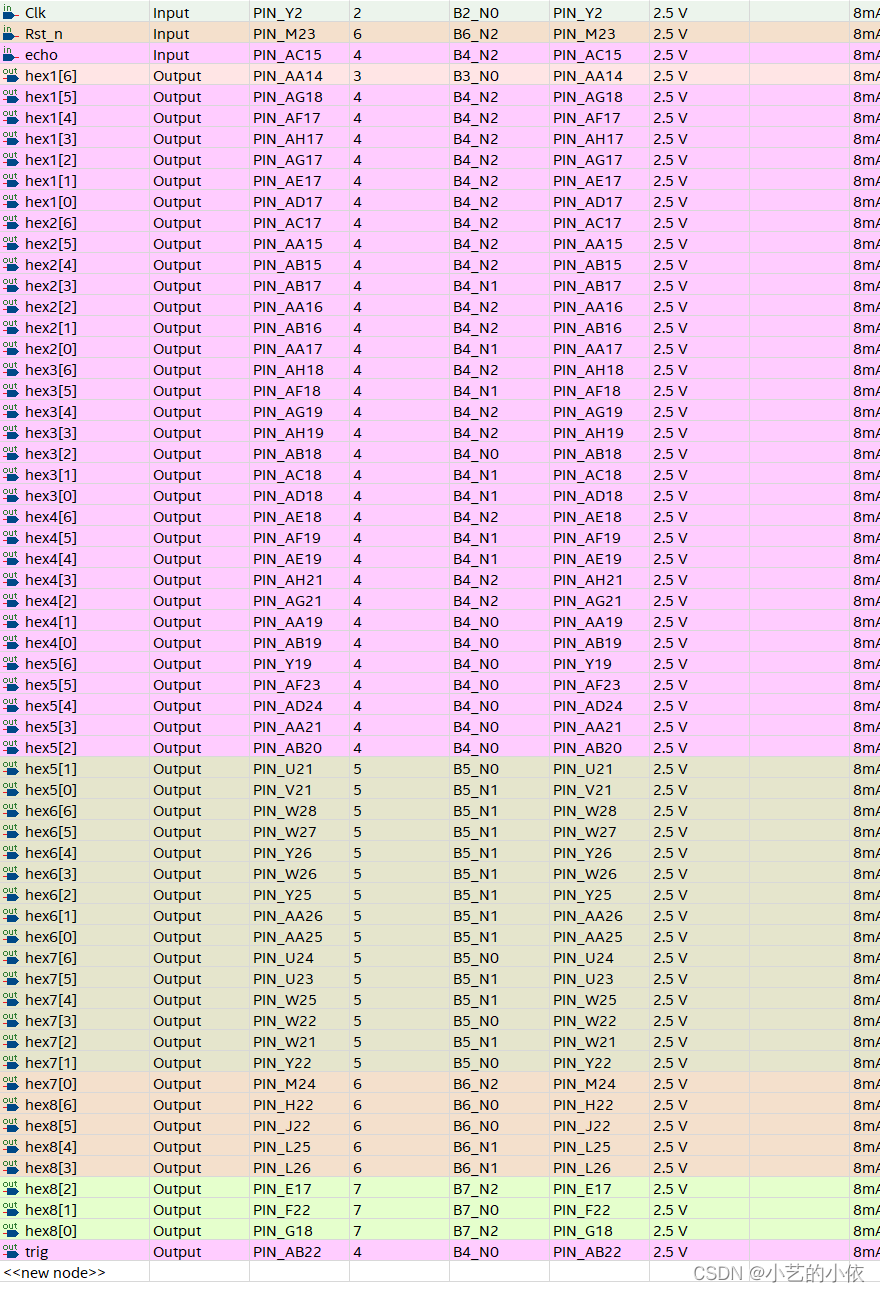

上板

首先这里提出引脚配置,其中trig和echo引脚与自己所接线的位置向同即可

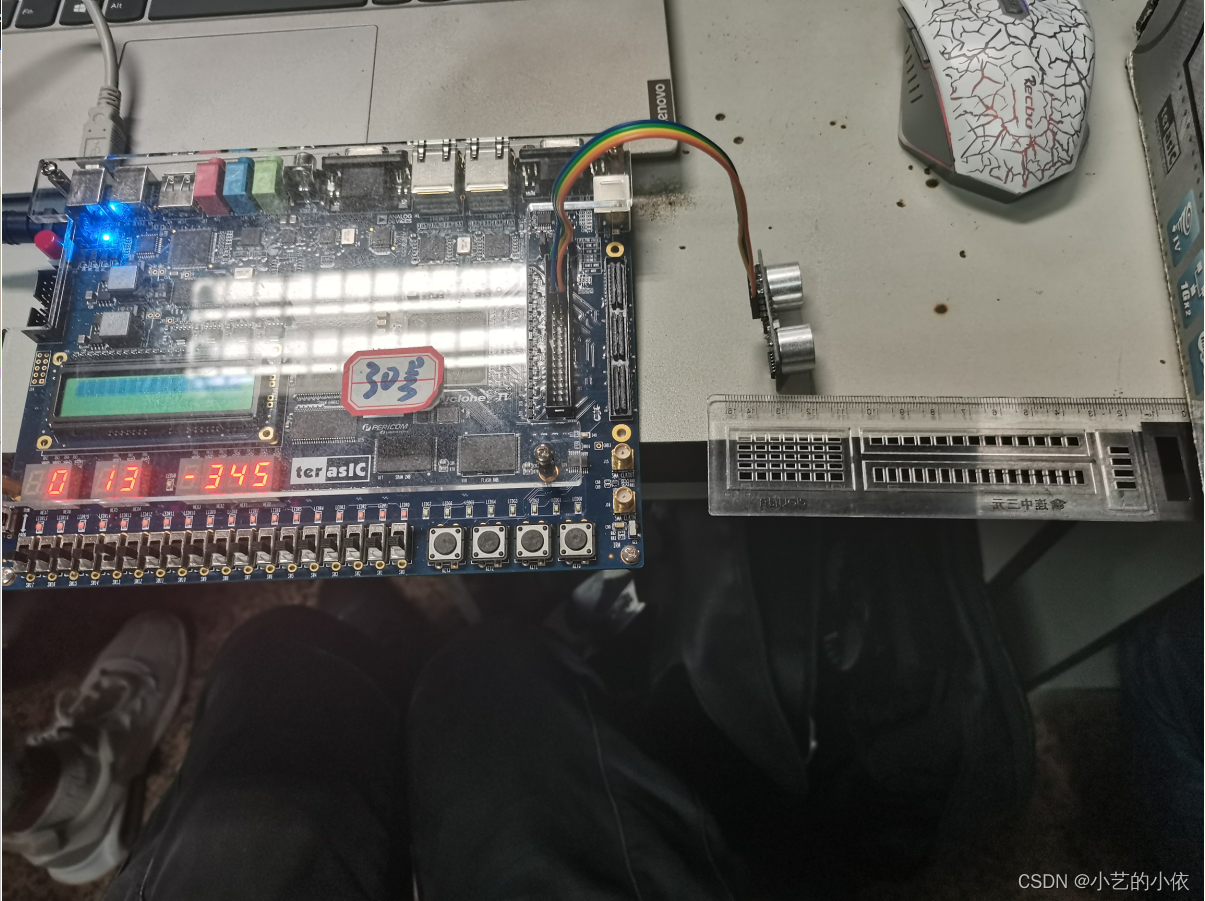

可见所测距离与实际距离一致,可见功能基本实现。

总结

本次测试借用了一些学长的代码,也带有自己的一些思考,补全了学长没有写进代码的部分。由于代码中设计的寄存器只有那么多位数,也和驱动本身的下限,决定了这次设计只能测试大概4~247cm左右的距离。能够自己补全一部分代码,对于我来说还是很有成就感的,下次见

1878

1878

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?