摘要:对Aurora ip 核进行介绍,并对IP进行仿真。写的不一定全对,自行斟酌。

1. Aurora

Aurora ip比较简单,当然简单指的是这个IP的使用。它的核心原理以及实现是比较复杂的。

那么实际使用的时候只需要注意时钟、复位、数据发送接收等即可。

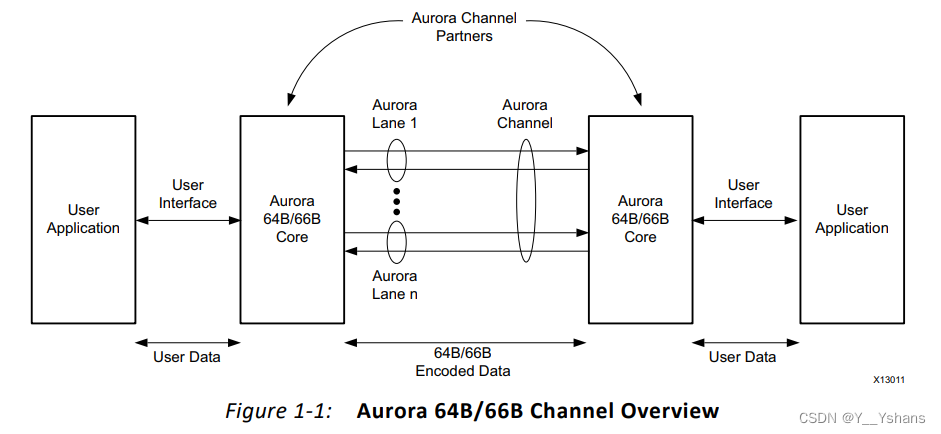

Xilinx提供了两个Aurora核,分别是:Aurora 8B/10B 以及Aurora 64B/66B。

顾名思义,主要是8B/10B ,64B/66B的区别;8B/10B编码可以平衡DC,有足够的跳变来恢复时钟,但是有20%的带宽开销。64B/66B编码的前两位表示同步头,减小的开销,但是却不能保证0/1数量的平衡,因此需要进行加扰。

本文以64B/66B为例

1.1 Aurora ip

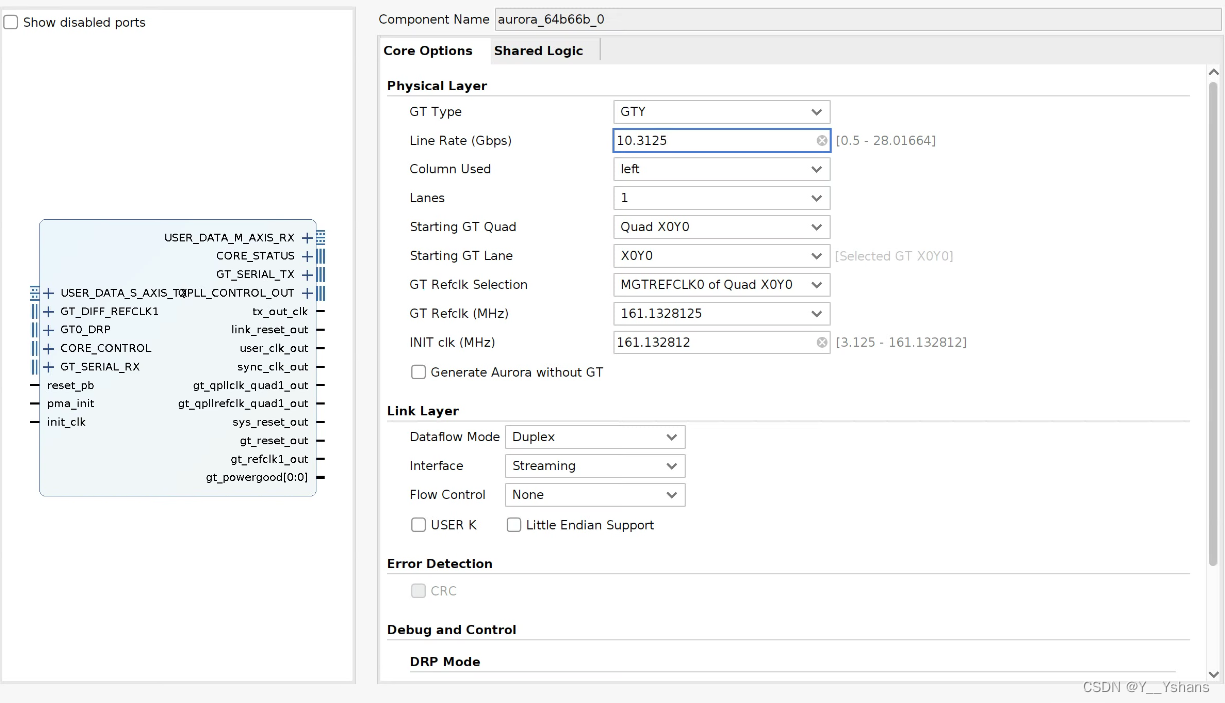

我这边使用的配置是这样,DRP选择native,shared logic里面直接选择Include shared logic in core(xilinx example design是这么选择的)

个人感觉只用在意Line Rate、GT Refclk、INIT clk就好,其它的设置比较简单,按照自己实际工程需求来,不明白什么意思直接到PG074里面搜。

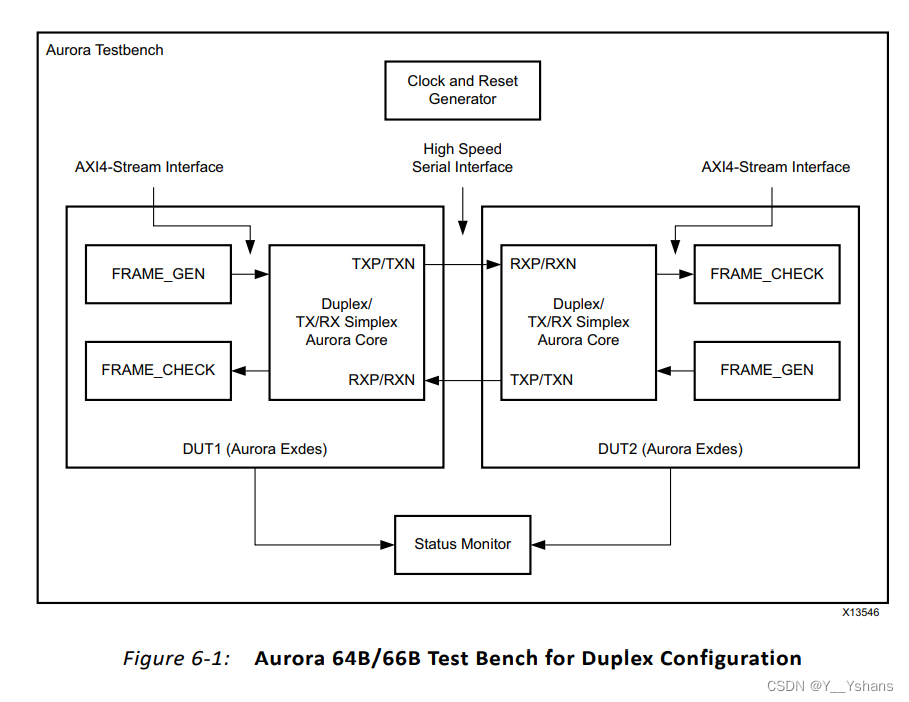

xilinx example design提供了工程仿真,这个仿真也没有错误,直接可以运行起来。下面是example design的框图:

实际使用中,我需要将两块板子进行通信,用Aurora通过高速接口serdes传输数据。两块板子需要用到两个Aurora,两个Aurora配置相同。

GEN模块就是产生数据的模块,check的模块是检验接受数据是否正确的模块。gen模块按照一定的规则输出数据,check模块也按照同样的规则产生数据,产生的数据与接受到的数据进行对比从而验证整个传输过程中有没有错误(用tready和tvalid实现同步)。

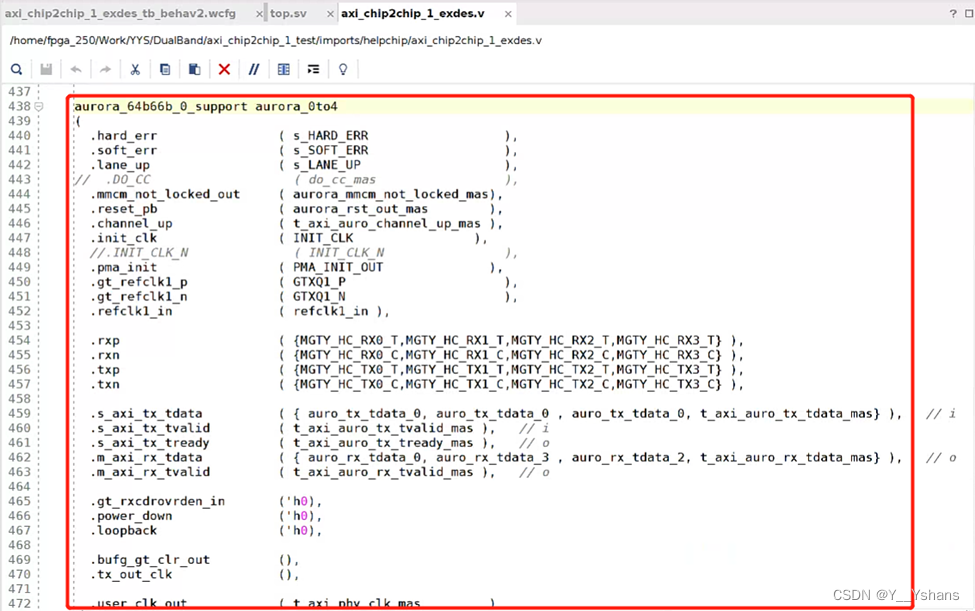

| 信号 | 描述 |

| hard_err soft_err | |

| Lane_up | 表示aurora的一个或多个通道的状态 |

| mmcm_not_locked_out | 与chip2chip直连 |

| reset_pb | 和chip2chip直连 |

| channel_up | 表明link状态 |

| init_clk pma_init | 100Mhz |

| refclk1_in | 单端161.XXXXMhz |

| s_axi_tx_tdata s_axi_tx_tvalid s_axi_tx_tready s_axi_rx_tdata s_axi_rx_tvalid | 数据传输 |

| user_clk_out | 402.832031Mhz,数据传输要用的钟 |

一般关注两个信号看看Aurora是否正常工作:channel up、lane up。

lane_up为1表示收发器之间的通信链路训练成功。

channel_UP为1表示验证序列成功。

而且一般情况下,只要aurora时钟复位都是对的,并且两边aurora的配置也是对的,那么直接就link了,一般不会出现其它的问题。我碰到的最多的就是时钟没有接好,导致link不上。

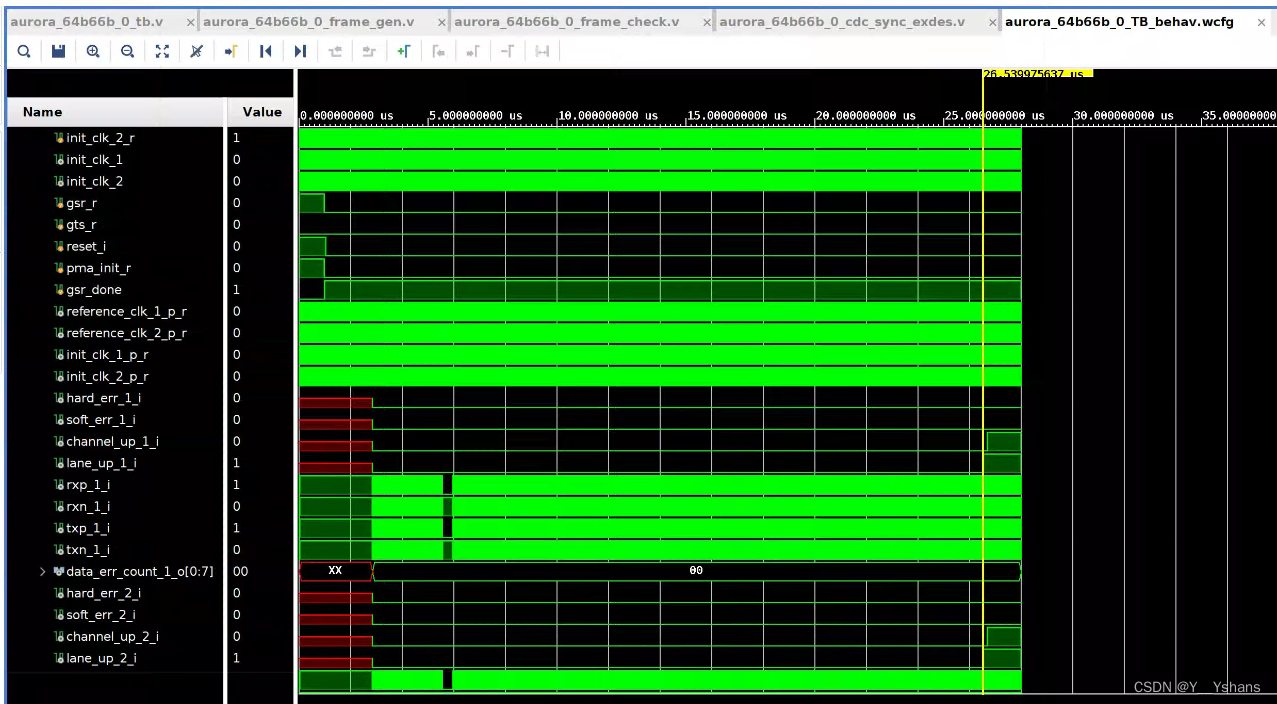

仿真的时候可以直接将发射端或者接收端的txp、rxp短接可以直接验证回环(实际上板验证的时候单个板子只能通过物理回环)不会有任何报错,但是chip2chip不行。或者通过检查check error判断是否有数据传输错误。

整个代码都比较简单,都是xilinx提供的代码。

总结

需要仿真的话,建议看4个Lane的Aurora仿真+chip2chip+ethernet

这里面的仿真比较全,而且经过少量修改可以直接在实际中使用。

参考文章:

Xilinx平台Aurora IP介绍(汇总篇)_子墨祭的博客-CSDN博客_aurora ip

Xilinx平台Aurora IP介绍(一)Aurora基础知识_子墨祭的博客-CSDN博客

Xilinx平台Aurora IP介绍(二)时钟与复位_子墨祭的博客-CSDN博客_xilinx aurora

Xilinx平台Aurora IP介绍(四)Example Design介绍_子墨祭的博客-CSDN博客

Xilinx平台Aurora IP介绍(五)数据收发测试_子墨祭的博客-CSDN博客

PG074 Aurora 64B/66B v12.0

https://download.csdn.net/download/Y__Yshans/86892336?spm=1001.2014.3001.5501

https://download.csdn.net/download/Y__Yshans/87484631?spm=1001.2014.3001.5501

本文介绍了Aurora IP核,Xilinx提供Aurora 8B/10B和Aurora 64B/66B两个核,以64B/66B为例说明使用配置。讲述了用Aurora通过高速接口传输数据的方法,以及验证传输是否正常的方式。最后建议参考4个Lane的Aurora仿真等内容。

本文介绍了Aurora IP核,Xilinx提供Aurora 8B/10B和Aurora 64B/66B两个核,以64B/66B为例说明使用配置。讲述了用Aurora通过高速接口传输数据的方法,以及验证传输是否正常的方式。最后建议参考4个Lane的Aurora仿真等内容。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?