版权声明:转载请注明出处:http://blog.csdn.net/lg2lh

一、锁存器

首先设计锁存器的时候应该清楚什么是锁存器,锁存器其实是对电平信号敏感的,一定信号是电平敏感的,和时钟边沿clk无关。

所以用verilog描述的时候,应该是:

产生锁存器的原因是因为各条件分支对dout的赋值不全,在else分支内没有对dout操作,这样就会造成锁存器。

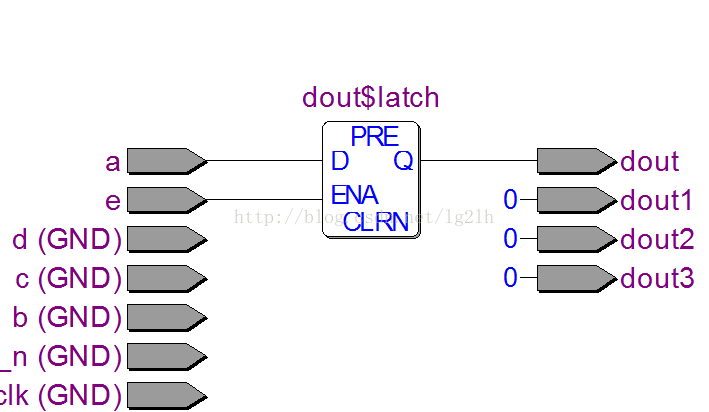

实际综合后的RTL视图,可以看到综合后出现了锁存器latch

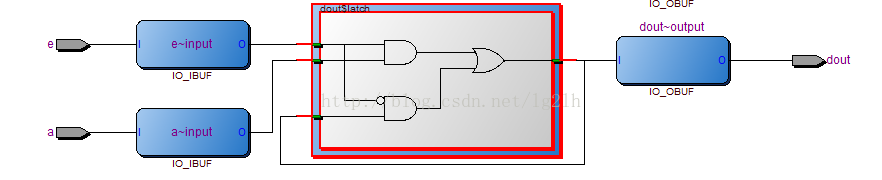

而从Technology Map View可以看出该锁存器的结构:

实际从FPGA逻辑资源实现上采用了逻辑门实现的,可见FPGA内部一般是没有锁存器这样的单元的。

二、触发器

首先明白触发器敏感信号时时钟边沿, 在Verilog中表述是这样的

其RTL视图为一个触发器:

而从Technology Map View可以看出FPGA内部实际是有触发器资源的。

三、避免锁存器

在(一)中可以看到对于dout分支不全造成了锁存器。下面再分析一例程序

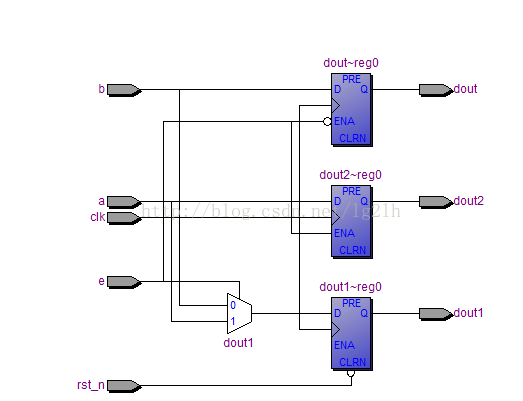

RTL视图为:包含两个锁存器和一个触发器。

分析:虽然下面的alway里分支都有(if else都有)但是每个分支只对其中一个寄存器赋值,再另一分支中没有再对相应寄存器赋值。

所以对于dout2和dout都形成了锁存器。

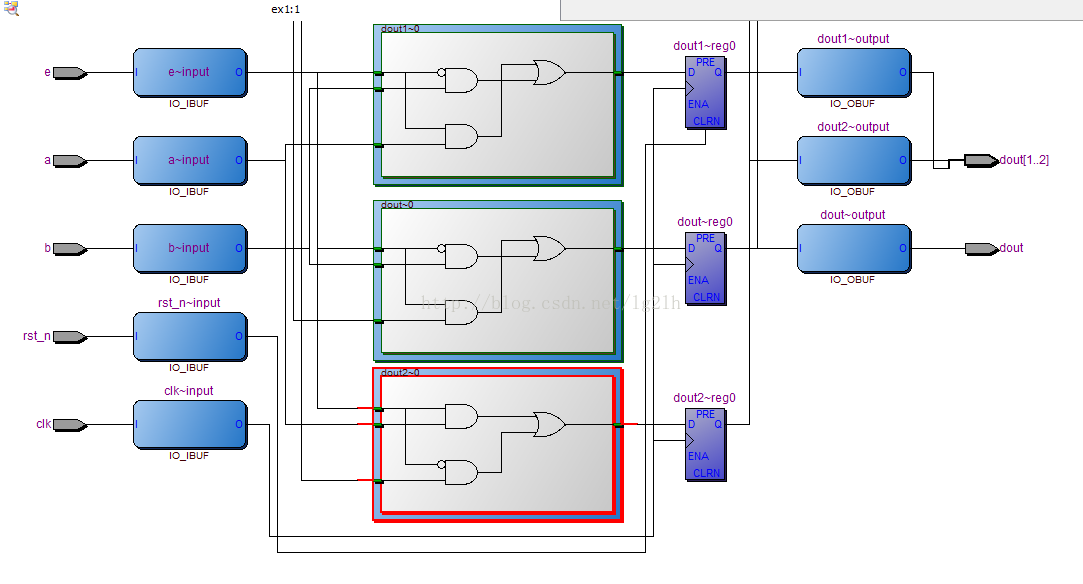

再看Technology Map View视图:

分析:图中下面两个位锁存器的结构,可以看出,锁存器是有反馈回路的逻辑电路,如图中标红的线为反馈信号。

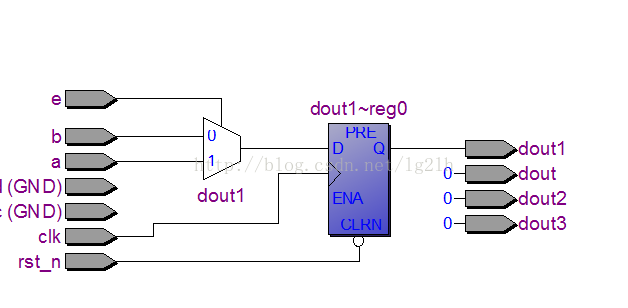

为了尽量避免锁存器,改为触发器,修改语句:

图示为修改后的RTL视图,把分支赋值全了,可以看到锁存器没有了,变成了触发器

再看Technology Map View视图:

分析:锁存器消失

缺点:时序分析较困难。

不要锁存器的原因有二:

1、锁存器容易产生毛刺,

2、锁存器在ASIC(专用集成电路)设计中应该说比ff(触发器)要简单,但是在FPGA的资源中,大部分器件没有锁存器这个东西,所以需要用一个逻辑门和ff

来组成锁存器,这样就浪费了资源。(用CPLD(复杂可编程逻辑器件)和FPGA(现场可编程逻辑阵列)来进行ASIC设计是最为流行的方式之一)

优点:面积小。锁存器比FF快,所以用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得

CPU的速度比外部IO部件逻辑快许多。latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

440

440

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?