开题先来看下这几个差异:

时钟震荡器就是常说的Clock Oscillator。时钟震荡器(Oscillator)本身可以产生频率源的,它的主要作用是产生频率源。

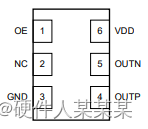

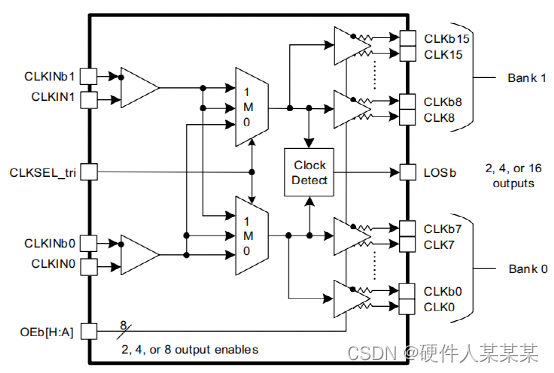

时钟缓冲器就是常说的Clock Buffer。时钟缓冲器(Buffer)本身是无法产生频率源的,它的主要作用是将晶体或晶振产生的时钟信号进行复制、格式转换及电平转换。

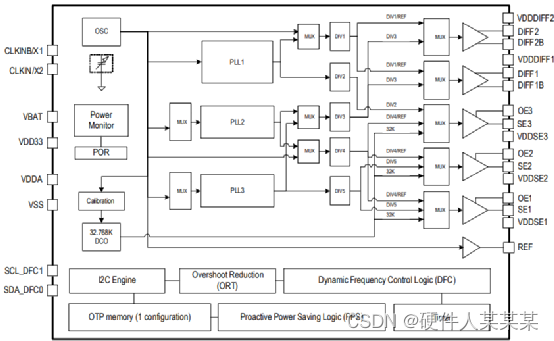

时钟发生器就是常说的Clock Generator。时钟发生器(Generator)搭配外部石英晶体或单端或差分时钟作为参考频率,可产生具有严格公差限制的时钟输出频率。 它的主要作用是生成低抖动输出时钟,频率的多份拷贝来驱动多个负载,可通过乘法或除法方式实现频率转换,提供具有单端和差分时钟输出。

主要器件厂商

clock oscillator,generator,buffer芯片厂商:

美国TI、Skyworks(原silicon lab时钟业务)、Diodes、Microchip;日本Renesas(收购IDT);中国香港Aura、无锡有容微。

选型参数以及目的:

clock oscillator,generator,buffer最终的目的就是为系统提供合适的时钟,那么什么是合适的时钟?

从大方面来讲主要有如下参数:

电平:如CMOS、LVCMOS、LVPECL、LVDS、HCSL等等。

频率:如32.768KHz、25MHz、33MHz、48MHz、100MHz、125MHz、156.25MHz等等。

频率稳定度:通常为±10~±30ppm,越小越好。

占空比:通常为50%±5%或者是50%±10%。

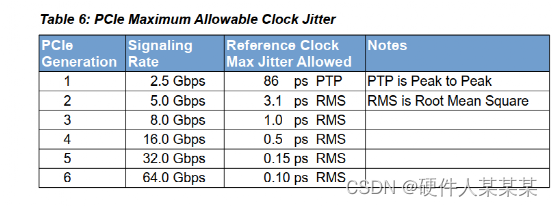

抖动:如PCIE的抖动要求

总结:要想得到更好的时钟,就必须从使用场景的数据指标要求入手,选择适配这些指标的时钟方案即可。

电平,频率,频率稳定度,占空比,抖动这些参数新手工程师通常只关注频率,而把其他参数忽略了。这是一个很严重的问题,因为时钟跟电源一样,是一个系统的根基,根基没做好,楼肯定盖不高、盖不好。

今天咋们这里就挑个抖动来说说:

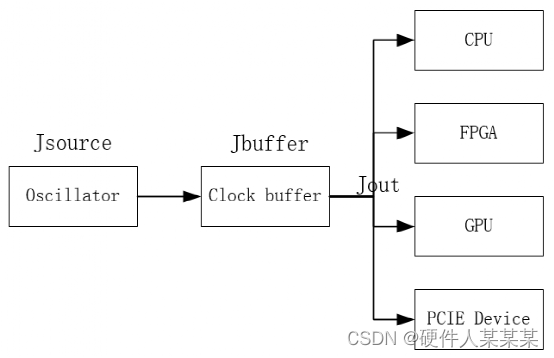

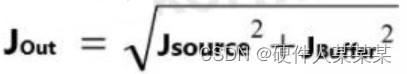

从上图来看,配合下面输出抖动计算方法,

可知:

给到系统设备使用的时钟抖动主要受振荡器的抖动以及时钟buffer的抖动影响。

Jout是否满足系统器件的要求?这是我们要关心的最终结果。

如果不满足,可通过选择更低抖动的振荡器以及时钟buffer;如果是多级时钟架构,可改版降低级数,这也是我们设计时候就要考虑的事情,尽量不要采用多级时钟。

文章详细介绍了时钟震荡器、时钟缓冲器和时钟发生器的功能与区别,强调了在选择时钟组件时,除了关注频率外,电平、频率稳定度、占空比和抖动等参数同样重要。特别提到抖动对系统性能的影响,并指出应根据系统需求选择低抖动的组件,避免多级时钟架构以优化设计。

文章详细介绍了时钟震荡器、时钟缓冲器和时钟发生器的功能与区别,强调了在选择时钟组件时,除了关注频率外,电平、频率稳定度、占空比和抖动等参数同样重要。特别提到抖动对系统性能的影响,并指出应根据系统需求选择低抖动的组件,避免多级时钟架构以优化设计。

3846

3846

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?