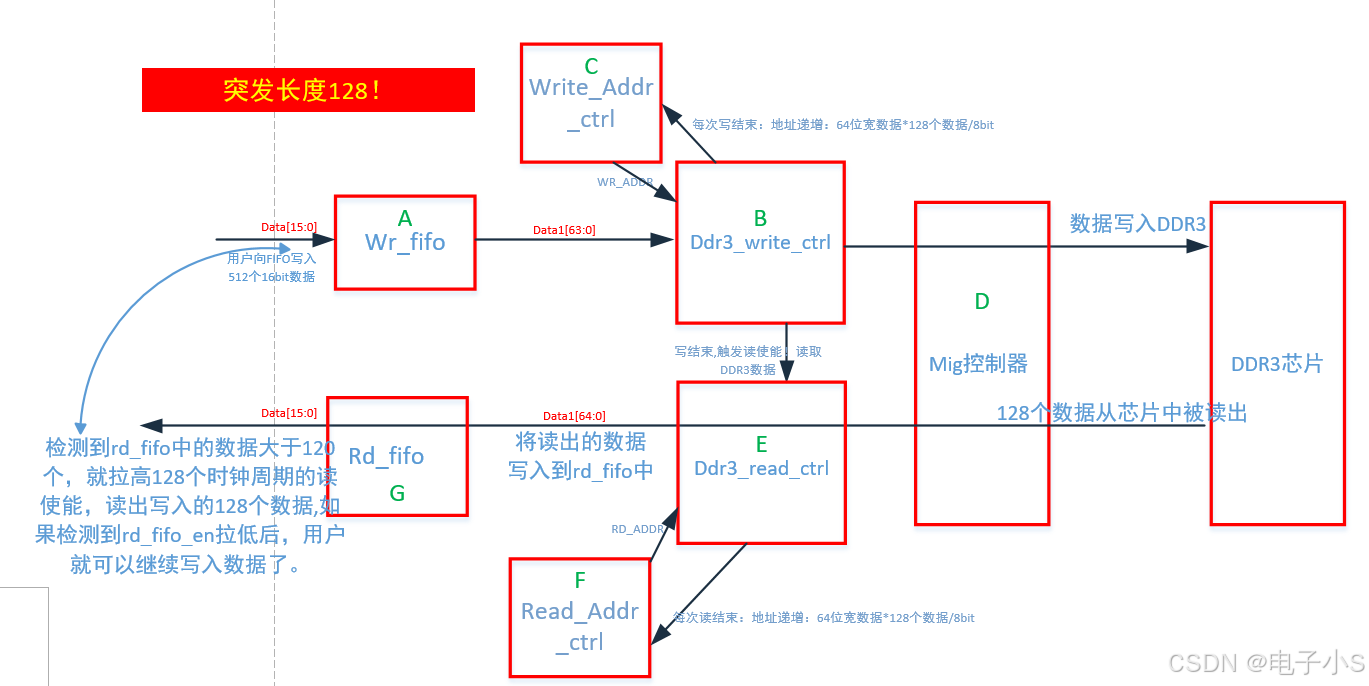

实验目标:写入512个16bit的数据到DDR3中!然后再将其读出来!(AXI总线位宽64位宽,突发长度128).图1是思维导体!(里面很多参数可以改的,我以突发128为例!)

图1 总体思维导图

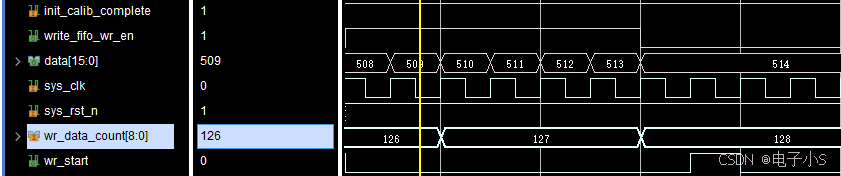

首先等Mig的初始化信号init_calib_complete信号拉高(大概100us左右)。然后开始实现图1绿色字体的A部分:我向fifo中写入了512个数据(从2写到了513)!仿真如图2所示!

图2

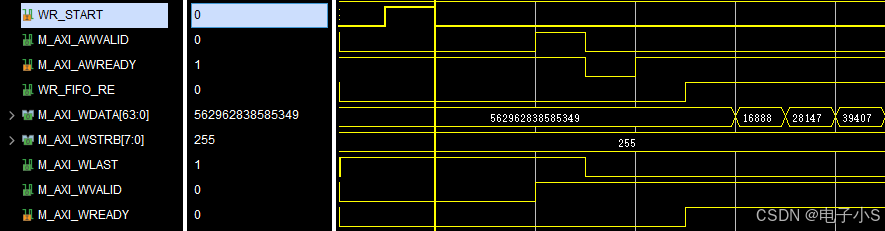

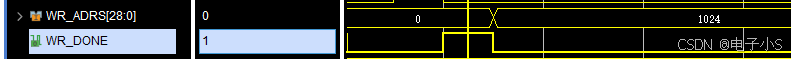

在图2中,写入了512个16位宽数据后,wr_data_count计数器显示可以读取的数有128个(64位宽的数据),同时wr_start信号拉高,表明要将128个64位宽的数通过B模块写入到ddr3中(如图3所示),写入DDR3后结束后,同时进行地址的更新(初始地址0+1024)(图3)。写结束后fifo中的计数器也变空了!

图3

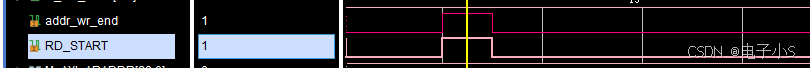

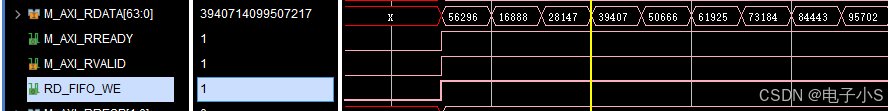

检测到写结束信号后,同时拉高读开始信号(图4),使用E模块将DDR3的128个数据读出放入到RD_fifo中!

图4

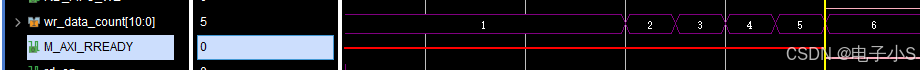

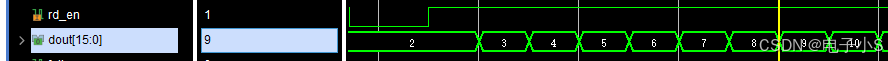

然后检测RD_FIFO中的数据量是否大于120(为什么不等于128呢?因为的在axi_read模块中声明rd_fifo_rd_en =M_AXI_READY,M_AXI_READY刚开始要初始化,属于高阻态,会扰乱fifo计数器里的值),大于话就把里面数给输出出来给用户。 然后拉高rd_fifo_en 512个时钟周期就可以读出里面的值了。

图5 由于高阻态导致的wr_data_count计数器的值紊乱(写使能没拉高就有值)

下面图6是用户读出的数据从2读到了513!

图6 读出写入DDR3的512个数据

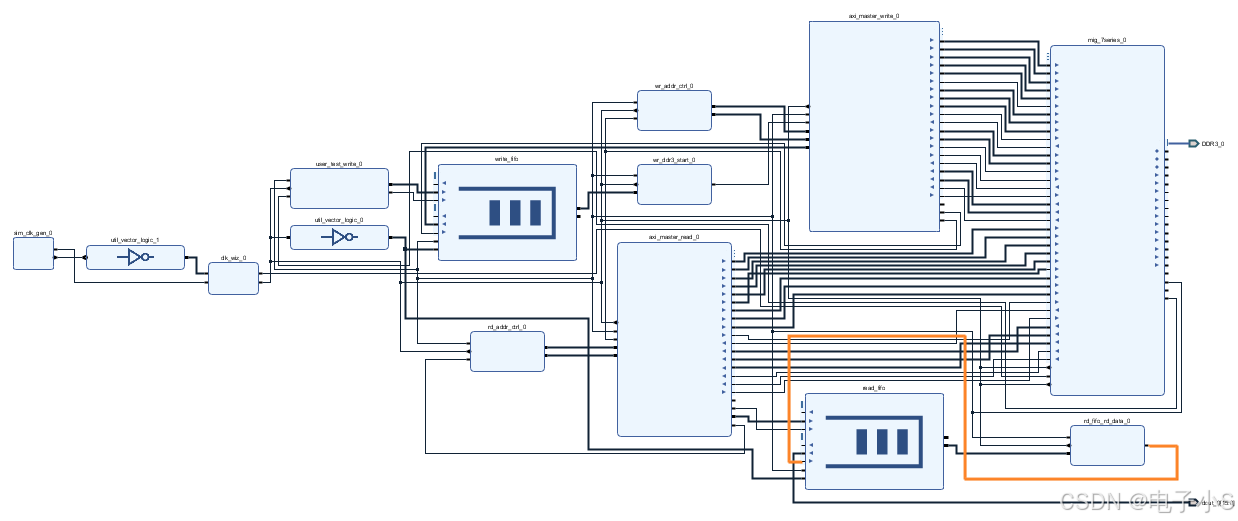

大功告成!(下面放一个我的block_design),我全部都是以ip核的形式做的,自己封装了很多ip核,实在不想一个一个去例化连接了!!!

图7 vivado_block_design

9831

9831

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?