PCIe 3.0设计面对的挑战

PCIe由PCI-SIG协会研发和维护的一个高速标准接口,PCIe3.0是其开发的第三代接口高速差分接口,其单个差分对信号速率可到达8.0Gbps,目前其以广泛的应用于计算机服务器等设备领域。

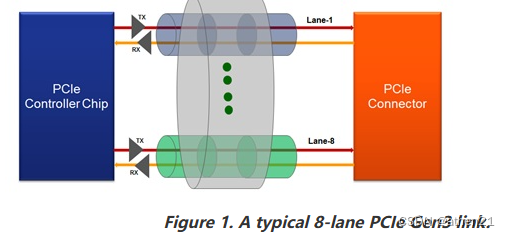

下图显示的是一个典型的PCIe Gen3的链接结构。PCIe 3.0 的连接通道可以由不同的位宽组成,其支持x1, x4, x8, x12, x16, and x32。由于有高达8Gbps的信号速率,因此一些物理效应会给信号的传输带来给大的挑战。串扰,阻抗不连续引起的反射会造成Jitter, ISI,模态转化等问题。

如何应对挑战

为了解决上述问题, 在一般的相关设计中,需要使用仿真的方法来确认设计是否满足接口的相关规格。一般会对眼图特性及误码率进行仿真。

在高速的串行通道仿真中,需要使用到IBIS-AMI模型进行不同的参数仿真。IBIS-AMI模型可以对多位千兆接口进行快速,准确的进行统计方法上的电路仿真。

通常我们利用IBIS-AMI模型发射器及接收器与提取到的通道模型进行结合,在接收器生成眼图。再根据PCIe3.0规范里的眼图模板与眼图相比较。

具体而言,对于PCIe接口的信真方法有如下几个部分:

通道仿真

这里介绍的方法为瞬态仿真,其长度由通道损耗及反射所决定。为了应对克服信号完整性的问题,在PCIe中使用发DFE及FFE。因此在IBIS模型上扩展了IBIS-AMI。

抖动

在串行通信系统中,时钟与传输的数据一起嵌入,时钟数据恢复(CDR)电路用于恢复接收器侧的时钟。锁存正确的数据很大程度上取决于数据和时钟之间的对齐。抖动在误码数量中起着重要作用,可分为随机抖动 (RJ) 和确定性抖动 (DJ)。为了仿真BER的准确估计值,仿真中必须包含这两个抖动元素。

均衡

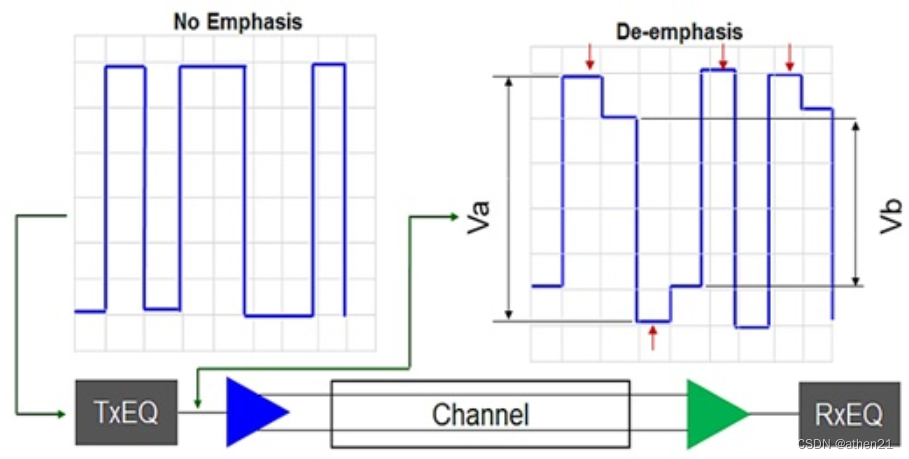

PCIe 3.0 规范包括在发射器和/或接收器处执行均衡的规定。这样做是为了减轻 ISI 的影响,从而最大限度地减少 BER。在均衡中,信号通过频率响应等于通道反频率响应的滤波器。高增益用于抵消较高频率下的信号衰减。也就是说均衡是一种自适应滤波器,其系数取决于运行时,具体取决于物理通道。

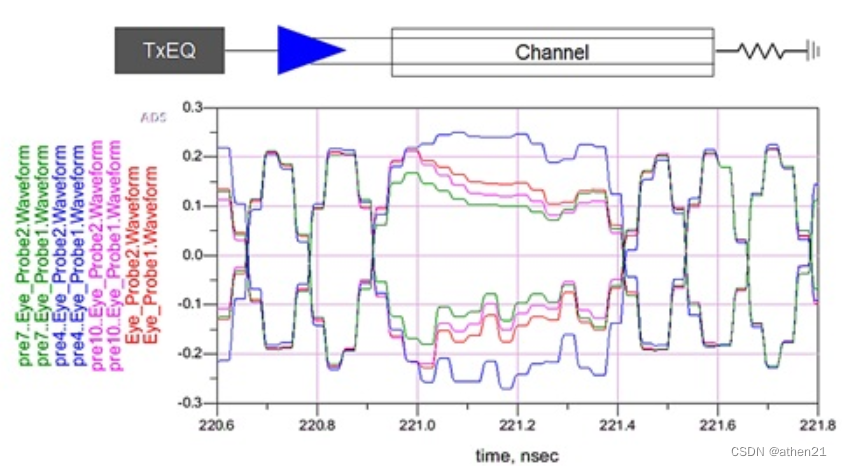

去加重与Pre-Shoot

PCIe使用增加去加重来补偿高频通道损耗。去加重波形由电压电平 Va(去加重)和 Vb(平坦电平)定义。下图显示了将波形使用3抽头FIR滤波器时产生的输出信号。输出在输入位流极性反转之前和之后采用不同的值。

PCIe信号完整性分析

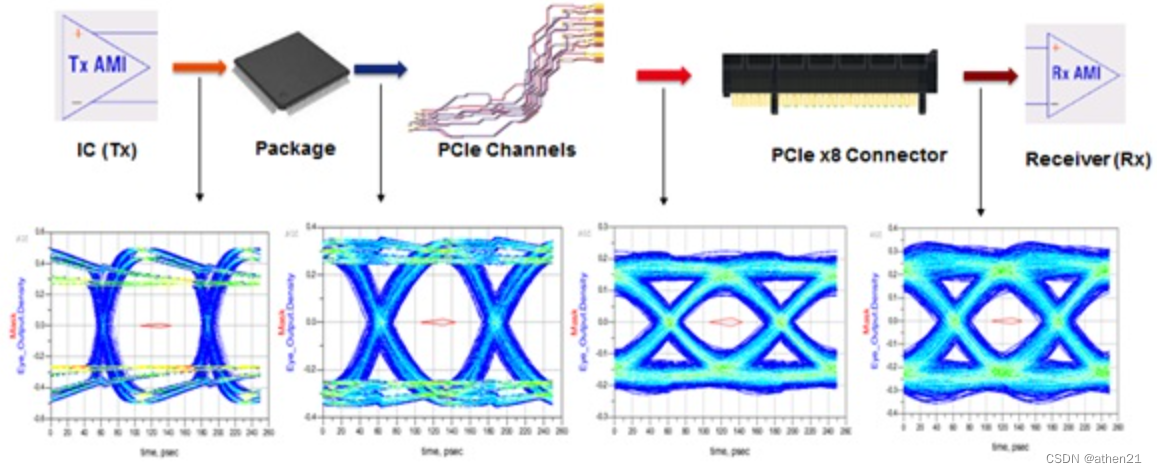

为了进行SI 分析,首先使用电磁 (EM) 求解器对 PCIe 连接器、通道数据总线和封装进行进行提取 S 参数。根据S参数从SI的角度对以下因素进行分析:阻抗匹配、反射、衰减、阻抗失配、传播延迟、串扰。

就本文而言,分析中使用的高速数字 (HSD) 板是 12 层高速 FPGA 数字板。信道网络中的噪声主要影响系统的抖动性能,这会导致信号质量下降。对于水平和垂直过渡,如引线键合、通孔阵列以及封装和印刷电路板的焊球,生成了用于 SI 和电源完整性 (PI) 仿真的 3D 模型。使用 SIPro 为 PCIe 3.0 八通道数据总线提取 EM 仿真数据。

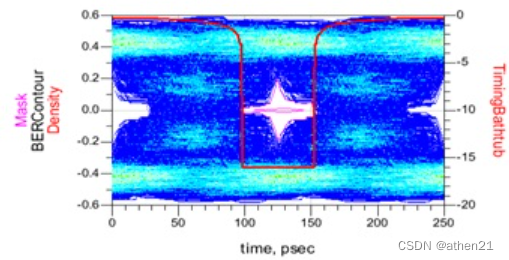

使用PRBS随机数据输入对整个通道进行瞬态分析的结果如图4所示。该通道将连接器、通道和芯片封装的提取的S参数在ADS软件中进行连接仿真。从眼图中可以看出,由于连接器的原因,信号在较长的传输路径上会下降。输入信号是 8 Gbps 的 PRBS-11 串行数据。

PCIe合规性测试

合规性是确保产品可互操作的必要条件。它验证PCIe通道是否符合PCIe规范。下表列出了不同的一致性测试参数。

| Signal | PCIe合规性 |

| 发送端测试 | 发送端信号质量测试 发送端Preset测试 |

| 接收器测试 | 接收端抖动测试 |

| 链接均衡测试 | 发送端发送链路初始均衡测试 TX 和RX 链路均衡测试 |

发送端信号质量测试

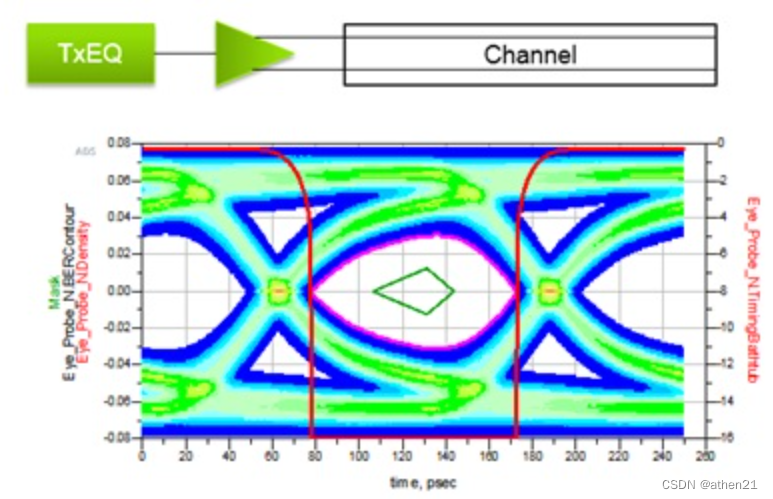

为了全面表征PCIe发送器,根据PCI-SIG规范测量单位间隔(UI)时间、电压、眼图模板、抖动、空闲时序和通道偏移。大多数规格需要在 250 个连续的 UI 上进行测量。为了进行准确的测量,应使用从发送器的 Tx 输出到其输入的直接连接。这样做可以确保最低的噪声测量。下图显示了发射机转换位上的眼图和抖动测量。

接收端均衡测试

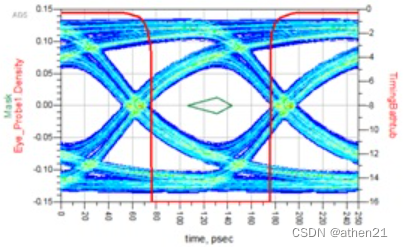

接收机需要测试接收的灵敏度和对抖动的容忍度。测试方法是为器件的 Rx 输入提供激励,并通过 Tx 引脚监控器件的响应。将被测的眼睛与眼图模板相结合进行合规性测试。

下图在没有任何均衡的情况下,眼图是闭合的。但是,在应用 Rx 均衡后,眼图是睁开的,符合 PCIe 规范。均衡背后的思想是使用其他位的电压电平来校正当前位的电压电平。由于ISI来自信道的频率相关损耗,接收信号的眼图完全闭合,时钟和数据无法从严重失真的信号中恢复。在决策反馈均衡 (DFE) 均衡器之后,均衡信号的眼图被打开,数据中心的垂直眼图开度约为 368 mV。该值足够大,DFE可以在可接受的BER下恢复数据。

发关端均衡设置与Preset测试

PCIe 3.0 规范指定了具有 10 个预设的一致性模式。在进入一致性测试模式,100MHz 时钟被用于在不同的各种Preset之间进行循环,用于抖动、电压和时序的测量。一致性测试可确保被测设备能够生成所有Preset与均衡电平,以满足规范的测试要求。下图 显示了所有Preset的波形。

结论

为了确保 PCIe Gen3 串行通道的信号质量,需信号完整性分析和一致性测试是实现这一目标的重要工具,采用使用IBIS-AMI模型的方法结合PCIe-SIG 规范,直接准确地优化通道性能。

这篇文章来自于 Anil Kumar Pandey的博客。

文章探讨了PCIe3.0高速接口面临的串扰、阻抗问题、抖动和均衡挑战。通过使用IBIS-AMI模型进行仿真,以及SI分析和合规性测试,确保信号质量和设备间的互操作性。

文章探讨了PCIe3.0高速接口面临的串扰、阻抗问题、抖动和均衡挑战。通过使用IBIS-AMI模型进行仿真,以及SI分析和合规性测试,确保信号质量和设备间的互操作性。

68

68

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?