一、常用的设置

1、语言设置

安装如下插件,然后在config

2、编码格式设置

解决中文注释乱码问题。vivado 默认是这个格式,这里也设置一样。

ctrl +shift +p 打开设置项

3、插件信任区设

打开一个verilog 文件,显示是纯本文,没有自动识别,左侧的插件显示灰色,且有防御的小图标。

打开设置,将 ✔ 去掉,重启即可。

二、常用的插件

1、verilog插件

具备语言识别,颜色标记,语句补全,自动例化功能

2、testbench 插件

可以自动生成测试激励文件

3、格式排版

定义跳转插件

不需要额外的设置,装上这个插件即可。理论上iverilog 插件也支持定义跳转,实际测试不行,需要搭配下面这个插件。

安装之后,右上角会出现下图的这个栏,有编译,接口生成,和模块复制的几个选项。

代码对其插件

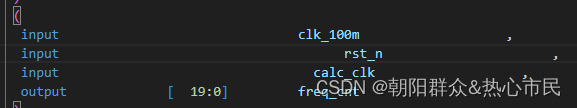

比如原先的代码如下图所示

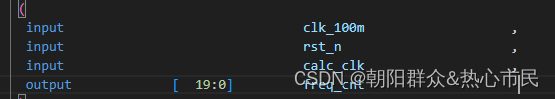

使用快捷键ctrl + L 实现如下图的对其

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?