fifo是FPGA中使用最为频繁的IP核之一,可以通过软件自动生成,也可以自主编写。下面介绍vivado的fifo生成步骤

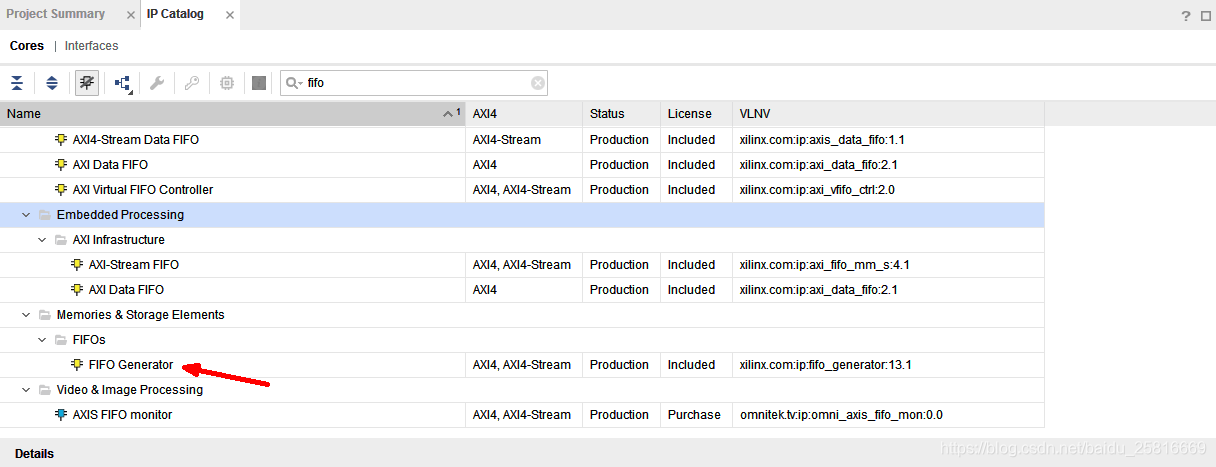

1、打开ip核,搜索fifo

2、创建fifo

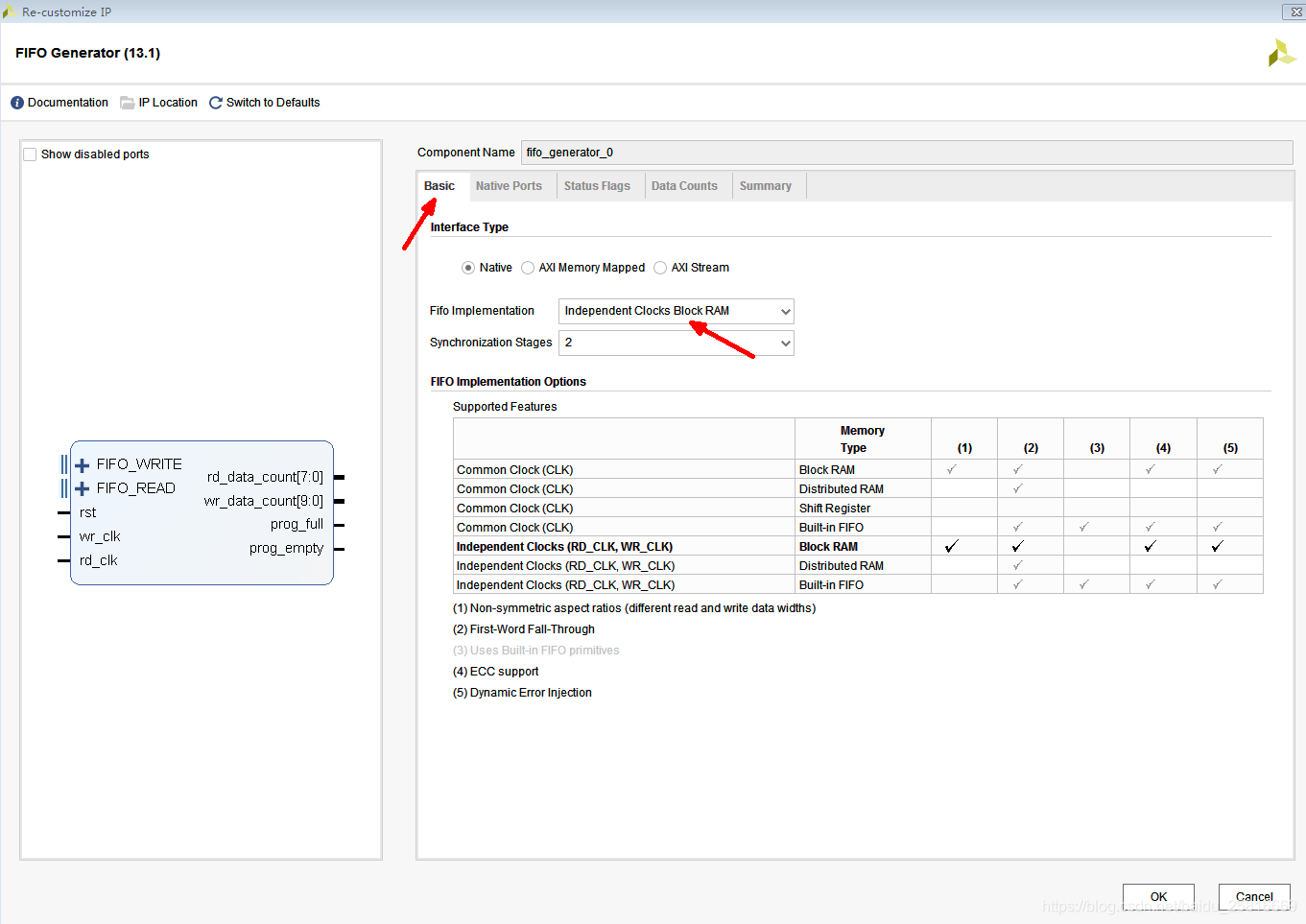

2、创建fifo

选择独立的时钟块ram。

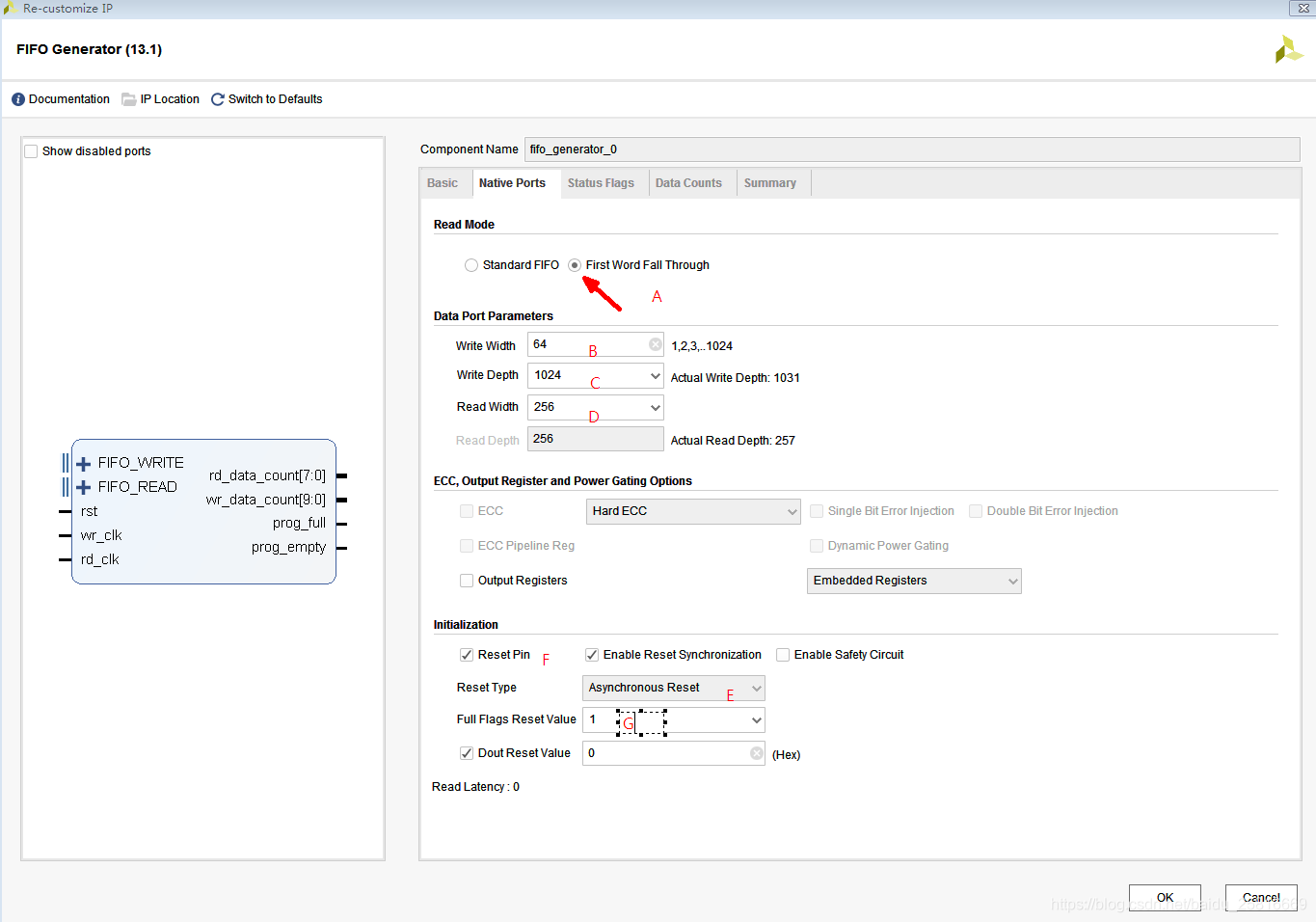

3、

A、选择标准fifo或者frist word full模式,标准模式是数据延时一个时钟周期进入或者输出;frist word full模式时数据直接随时钟同步进入或者输出。

B、设置输入数据位宽

C、设置f写ifo深度

D、设置输出数据位宽、读fifo深度会自动生成

E、选择异步复位

F、勾选复位管脚

G、选择高电平复位或低电平复位

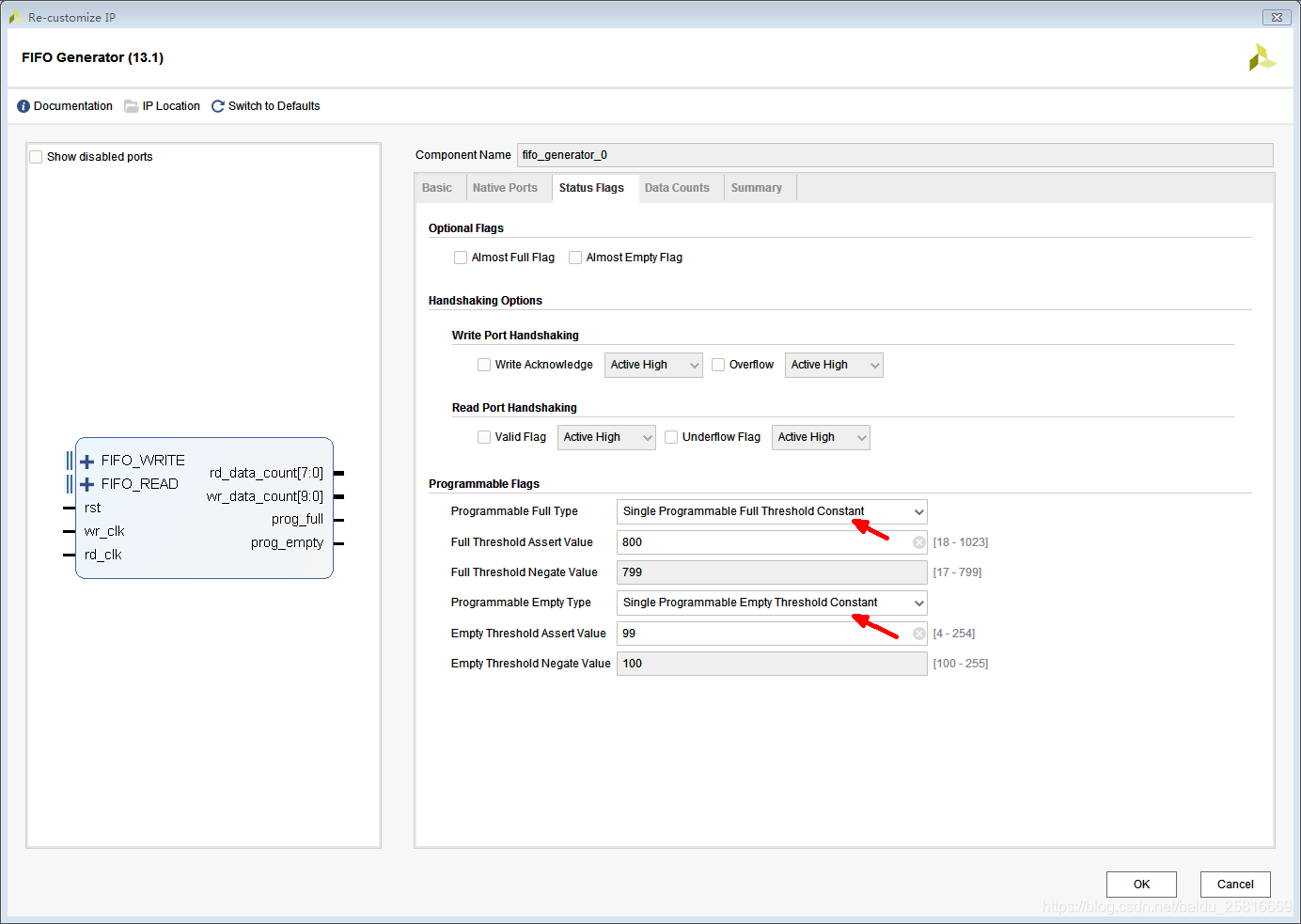

4、设置满、空标志位

选择信号可编程满、空阈值、可以自主设置漫、空标志位的阈值,保证fifio运行的可靠性,尽量多留些阈值

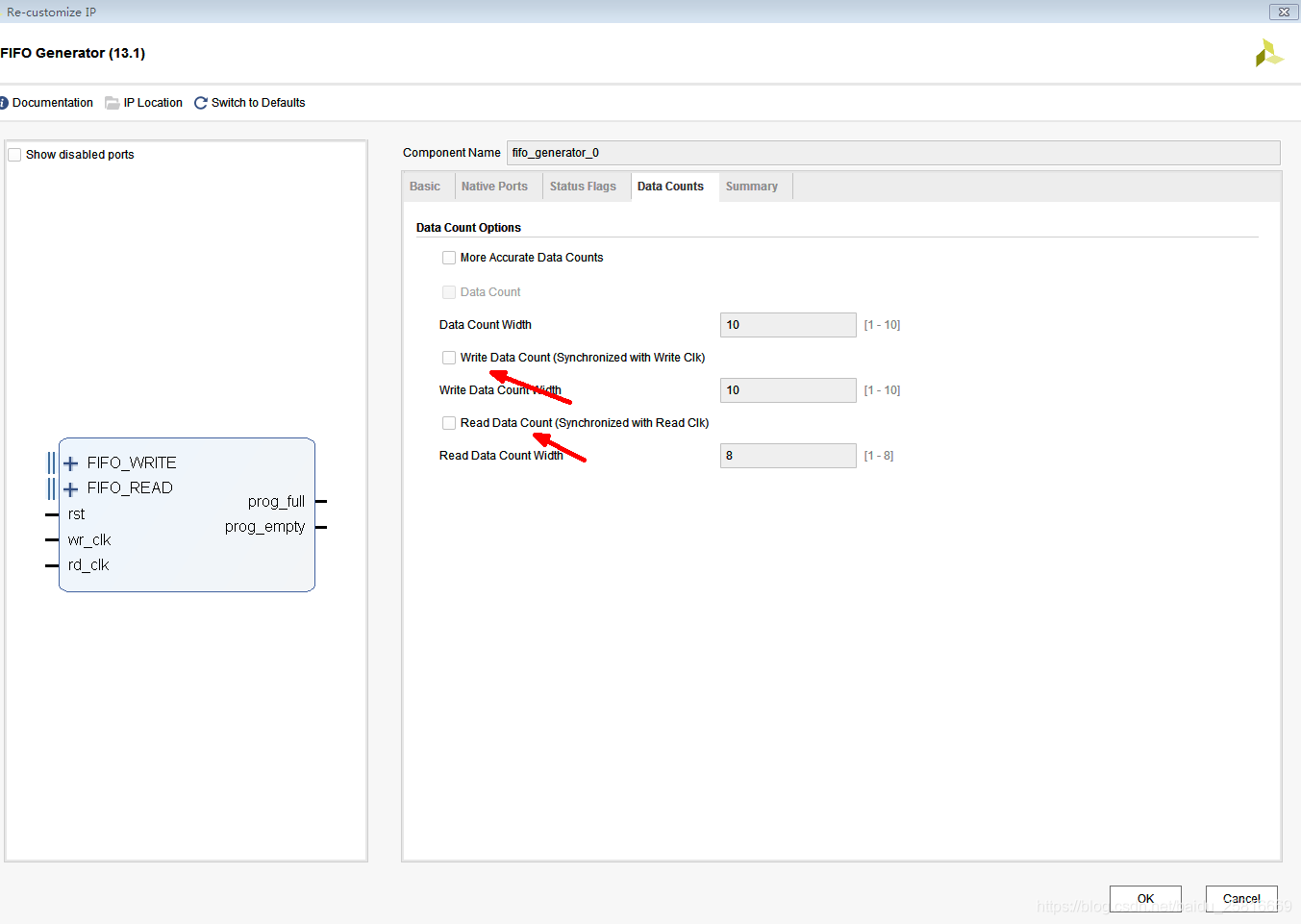

5、读写计数,可以不勾选,只通过满空标志位来做读判断,计数的标志位存在周期短,判断存在不确定性

6、可以看到fifo占用的资源。

三、读写fifo例程

写fifo

//write fifo us1

always@(posedge wrclk, negedge sys_reset_n_i)

begin

if (!sys_reset_n_i)

begin

fifo_wrreq_ddr3_us <= 0 ;

fifo_data_ddr3_us <= 0 ;

end

else

begin

if(fifo_prog_full_ddr3_us!= 1)

fifo_wrreq_ddr3_us <= 1 ;

else

fifo_wrreq_ddr3_us <= 0 ;

if(fifo_wrreq_ddr3_us == 1)

begin

if(fifo_data_ddr3_us < 64'b1111_1111_1111_1111_1111_1111)

fifo_data_ddr3_us <=fifo_data_ddr3_us + 1 ;

else

fifo_data_ddr3_us <= 0 ;

end

else

fifo_data_ddr3_us <= fifo_data_ddr3_us ;

end

end

endmodule

读fifo

assign fifo_rdreq_ddr3_ds = !fifo_empty_ddr3_ds;

always@(posedge sys_clk_i,negedge sys_reset_n_i)

begin

if(!sys_reset_n_i)

rd_ck_flag_cp<= 1'b0;

else

begin

if (fifo_q_ddr3_ds_r!==fifo_q_ddr3_ds)

rd_ck_flag_cp<= 1'b1;

else

rd_ck_flag_cp<= 1'b0;

end

end

//jiao yan cuo wu ji shu jiao yan wei zi zeng

always@(posedge sys_clk_i,negedge sys_reset_n_i)

begin

if(!sys_reset_n_i)

begin

rd_ck_cnt <= 64'b0;

fifo_q_ddr3_ds_r <= 64'b0 ;

end

else

begin

if(rd_ck_flag_cp==1)

rd_ck_cnt <=rd_ck_cnt+1'b1;

else

rd_ck_cnt <= rd_ck_cnt;

if ( ( fifo_rdreq_ddr3_ds==1 ) && (fifo_q_ddr3_ds_r < 64'b1111_1111_1111_1111_1111_1111) )

fifo_q_ddr3_ds_r <= fifo_q_ddr3_ds_r + 1'b1 ;

else

fifo_q_ddr3_ds_r <= 64'b0;

end

end

endmodule

9924

9924

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?