一、问题

信号变量类型由 reg 或者 wire 修改为 logic 类型?

- logic是数据类型;wire和reg是类型

wire -> wire logic

reg -> (var) logic- 驱动用logic;检测用wire

- interface中可以尽量用logic,但要注意检测用wire,驱动多个模块,用logic报错时改为wire;class中只能用logic

将 rstn 的类型由 logic 修改为 bit 类型?

- rstn = x 时,rstn===0,此时不成立

- rstn = x 时,!rstn=x,此时不成立

- 修改为bit后,rstn = 0,rstn===0成立,!rstn=1成立

- = =返回值含x,= = =返回值不含x

二、实验要求

- 时钟和复位写在task中

- 采用数组发送数据

- 将激励与DUT分开,将激励发生器定义为一个新的模块:包含

set_ name()、 chnl_write()、 chnl_idle()

三、代码分析

时间单位

`timescale 1ns/1ps// 单位/精度

信号

logic clk;

logic rstn;

logic [31:0] ch0_data;//输出数据到DUT

logic ch0_valid;//输出有效信号DUT

logic ch0_ready;//DUT输入ready

logic [5:0] ch0_margin;//DUT输入fifo余量

logic [31:0] ch1_data;

logic ch1_valid;

logic ch1_ready;

logic [5:0] ch1_margin;

logic [31:0] ch2_data;

logic ch2_valid;

logic ch2_ready;

logic [5:0] ch2_margin;

logic [31:0] mcdt_data;//DUT输出当前输出的数据

logic mcdt_val; //DUT输出当前输出的有效信号

logic [1:0] mcdt_id; //DUT输出当前输出的通道号

例化

将tb的信号与dut的端口相连

mcdt dut(

.clk_i(clk)

,.rstn_i(rstn)

,.ch0_data_i(ch0_data)

,.ch0_valid_i(ch0_valid)

,.ch0_ready_o(ch0_ready)

,.ch0_margin_o(ch0_margin)

,.ch1_data_i(ch1_data)

,.ch1_valid_i(ch1_valid)

,.ch1_ready_o(ch1_ready)

,.ch1_margin_o(ch1_margin)

,.ch2_data_i(ch2_data)

,.ch2_valid_i(ch2_valid)

,.ch2_ready_o(ch2_ready)

,.ch2_margin_o(ch2_margin)

,.mcdt_data_o(mcdt_data)

,.mcdt_val_o(mcdt_val)

,.mcdt_id_o(mcdt_id)

);

产生时钟

定义可以设置时钟周期的task,在initial中调用

task clk_gen(int period);

clk <= 0;

forever begin

#period/2 clk<= !clk;

end

endtask

initial begin

// generate clk

clk_gen(10);

end

产生复位

定义可以复位的task,在initial中调用

task rstn_gen()

#10 rstn <= 0;

repeat(10) @(posedge clk);

rstn <= 1;

endtask

initial begin

// trigger rstn

rstn_gen();

end

一般直接在initial中初始化这两个

发送激励模块

有三个通道发送激励,定义一个激励发生器模块,在模块中实现slave的功能,三个通道例化该模块可以减少重复代码

module chnl_initiator(

input clk,

input rstn,

output logic [31:0] ch_data, //输出数据到DUT

output logic ch_valid,//输出有效信号到DUT

input ch_ready,//DUT输入ready

input [ 5:0] ch_margin//DUT输入fifo余量

);

string name;

//为实例化的模块命名

function void set_name(string s);

name = s;

endfunction

task chnl_write(input logic[31:0] data);

// drive valid data

@(posedge clk);//模仿时序逻辑,等到上升沿后发送数据

ch_valid <= 1;

ch_data <= data;

@(negedge clk);//valid、data发送到接口与clk有一个δcycle,ch_ready从接口返回,可能与data在同一个δcycle,这时需要模拟接口到slave获取到的ready信号的Delay;##10ps

wait(ch_ready === 'b1);//模拟组合逻辑,数据如果没有被获取就保持@(ch_ready === 'b1)

$display("%t channel initial [%s] sent data %x", $time, name, data);

chnl_idle();

endtask

task chnl_idle();

// drive idle data

@(posedge clk)

ch_valid <= 0;

ch_data <= 0;

endtask

endmodule

产生数据

将要发送的数据存放在数组中

logic [31:0] chnl0_arr[];//声明动态数组

logic [31:0] chnl1_arr[];

logic [31:0] chnl2_arr[];

initial begin

chnl0_arr = new[100];//创建动态数组

chnl1_arr = new[100];

chnl2_arr = new[100];

foreach(chnl0_arr[i])begin

chnl0_arr[i] = 'h00C0_00000 + i;

chnl1_arr[i] = 'h00C1_00000 + i;

chnl2_arr[i] = 'h00C2_00000 + i;

end

end

实例化slave模块

chnl_initiator chnl0_init(

.clk (clk),

.rstn (rstn),

.ch_data (ch0_data),

.ch_valid (ch0_valid),

.ch_ready (ch0_ready),

.ch_margin(ch0_margin)

);

chnl_initiator chnl1_init(

.clk (clk),

.rstn (rstn),

.ch_data (ch1_data),

.ch_valid (ch1_valid),

.ch_ready (ch1_ready),

.ch_margin(ch1_margin)

);

chnl_initiator chnl2_init(

.clk (clk),

.rstn (rstn),

.ch_data (ch2_data),

.ch_valid (ch2_valid),

.ch_ready (ch2_ready),

.ch_margin(ch2_margin)

);

发送激励

initial begin

@(posedge rstn);

repeat(5) @(posedge clk);

// Give unique names to each channel initiator

chnl0_init.set_name("chnl0_init");

chnl1_init.set_name("chnl0_init");

chnl2_init.set_name("chnl0_init");

// use chnl0_arr to send all data

foreach(chnl0_arr[i]) chnl0_init.chnl_write(chnl0_arr[i]);

// use chnl1_arr to send all data

foreach(chnl1_arr[i]) chnl1_init.chnl_write(chnl1_arr[i]);

// use chnl2_arr to send all data

foreach(chnl2_arr[i]) chnl2_init.chnl_write(chnl2_arr[i]);

end

三、Questasim的Makefile[^2]

#############################

# User variables

#############################

TB = tb1

DFILES = {arbiter.v,slave_fifo.v,mcdt.v}

VFILES = $(TB).v

#############################

# Environment variables

#############################

VLAB = vlib work #创建名为work的lib

VCOMP = vlog -l com.log #vlog编译;-l com.log将日志存放到com.log中

VSTART = vsim -l sim.log #vsim启动questa

VSIMULATE = -voptargs=+acc #simulate

VADDWAVE = add wave -position insertpoint sim:/$(TB)/*#添加top文件的波形

VSAVE = log -r /*#生成波形文件

RUN = run 1us #运行1ns

VQUIT = quit -f #退出

all: create_lib compile simulate #make要执行的顺序

create_lib:

$(VLAB)

compile:

$(VCOMP) $(DFILES) $(VFILES)

simulate:

#$(VSTART) -c $(VSIMULATE) work.$(TB) -do "$(SAVE) $(RUN);$(VQUIT)"

$(VSTART) $(VSIMULATE) work.$(TB) -do "$(VADDWAVE);$(VSAVE);$(RUN)"

clean:

rm -rf work mti_lib transcript modelsim.ini *.log vsim.wlf

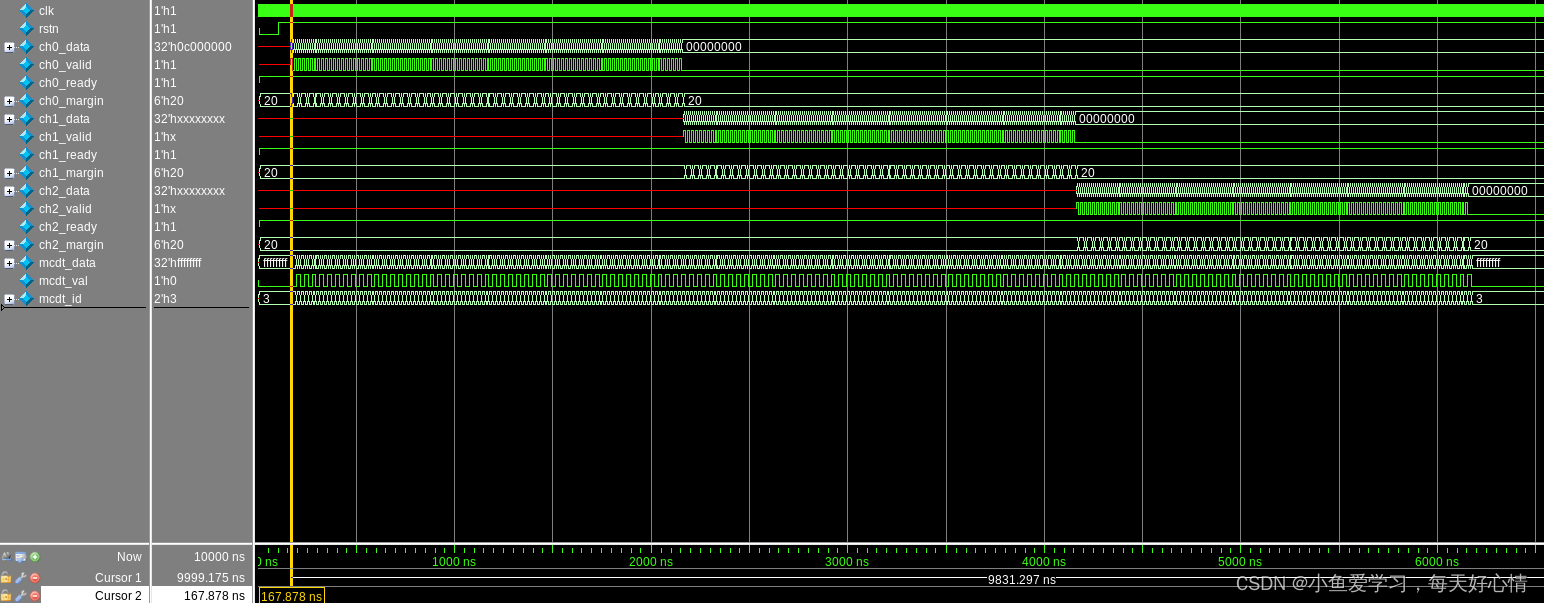

四、波形

每个通道依次发送100个数据

紧凑发送100个数据:三个initial为并行的

initial begin

@(posedge rstn);

repeat(5) @(posedge clk);

chnl0_init.set_name("chnl0");

foreach(chnl0_arr[i]) chnl0_init.chnl_write(chnl0_arr[i]);

end

initial begin

@(posedge rstn);

repeat(5) @(posedge clk);

chnl1_init.set_name("chnl1");

foreach(chnl1_arr[i]) chnl1_init.chnl_write(chnl1_arr[i]);

end

initial begin

@(posedge rstn);

repeat(5) @(posedge clk);

chnl2_init.set_name("chnl2");

foreach(chnl2_arr[i]) chnl2_init.chnl_write(chnl2_arr[i]);

end

紧凑发送100个数据:fork join

wait (rstn === 1'b1);

repeat(5) @(posedge clk);

fork

foreach(chnl0_arr[i]) chnl0_init.chnl_write(chnl0_arr[i]);

foreach(chnl1_arr[i]) chnl1_init.chnl_write(chnl1_arr[i]);

foreach(chnl2_arr[i]) chnl2_init.chnl_write(chnl2_arr[i]);

join

8762

8762

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?