好的工程,始于仿真,大家好!

网络上有很多ddr3仿真,example例程仿真等的教程,大部分实际应用价值不大,而且博客介绍也不够详细;比如ddr3调试经验分享(一)——modelsim实现对vivado中的MIG ddr3的仿真 - 清霜一梦 - 博客园 (cnblogs.com)

上文只介绍了TEST_PASSED,对内部逻辑并不清晰;

DDR3自建仿真平台(一)--成功拉起init_calib_complete信号 - 知乎 (zhihu.com)

上文介绍了基本的用例;

当然,alinx公司的开发板也封装了比较好的读写接口。

本文介绍ddr3的全部仿真流程。

1、example仿真

上述讲述了example的整个数据通路;

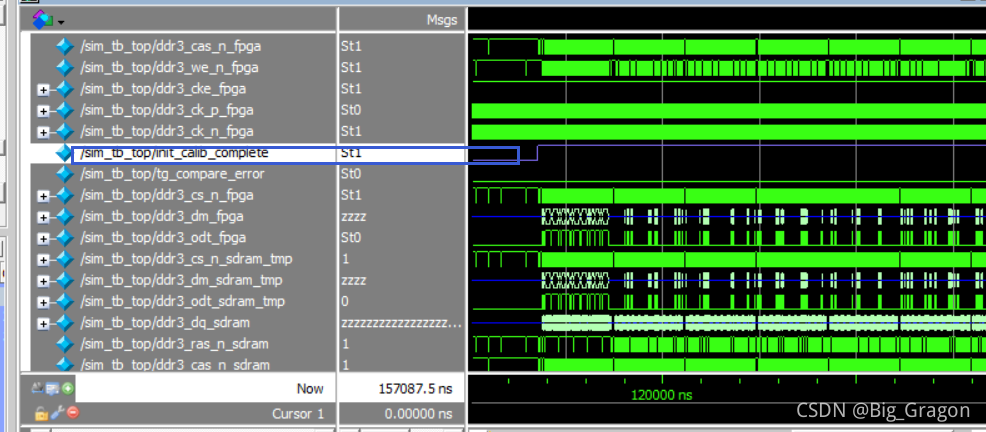

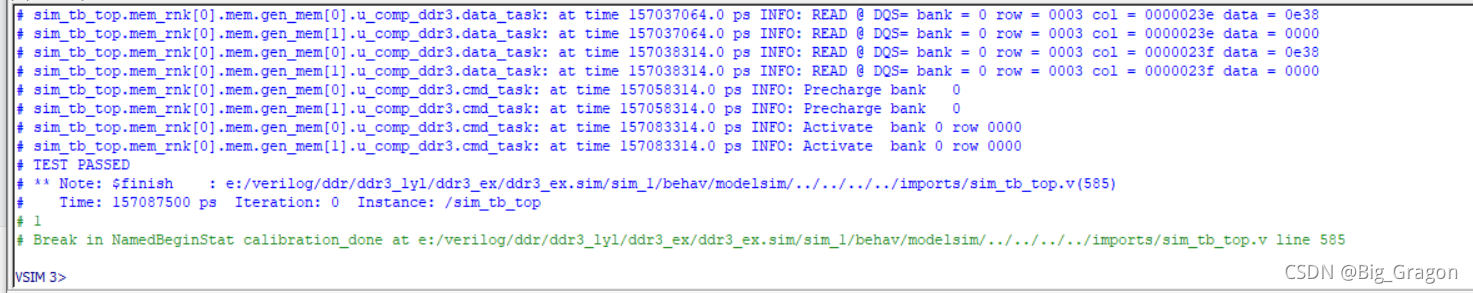

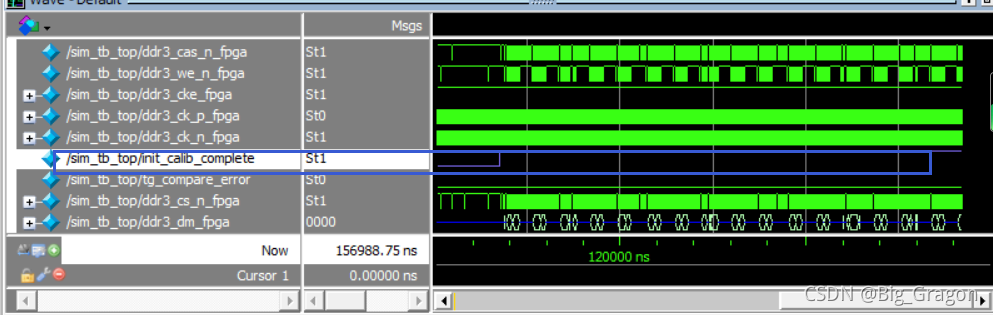

当init_calib_complete信号拉高,表示ddr3的ipcore已经初始化ddr3完毕,tragenfic_gen模块会随机读写ddr3,最后给出一个TEST_PASSED

这有什么用?

2、自测仿真平台

如果你想自己使用ddr3,一种方法是反复烧录到fpga上去验证,一种是建立仿真平台,这里给出一种方法。

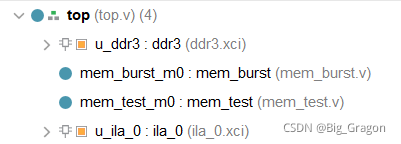

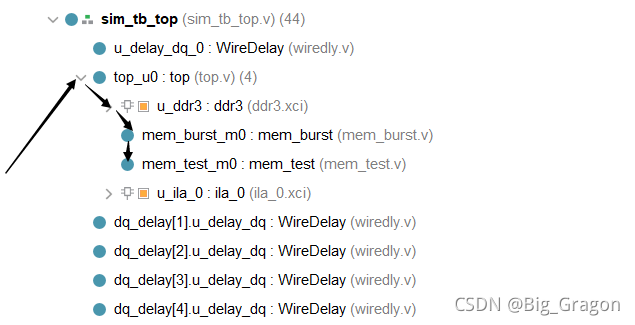

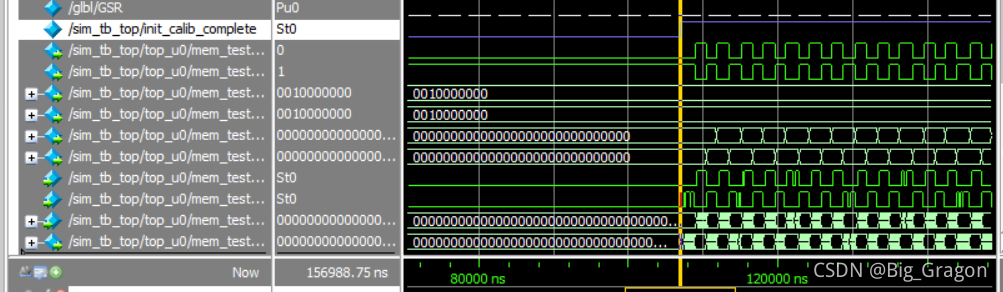

这是我们的设计工程文件,是alinx公司的开发板提供的,封装了mem_burst.v接口文件,mem_test.v是他们用来测试ddr3的,我们在使用ddr3的时候,需要将mem_test替换成自己的设计文件,mem_burst.v是很好的一个设计,简化了ipcore的使用难度。

本文对这种设计思路进行一个仿真。记住:如果可以根据自己的工程要求,设计整个工程,仿真思路是一致的。

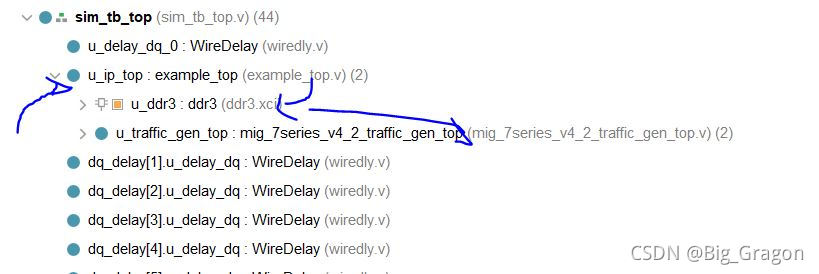

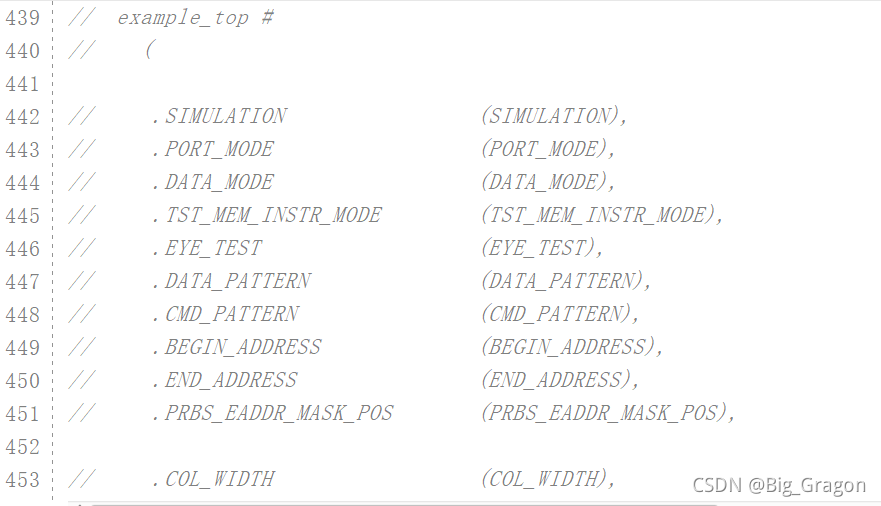

1)example_top.v就没用了

从第一小节可以看出,example_top里面,包含了ddr3这个ipcore,包含了tranfic_gen这个激励产生模块。现在整体替换掉。

写流程:

读流程:

读流程:

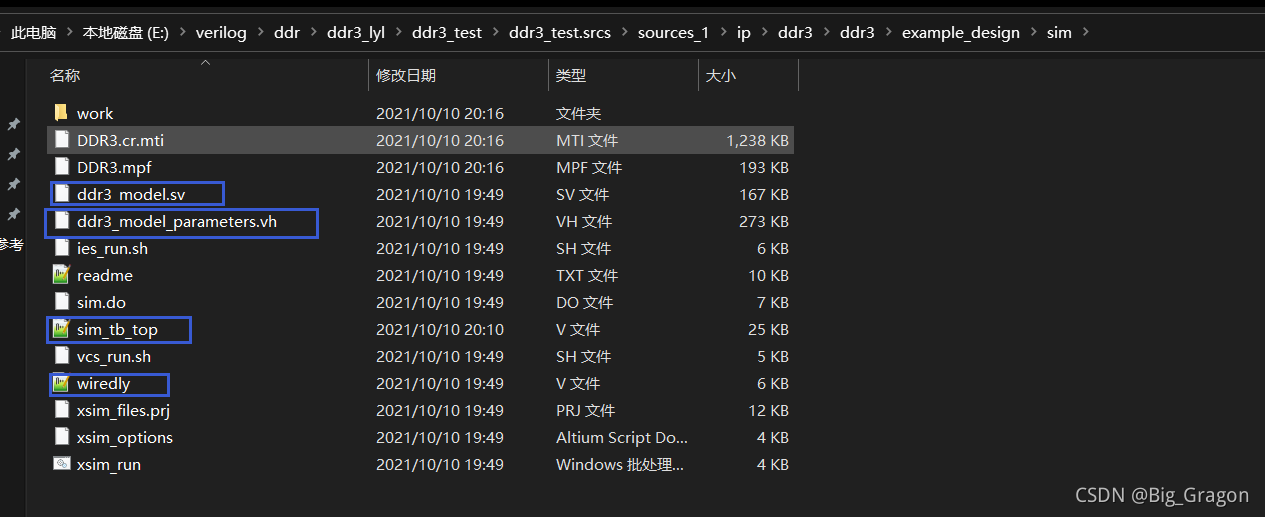

那么这个仿真平台包含需要手动添加哪些文件呢?

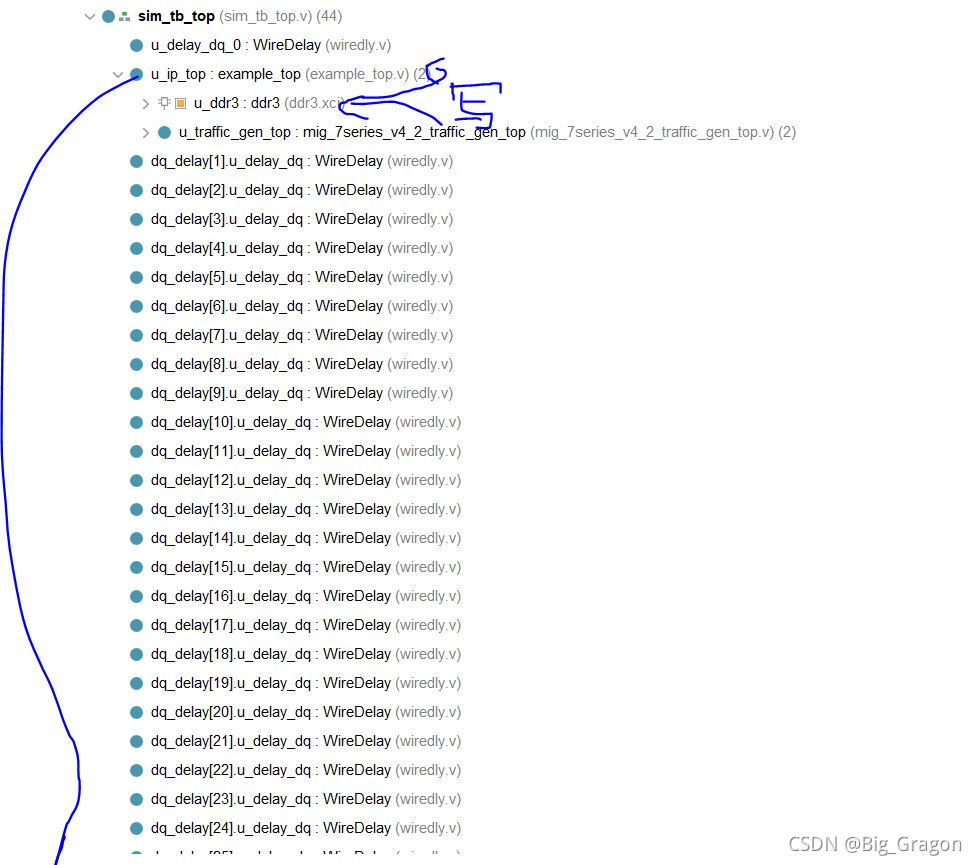

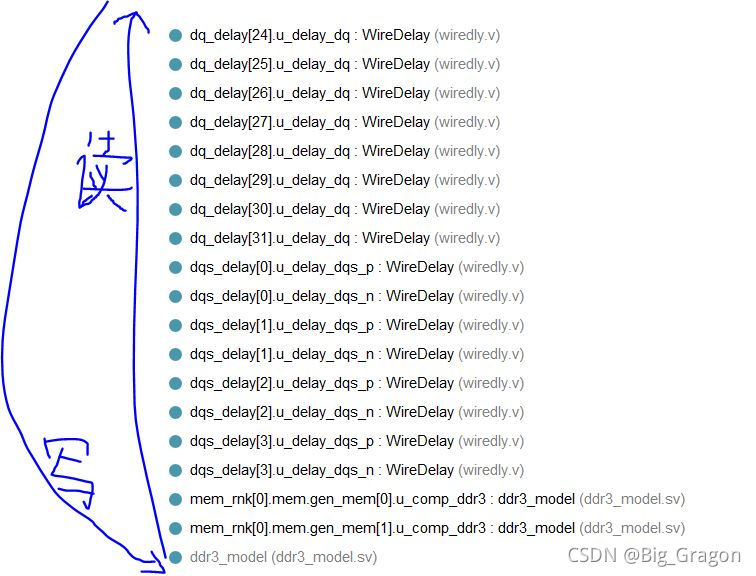

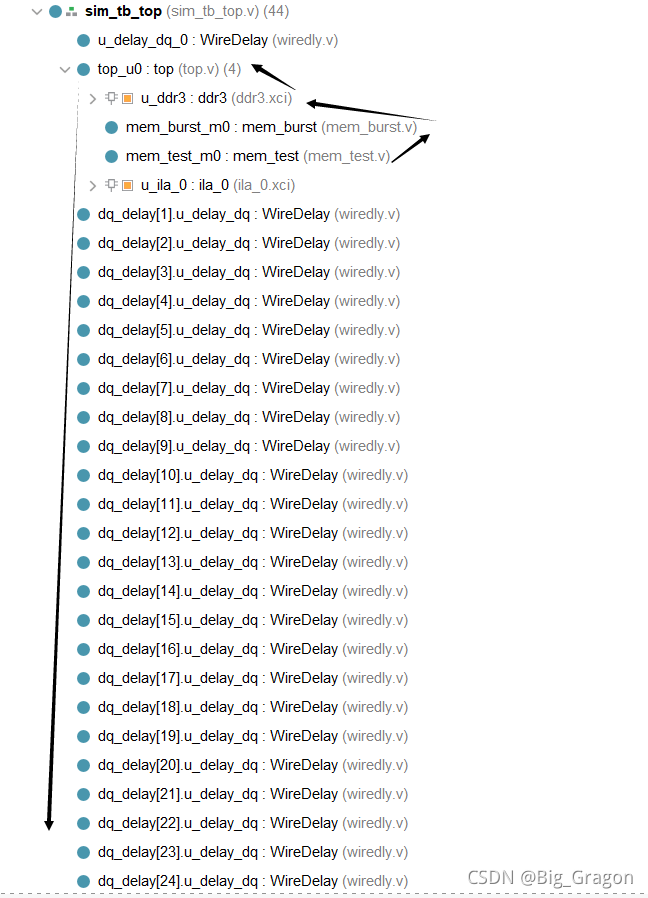

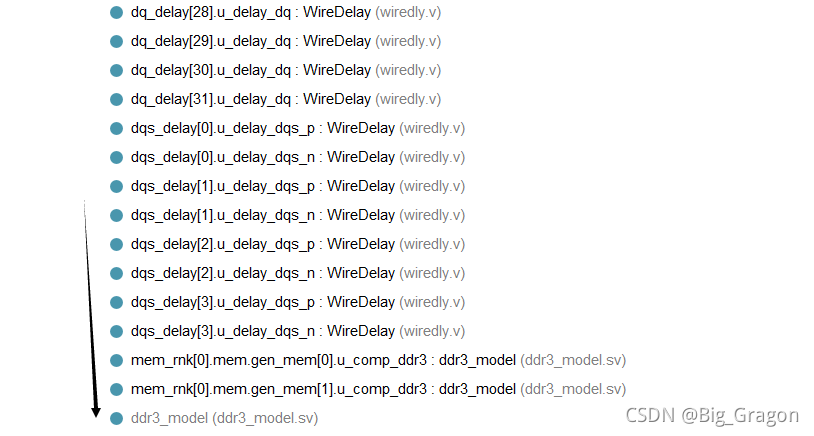

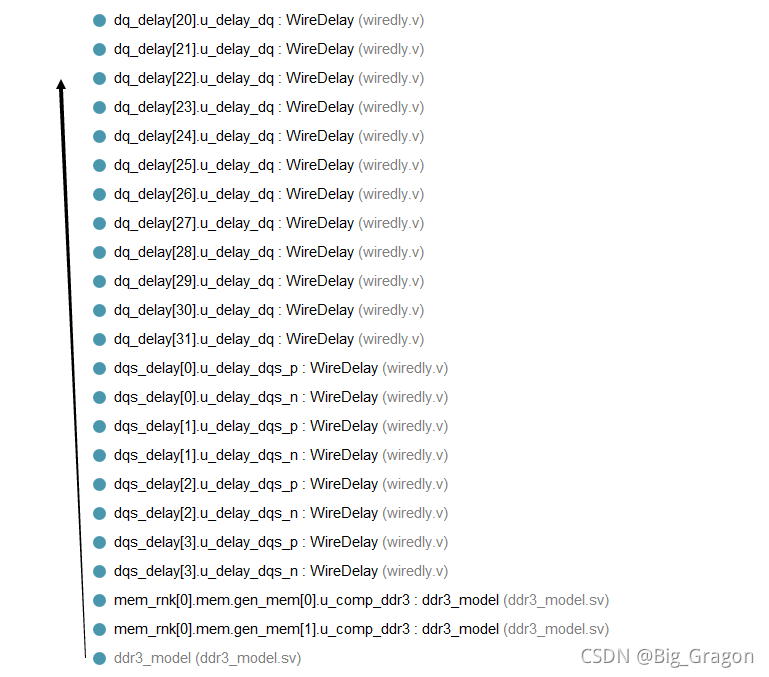

sim_tb_top是平台的top,ddr3_model.sv是ddr3仿真模型,ddr3_model_parameters.vh是头文件,wiredly.v是延时文件, ddr3_model.sv,ddr3_model_parameters.vh,wiredly.v构成了仿真模型;

sim_tb_top是平台的top,ddr3_model.sv是ddr3仿真模型,ddr3_model_parameters.vh是头文件,wiredly.v是延时文件, ddr3_model.sv,ddr3_model_parameters.vh,wiredly.v构成了仿真模型;

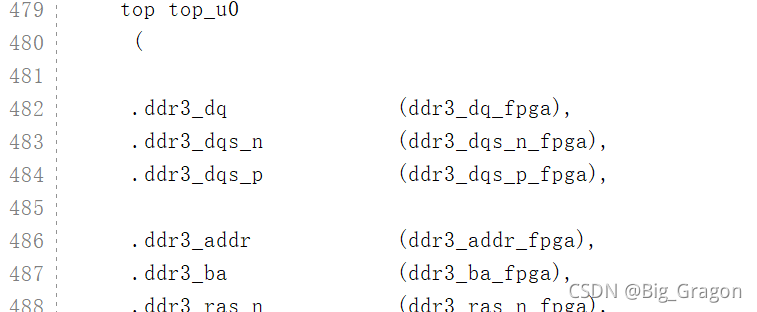

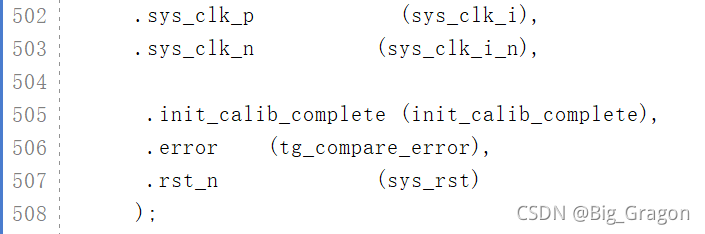

sim_tb_top里面的例化修改,删掉exapmle_top

替换成top,也就是我们的设计顶层,注意用户定义的接口

该修改的还是得修改的

3)最好使用Modelsim等仿真工具,vivado的仿真速度。。。自己想想

经过上述对sim_tb_topde 修改,我们已经成功的把设计文件加入到仿真平台,那么我们的设计时序是否满足要求呢?那就仿真见分晓吧。

init_calib_complete完成初始化,然后mem_test开始进行读写测试

观察波形即可,本文到此结束。

3352

3352

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?