最近学到PLD的结构,发现基本单元的结构和ROM是一样的,就看了很多存储器相关的东西,顺手记录一下。

顺序存储器(SAM)

SAM(Sequential Access Memory),其在存取信息时,只能按存储单元的位置,顺序地一个接一个地进行存取的存储器。最典型的例子是磁带。对其进行细分,又可分为FIFO和FILO。取名来看,其原本是和RAM(Ramdom Access Memory)对标的吧,但实际情况好像是变成ROM和RAM对标了hh。

1.FIFO

FIFO(First Input First Output)简单说就是指先进先出,即第一个进入其内的数据第一个被移出,其中一个是存储器的输入口,另一个口是存储器的输出口。FIFO由动态移存器组成,而动态移存器则是由基本的动态移存单元组成。

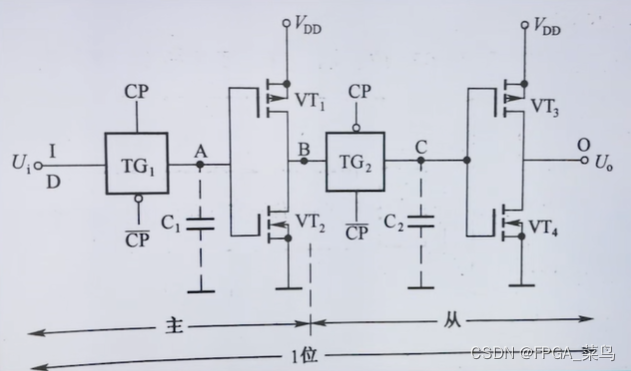

上图是一个动态移存单元,其再一个下降沿对数据进行记录。当处于高电平时,第一个传输门通,Ui传输到A点,假设Ui为1,则此时A点为1。栅电容(分布电容)充电快,放电慢,因此何以存储信息。经过一个cmos反相器,B点为0。过了一会儿,下降沿到来,电平CP变为了低电平,第二个传输门导通,C点为0,再经过一个cmos反相器,变为了1,实现了数据的存储。

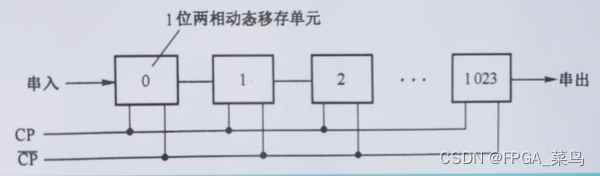

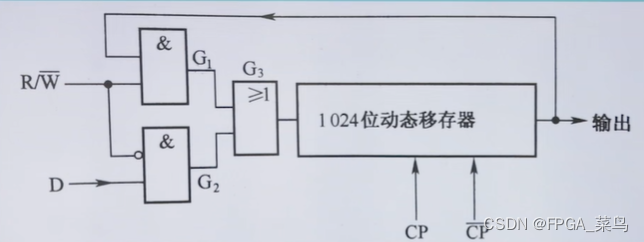

上图则是一个1024位的动态移存器。将动态移存器与一些逻辑门相连接,便得到了如下所示的1位位宽的FIFO。RW端为0时,将D的数据写入,动态移存器的最后一位舍弃;RW端为1时,最后一位数据输出的同时,反馈回动态移存器的最左侧。

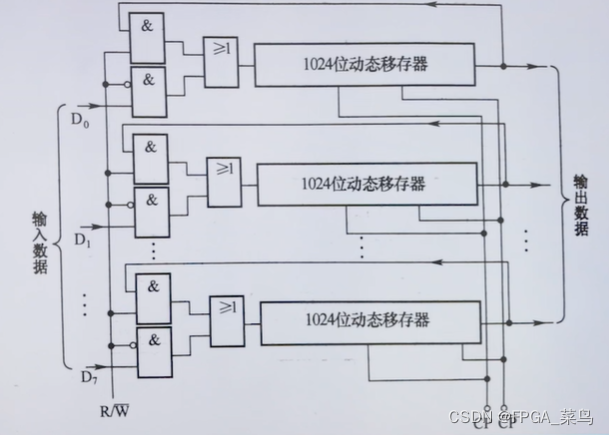

将8个这样的1位位宽的FIFO并联在一起,就构成了8位宽的FIFO。

2.FILO

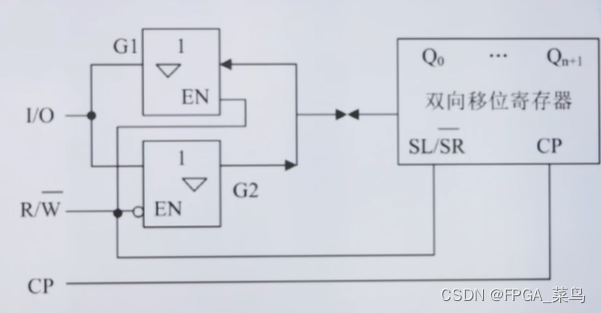

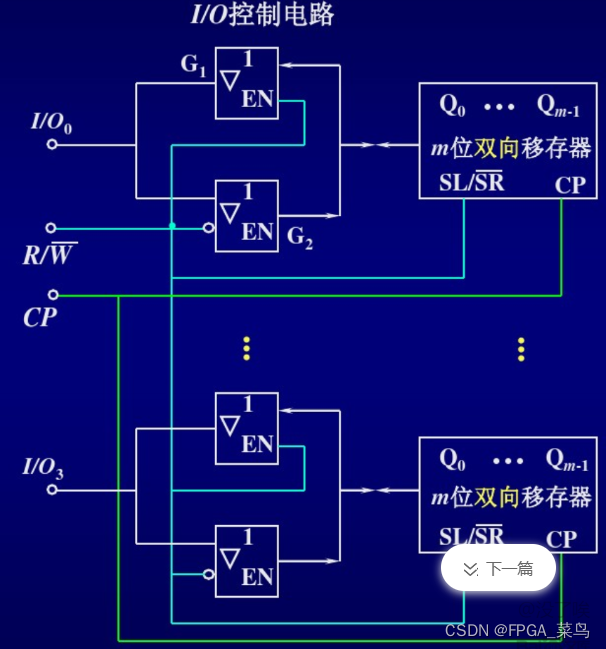

FILO(First Input Last Output)顺序存储器与FIFO的结构类似,但使用到的是双向移位寄存器。当RW端为0时,下方的逻辑电路通,下方不通,使得IO口内容传输至G2,同时双向移位寄存器右移,将数据写入最左侧;当RW为1时,双向移位寄存器左移,将数据输出到G2端,上方的逻辑电路通,下方不通,使得数据从IO口输出。因此,每次写入或输出的都是最左侧的数据。PS:第一次看到这个想到的就是堆栈,确实是很相似的概念。

类比FIFO,将4个这样的1位位宽的FILO并联在一起,就构成了4位宽的FILO。

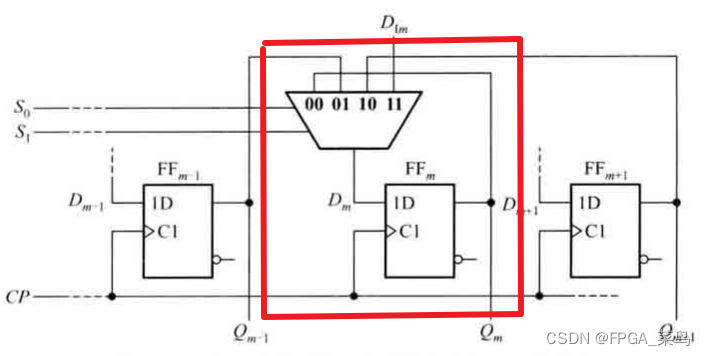

最简单的双向移位寄存器的基本存储位元,就是D触发器(实际上还需要一个四选一数据选择器),下面简单介绍其原理。当SL/SR = 1时,左移,此时S1S0为10,数据选择器选中FFm+1的输出。当CP脉冲到来,FFm+1的状态经数据选择器进入FFm,数据向左移动;当SL/SR = 0时,右移,此时S1S0为01,数据选择器选中FFm-1的输出。当CP脉冲到来,FFm-1的状态经数据选择器进入FFm,数据向右移动。

7707

7707

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?