Verilog HDL操作符

操作数

操作符的对象。比如A+B,+是操作符,AB就是操作数。

可以是常数,变量,数据对象例如iram[0]

或者有返回值的函数调用。

操作符

1、赋值操作符(=、<=)

<= 在进程模块中使用,是非阻塞赋值,它被赋值的对象必须是reg型。Always对reg变量赋值。

= 在进程中或assign赋值中使用。所以它被赋值的数据对象可以是reg与wire型。所以wire变量要用阻塞赋值

举例

assign idata = ~IData;//在assign语句中使用赋值操作符

always @(data_A,data_B)

begin

data=data_A&data_B; //在进程块中的阻塞赋值

end

always@(posedge clk)

begin

q<=d; //进程块中的非阻塞赋值操作符使用

end

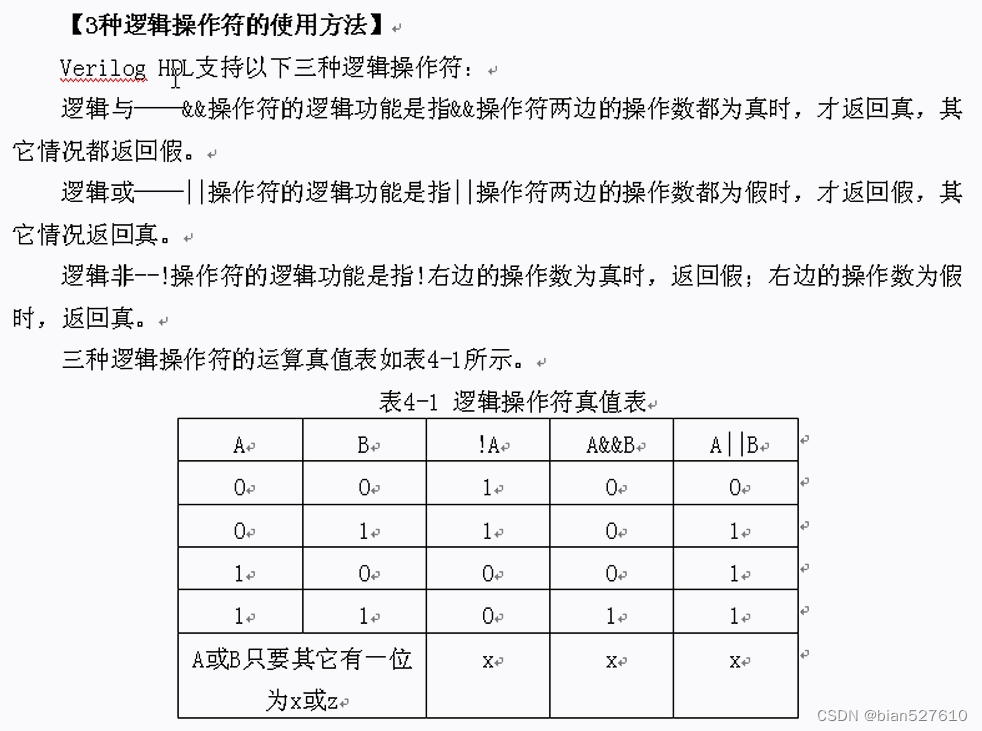

2、逻辑操作符:(&&、||、!)

逻辑关系操作符的返回值只有 1 bit,但操作数可以有多 bit。

3、关系操作符:(>、<、>=、<=)

关系操作符,返回值只有1bit ,要么为真要么为假。

//虽然关系操作符的操作数可能是多位,但是逻辑操作符返回的结果都是一位的。

//不管操作数的位宽是多少位,关系操作符运算的结果都为一位。

//如果操作数的位宽不一样,可以分为两种情况

//一是两种操作数都是无符号数,则把位宽小的操作数用0补齐。

8‘b10010000>5’b11000 //相当于8’b10010000 > 5’b00011000 返回1’b1

//二是两种操作数都是有符号数,则把位宽小的操作数用符号位的值补齐

8‘sb10010000>5’sb11000 //相当于8’sb10010000>5’b1111 1000相当于16>-8返回1’b1.

//但两个操作数,只要有一个为无符号数,则所有操作数都按无符号数处理

8‘sb10010000>5’b11000 //相当于8’sb00010000>5’b00011000 返回1’b1.

//若操作数中只要有一位为x或z,则关系操作符运算的结果都为x

8’b10010x00>5’b11000 //返回1’bx

4、算数操作符:(+、-、、/)*

幂运算()

使用方式:ab,返回a的b次幂

5、等式操作符;(、!=、=、!==)

相等==, AB,如果A相等B则返回1’b1否则返回1’b0;

不相等!=,A!=B,如果A不相等B则返回1’b1否则返回1’b0;

全等=, A=B,如果A全等B则返回1’b1否则返回1’b0;

非全等=,A!==B,如果A非全等B则返回1’b1否则返回1’b0;

在进行相等或者不相等时候,操作数中只要有一位为z或者x,返回值都为x;

在进行全等和非全等时,操作数中的z或者x都要进行位比较。

6、条件操作符:(?:)

条件表达式? 表达式1(真):表达式2(假)

7、移位操作符:(<<、>>)

<<左移 >>右移 <<<算数左移 >>>算数右移

负数的算数右移使用符号位填充。

8、拼接操作符:({})

{s,a,b} 拼接之后的位宽为s,a,b三个信号位宽的总和。

{2{s}} 拼接之后的位宽时两倍s的位宽。

{2{s},a} 拼接之后的位宽时两倍s的位宽加上a的位宽。

9、位运算与缩位操作符:(、|、^、&、^)

两个操作数的每一个位进行操作。

本文详细介绍了VerilogHDL中的各种操作符,包括赋值、逻辑、关系、算数、等式、条件、移位、拼接以及位运算,帮助读者理解并掌握在设计硬件描述语言时的运算规则。

本文详细介绍了VerilogHDL中的各种操作符,包括赋值、逻辑、关系、算数、等式、条件、移位、拼接以及位运算,帮助读者理解并掌握在设计硬件描述语言时的运算规则。

8145

8145

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?