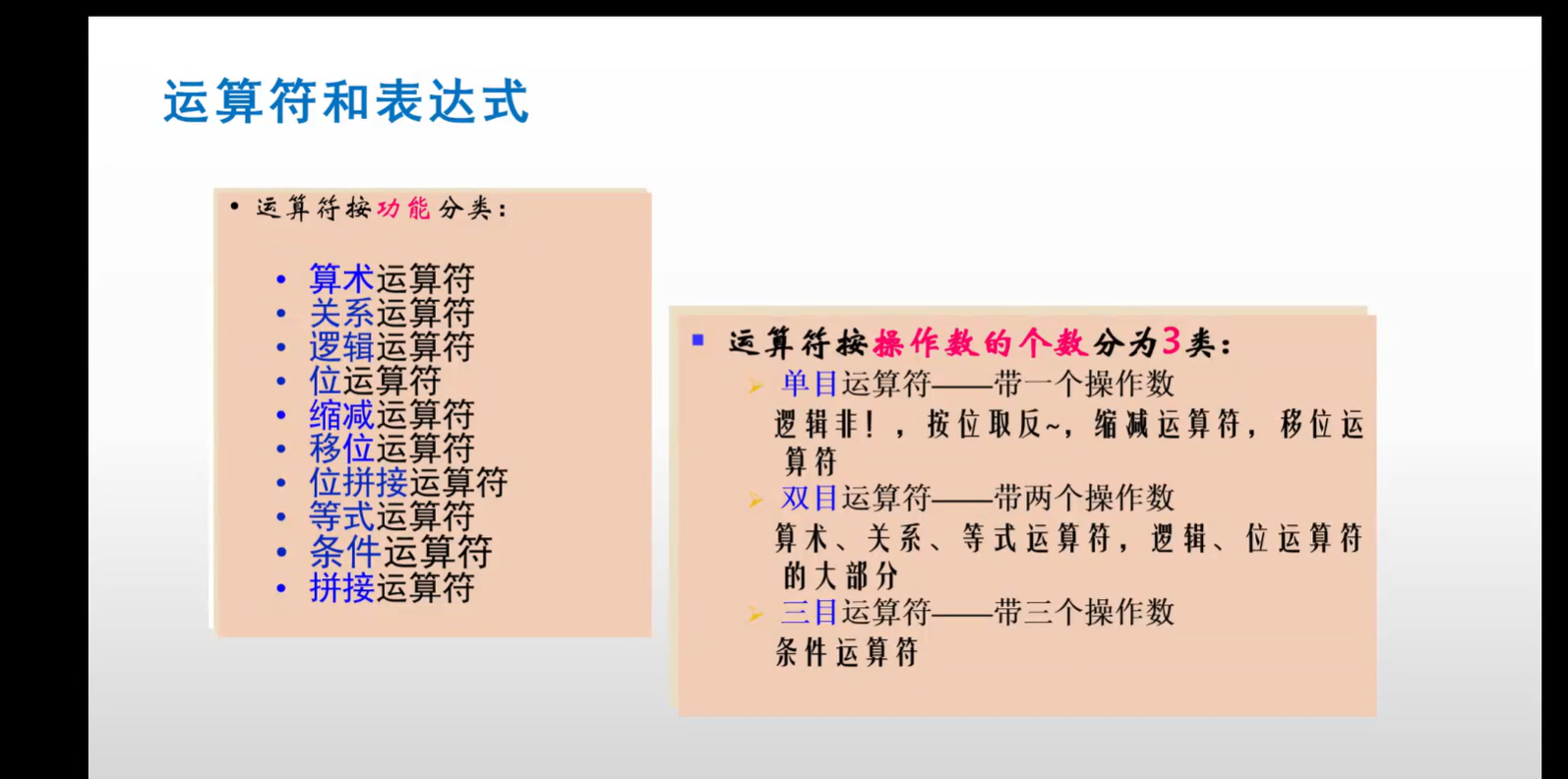

运算符和表达式

算数运算符

算数运算符 | 说明 |

+ | 加 |

- | 减 |

* | 乘 |

/ | 除 |

% | 求模 |

进行整数除法运算时,结果值略去小数部分,只取整数部分;

%称为求模(或求余)运算符,要求%两侧均为整型数据;

求模运算结果值得符号位取第一个操作数的符号位;

进行算数运算时,若操作数位不定值X,则整个结果也为x

eg:x + a = x;

定义一个a,b都是[1:0]两位的,b是1,c是6

a=b+c a=7但是换算成二进制111 但是a是两位的二进制,故a为11舍弃了最高位的1

关系运算符

关系运算符 | 说明 |

< | 小于 |

<= | 小于或等于 |

> | 大于 |

>= | 大于或等于 |

运算结果值为1位的逻辑值1或0或x

关系运算时,若关系为真,则返回值为1

若声明的关系为假,则返回值为0

若操作数为不定值x,则返回值为x

所有关系运算符优先级别相同

关系运算符的优先级低于算数运算符

逻辑运算符(其结果只有一个)

PS:进行逻辑运算后的结果为1或0或x 大于1也是真

非零的操作数被认为是真(1'b1)

零被认为是假(1'b0)1'在其中的含义为一位的位宽

不确定的操作数如4'bxx00,被认为是不确定的(可能为0,也可能为非0)(记为1'bx),但4'bxx11被认为是真(记为1'b1,因为它肯定是非零的)

逻辑运算符 | 使用方法 | 说明 |

! | !a | a的非,若a为0,那么a的非是1 |

&& | a&&b | a与上b,如果a和b的值都为1,a&&b的结果才为1,表示为真 |

|| | a||b | a或上b,如果a或者b有一个为1,a||b的结果才为1,表示为真 |

&&和||的优先级高于条件运算符外,低于关系运算符、等式运算符等几乎所有运算符

逻辑!的优先级最高

eg:(a>b)&&(b>C)可简写为a>b && b>c

(a==b)||(x==y)可简写成 a==b||x == y

(!a)||(a>b)可简写成 !a||a>b

为了提高程序的可读性,明确表达各运算符之间的优先关系,建议使用括号

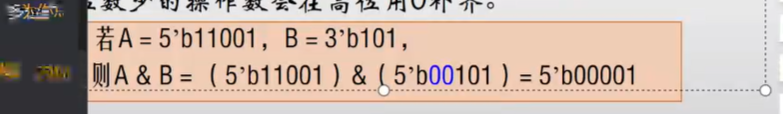

位运算符(前面操作数有几位,则输出就为几位)

位运算符 | 说明 | |

~ | 按位取反 | 单目运算符 |

& | 按位与 | 双目运算符 |

| | 按位或 | |

^~、~^ | 按位同或 |

比如a为11 b为00 a的第一个1和b的第一个0按位与 如此类推

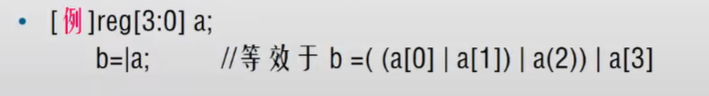

缩减运算符(与位运算符不同)

缩减运算与位运算类似,但运算过程不同

对单个操作数进行递推运算,即先将操作数的最低位与第二位进行与、或、非运算,再将运算结果与第三位进行相同的运算,依次类推至最高位

运算结果缩减为1位二级制数

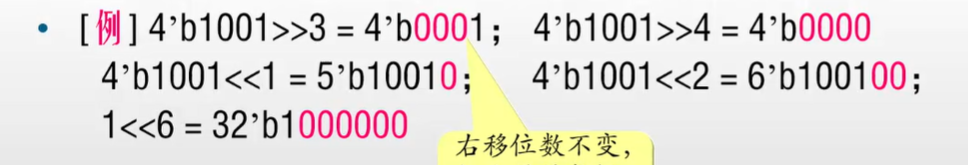

移位操作符

用法:A>>n 或 <<n

将操作数右移或左移n位,同时用n个0填补移出的空位

左移会扩充位数

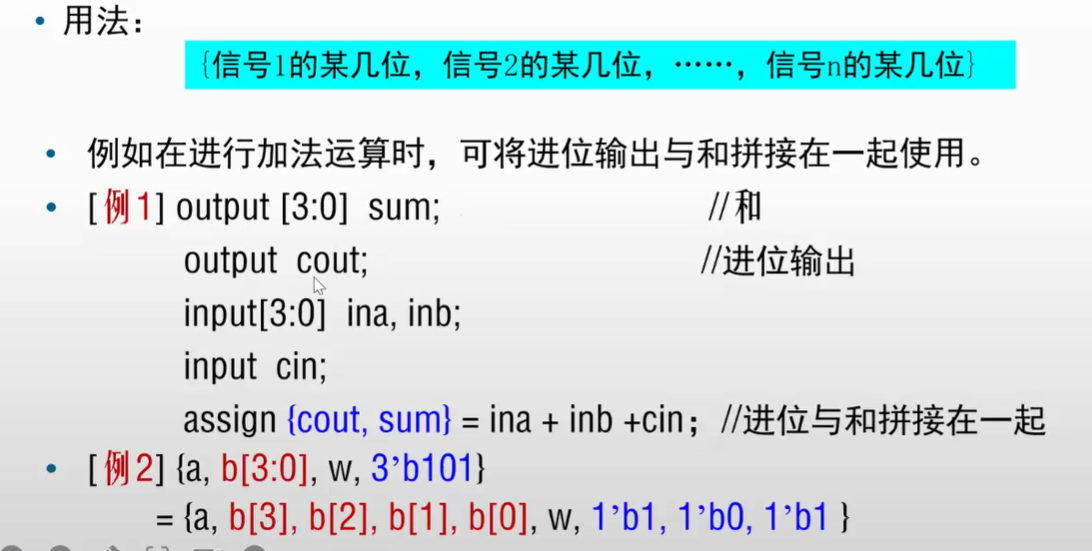

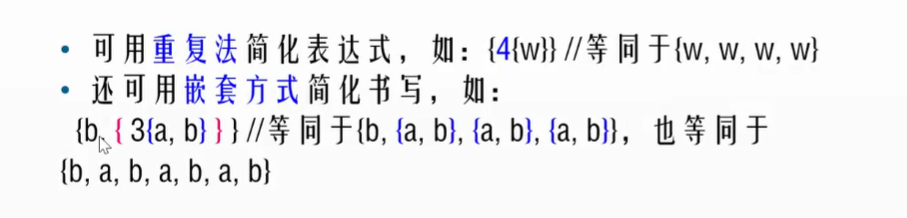

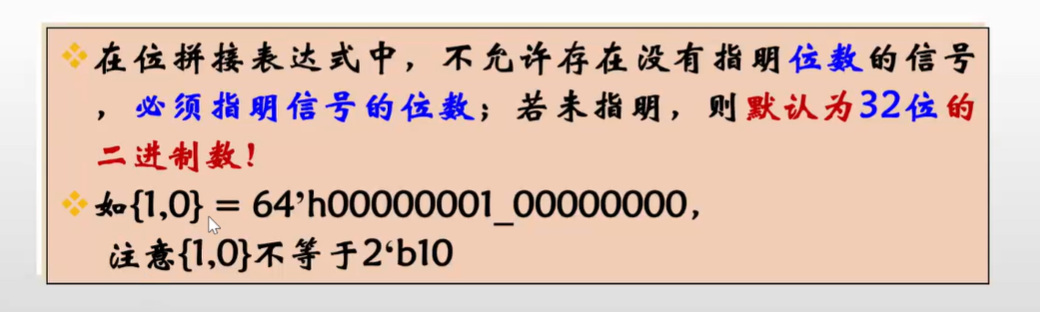

位拼接运算符

位拼接运算符为{}

将两个或多个信号的某些位拼接起来,表示一个整体信号

表示重复的表达式必须位为常数表达式

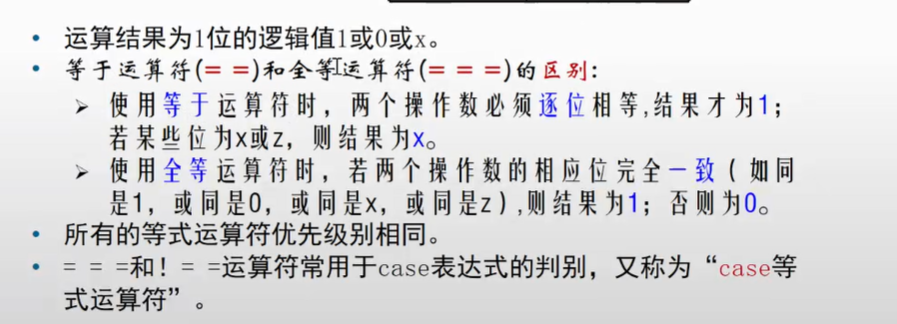

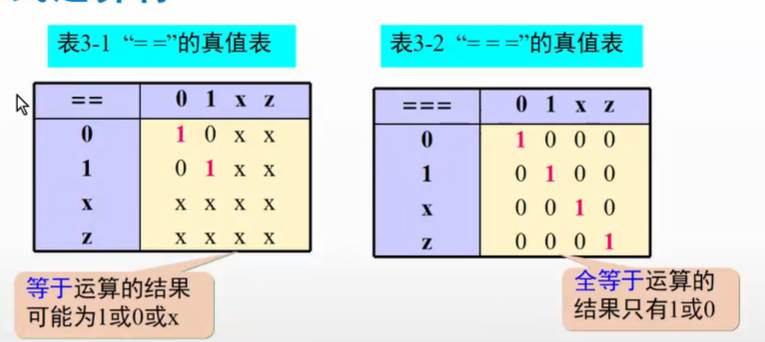

等式运算符

运算符 | 说明 |

== | 等于 |

!= | 不等于 |

=== | 全等 |

!== | 不全等 |

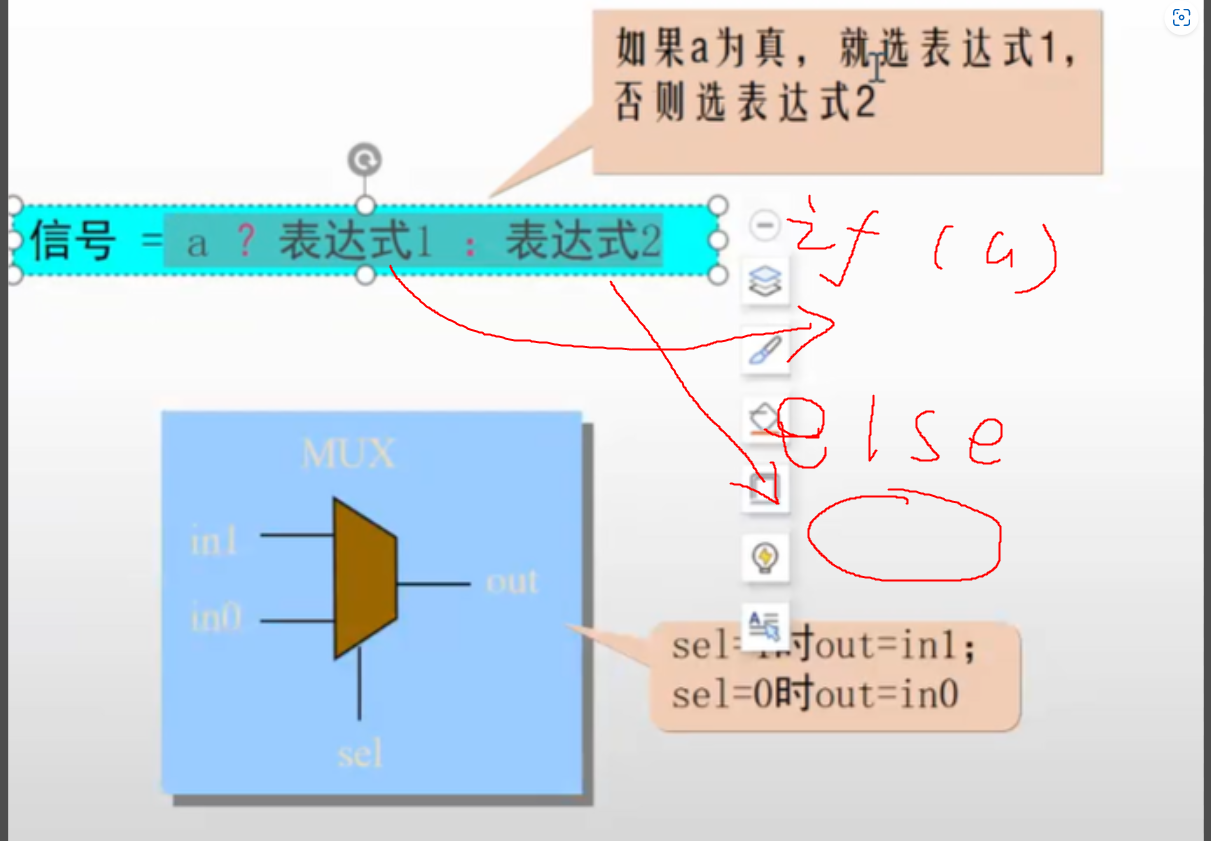

条件运算符

运算符的优先级(不要去挑战编辑器,不要给自己挖坑,用括号来控制运算的优先级)

条件赋值语句 out = sel ?in1:in0

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?