一、准备好图片转数据采集工具和bin文件转bit文件

链接:https://pan.baidu.com/s/1BTAbD2-2F9m9MF_dUpV_qw

提取码:BB73

二、采集数据

1.打开图片采集工具

2.编辑--->>添加图片

3.选完图片可以看到你的图片的大小。

我的是240*240的(这个大小很重要,要记住!),建议自己修改一下大小,通过电脑自带的画图软件就可以,详细步骤搜百度就可以找到。

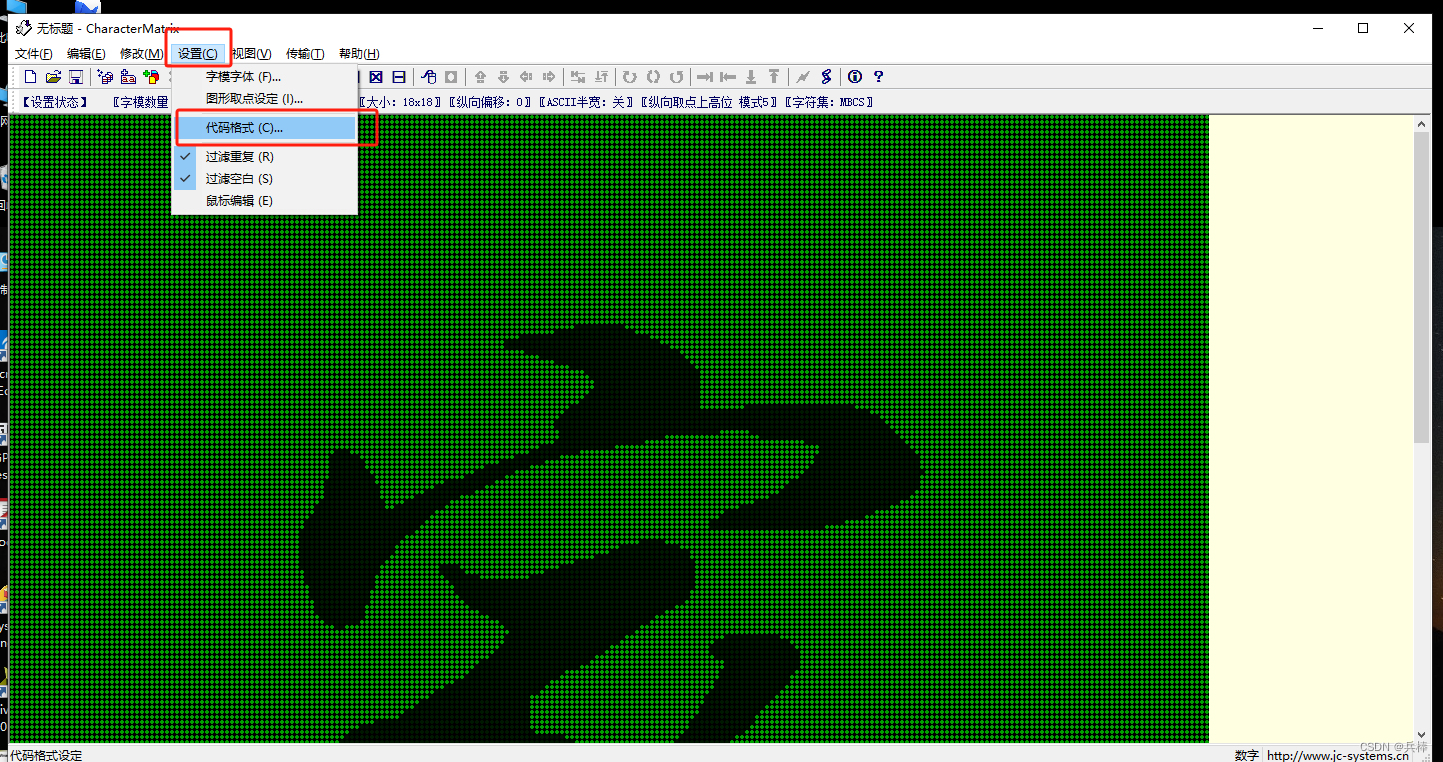

4.选择设置-->>代码格式

5.如下图选择就行。

6.编辑-->>导出字库

7.不需要索引表,直接选否

三、将刚刚的bin文件转换成txt文件

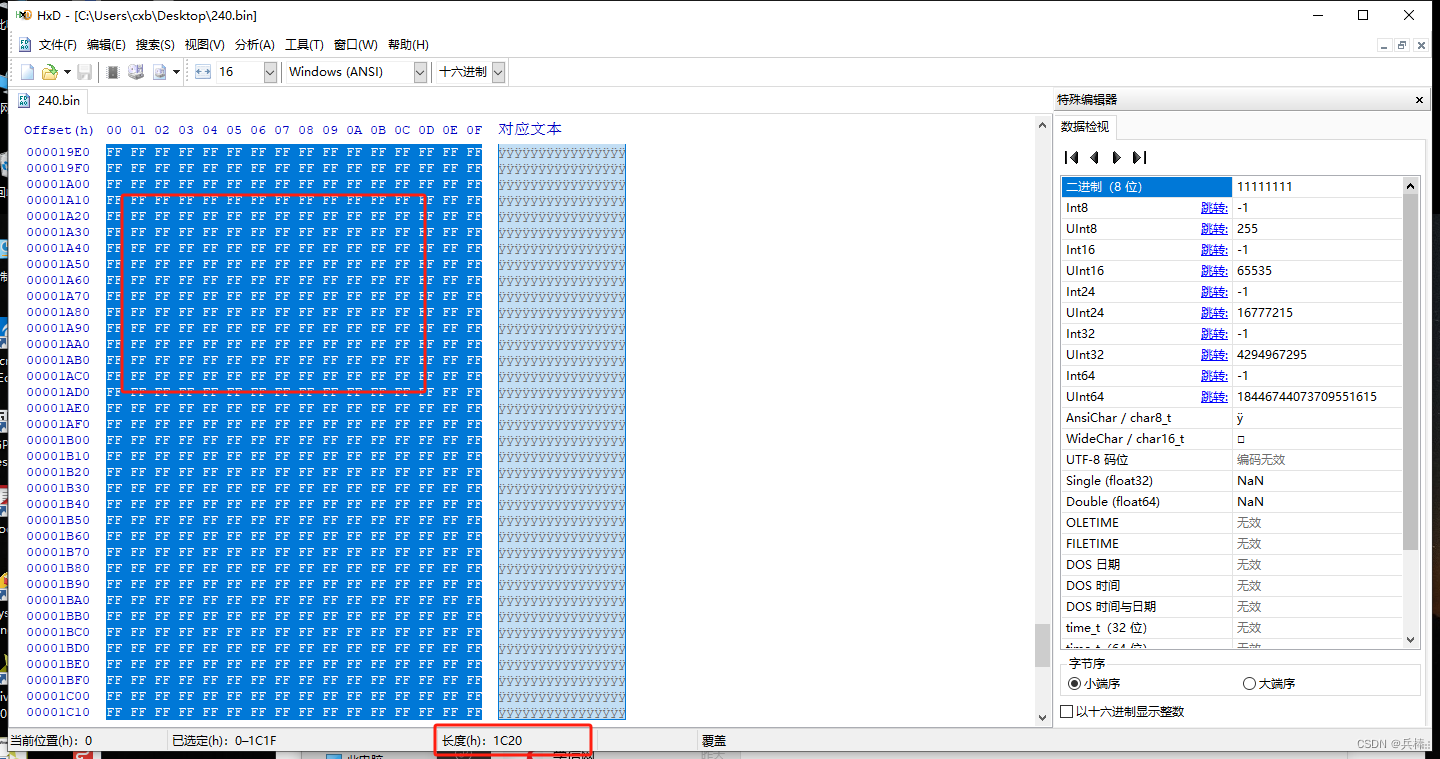

1.打开HxD,自己选一下系统有32和64的

2.打开刚刚生成的bin文件,按图选择相应的数据

3.全选复制,注意下脚有一个数据1C20,这是所有十六进制的总长度,后面代码中需要将数值写入进去。

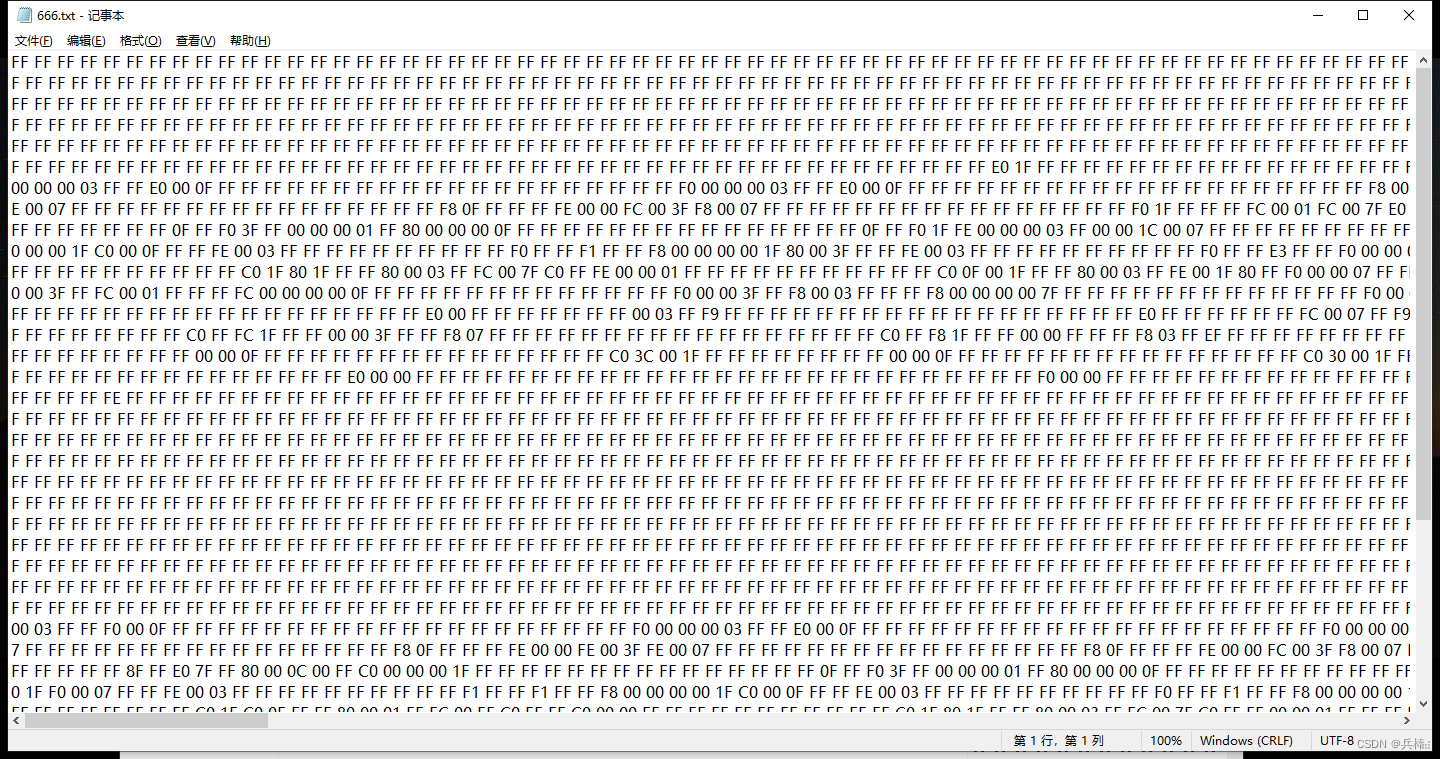

4.创建一个txt文件,将代码全都粘贴进去,然后保存

四、vivado代码实现

代码的话,只需要建立一个仿真文件就行,其他的不需要。

值得注意的是刚刚让你记住的两个数值,一个是图片的行大小240,和十六进制数据1C20(十六进制)=7200(十进制),然后根据你自己的数据大小更改一下代码中的 picture_bytes和picture_width。

再需要更改的就是路径了,将你的txt文件路径与我的更改一下就行了$readmemh("D:/matlab_data/666.txt",mem_data);

记住把“\”改成“/”就可以仿真了。

`timescale 1ns / 1ps

module tb_picture();

//根据要显示的图片进行调整

parameter picture_bytes = 7200;//图片的总字节数量

parameter picture_width = 240;//图片的宽度(像素数量)

parameter dataBit_with = 8;//数据宽度

parameter addr_with = picture_bytes;//数据深度即图片的字节数

parameter total_dot_nuber = picture_bytes * dataBit_with;//图片的数据总bit数

parameter picture_length = total_dot_nuber / picture_width; //一列数据的bit数

parameter pictureLengthBytes= picture_length / dataBit_with;//一列数据的深度

parameter addr_stop = addr_with - pictureLengthBytes;//数据列计数时的最大值,因为地址时从0开始计数,一次性加的值是pictureLengthBytes

parameter ClockPeriod = 10; //定义仿真时钟周期100M

parameter ClockPeriodNumber = picture_bytes; //定义仿真时钟周期个数

reg clk_i;

reg [31:0] i;

wire [picture_length - 1:0] data_in;//读取的图片数据

wire [picture_length - 1:0] data_out;//显示仿真图片的变量

reg rst_n;

reg [31:0] addr = 0;

reg [31:0] test_reg;

reg [dataBit_with-1:0] mem_data[0:addr_with-1];// addr_with是地址深度,data_with是数据宽度

//产生固定的仿真周期数量,显示图片一次即可

initial begin

clk_i = 0;

repeat(ClockPeriodNumber*2)

#(ClockPeriod/2) clk_i = ~clk_i;

$stop;//$finish;

end

//读取文本型的16进制点阵字符

initial begin

$readmemh("D:/matlab_data/666.txt",mem_data);//读取十六进制数据位置

end

//拼接高位在前,低位在右

generate

genvar m;

for( m = 0; m < pictureLengthBytes; m = m + 1 )//generate for模块复制

begin : gfor_block

assign data_out[(dataBit_with * m + dataBit_with - 1 ): (dataBit_with * m)] = mem_data[addr + pictureLengthBytes - 1 - m];

end

endgenerate

//控制何时停止更新地址

always@(posedge clk_i )

begin

if(addr < addr_stop)begin

addr <= addr + pictureLengthBytes;

end

end

endmodule代码参考的是这位仁兄的,大家可以去看看利用FPGA仿真软件modelsim仿真波形显示图片_modelsim仿真结果图怎么导出_wetells的博客-CSDN博客

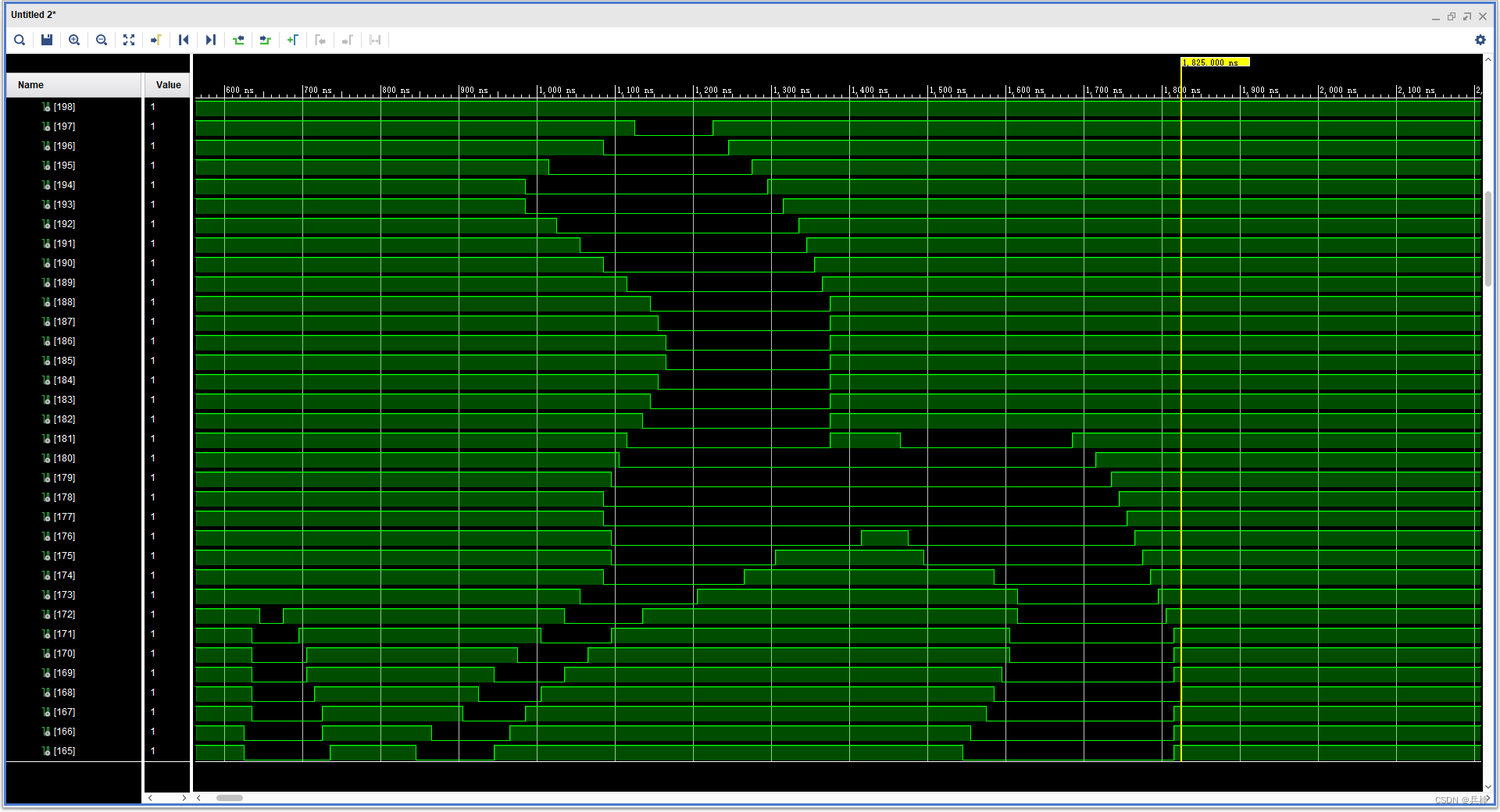

五、调整一下大小就可以出来了

我的字是“家”,有点大了就没有显示出来 如果成了就回来点个赞

如果成了就回来点个赞

3184

3184

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?