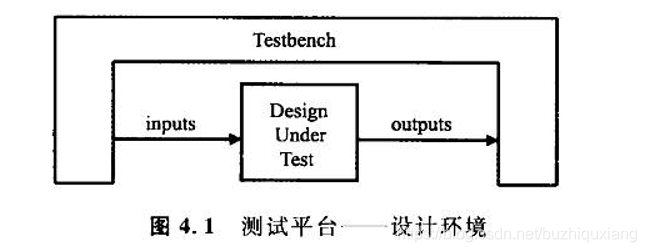

1/测试平台与DUT之间的通信

在传统verilog中,测试平台的代码独立于设计代码,处于不同的模块中,但是使用模块来保存测试平台经常会引起驱动和采样的时序问题。所以systemverilog引入了程序块program block,从逻辑上和时间上分开测试平台。

模块之间的连接采用接口,是systemverilog中一种代表一捆连线的结构。(接口可以像模块那样例化,也可以向信号一样连接到端口)

使用端口的仲裁器模型(由于systemverilog 中reg类型可以像wire一样连接块,为区别verilog中的reg类型,logic(单驱动))

module arb_port(output logic[1:0] grant,

input logic reset,

input logic [1:0] request,

input logic clk);

...

endmodule

使用端口的测试平台(测试平台通过端口与设计连接)

module test(input logic [1:0] grant,

output logic [1:0] request,

input logic clk,

output reset);

initial

begin

@(posedge clk) request<=2'b01;

$display("@%0t:req=01",$time);

...

$finish

end

endmodule

顶层连接测试平台和DUT,并且含有一个简单的时钟发生器(clk generator)

最后,采用例化的方式

module top;

logic [1:0] grant,request;

bit clk,rst;

always #5 clk=~clk;

arb_port a1(grant,request,rst,clk);

test b1(grant,request,rst.clk);

endmodule

但是真实的设计往往有数百个端口信号,声明信号和端口复杂困难

可以采用接口简化连接

interface arb_if(input bit clk);

logic [1:0] grant,request;

logic rst;

endinterface

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2182

2182

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?