1、综合策略

(1)top-down:层次化结构,只对顶层设计进行全面约束,针对个别模块有特殊约束;比如管理模块(clock模块,reset模块等)的综合不会与工作模块(顶层模块)放在一起综合的

(2)bottom-up:对底层的各个模块定为current_design,进行综合,加上dont touch属性;若各层之间有group logic(如与门),还需要对group logic约束;这种风格的综合约束复杂且多

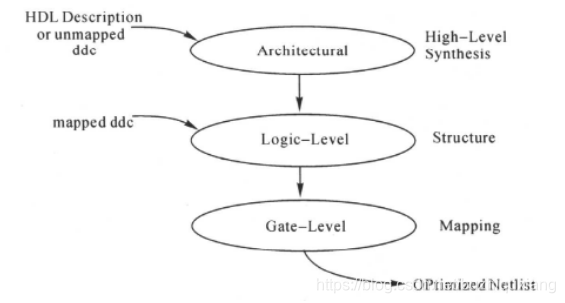

2、三个阶段的优化

第一阶段的结构级的优化(Architectural-Level Optimization)

第二阶段的逻辑级优化(Logic-Level Optimization)

最后阶段的门级优化(Gate-Level Optimization)

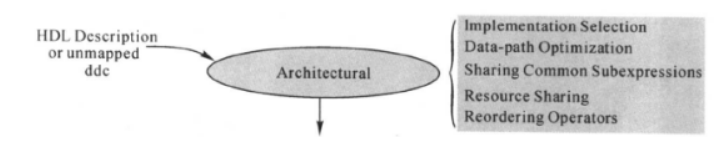

(1)结构级优化(architectural-level)

包括:设计结构的优化,数据通路的优化,共享共同的子表达式,资源共享,重新排序运算符号

包括:设计结构的优化,数据通路的优化,共享共同的子表达式,资源共享,重新排序运算符号

例如:加法器有普通加法器,超前进位加法器,DC会根据应用场合挑选出合适的加法器

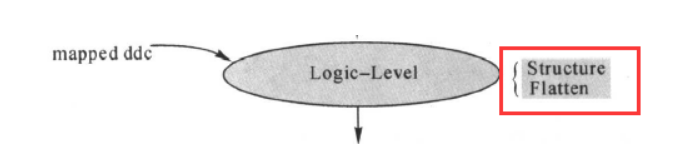

(2)逻辑级优化(logic-level)

一个逻辑表达式可以是与非格式,也可以是或非格式,DC会选择合适的逻辑表达式来描述逻辑功能

(3)门级优化(Gate-level)

得到网表后的优化,局部优化。网表文件生成后,静态时序分析时,DC工具对路径进行分析,对关键路径进行优化,逻辑级优化与门级优化可以迭代使用(若路径延时过大,不满足设计规则,DC会resynthesis,一直到路径延迟满足要求)。

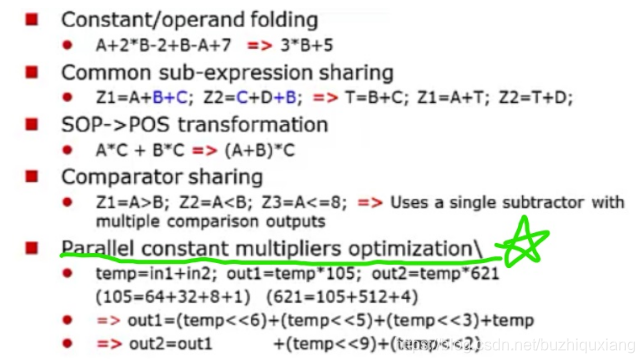

常见的算术优化方法:

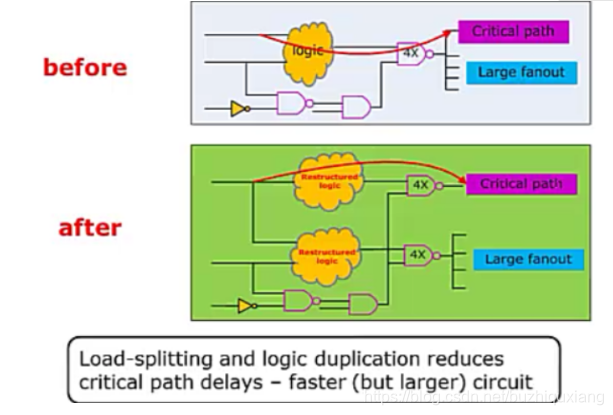

逻辑复制(logic duplication):

对关键路径部分的负载放在其他路径上,减少关键路径延时,以面积换速度

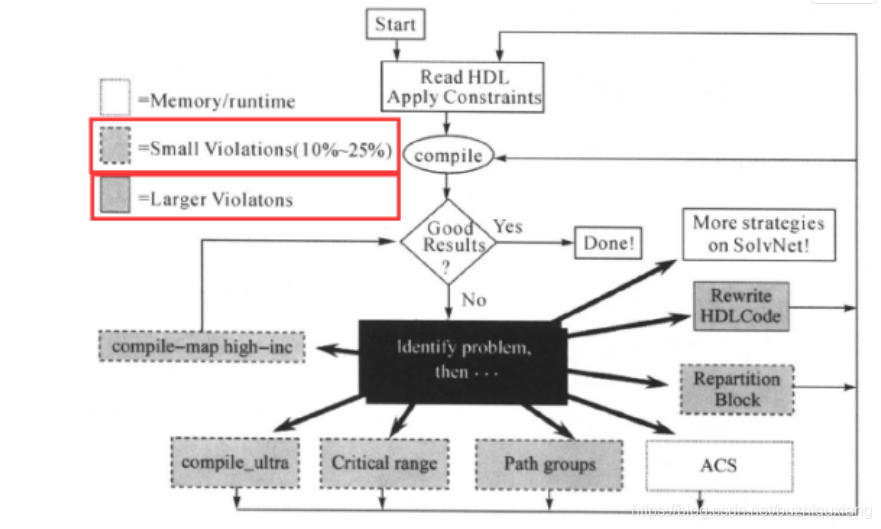

DC综合之后,我们查看详细的报告,如果没有违规,设计既能满足时间和面积的要求又不违犯设计规则,那么综合完成。可以把门级网表和设计约束等交给后端(backend)工具做布局(placement )、时钟树综合(clock tree synthesis)和布线(route)等工作,产生GDSII文件。如果设计不能满足时间和面积的要求或违犯设计规则等,就要分析问题所在,判断问题的大小,然后采取适当的措施解决问题。问题往往是时序的问题,发生时序违规时可以采取相应的措施,如下图所示:

(1)当违规得比较严重时,也就是时序的违规(timing violation)在时钟周期的25%以上时,就需要重新修改RTL代码了

(2)时序违规在25%以下,有下面的时序优化方法:

- 使用compile_ultra命令(在拓扑模式下运行)

compile_ultra跟compile一样,是进行编译的命令。compile_ultra命令适用于时序要求比较严格,高性能的设计。使用该命令可以得到更好的延迟质量( delay QoR ),特别适用于高性能的算术电路优化。该命令非常容易使用,它自

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1129

1129

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?