一、FPGA背景信息

当前的FPGA市场上有国际和国产两大体系,国际排名,一直很稳定,国际上前三名Xilinx、Altera、Lattice,国内FPG厂商也在填补空白,低端、中低端市场上发力,替代潮流已在兴起,目前国内前五,分别是京威齐力、安路科技、广州高云、复旦微电子、西安智多晶,国货当自强,真的很厉害。

FPGA随着人工智能、大数据、云计算、数据中心而越发收到重视,对于我们硬件工程师来说是利好消息。

硬件工程师设计一款产品或功能模块,采用FPGA为主体核心,从方案初定、评估选型、最小系统、模块搭建、绘图、制版、调试、测试,顺应行业发展,添一把力。

二、JTAG下载电路模块

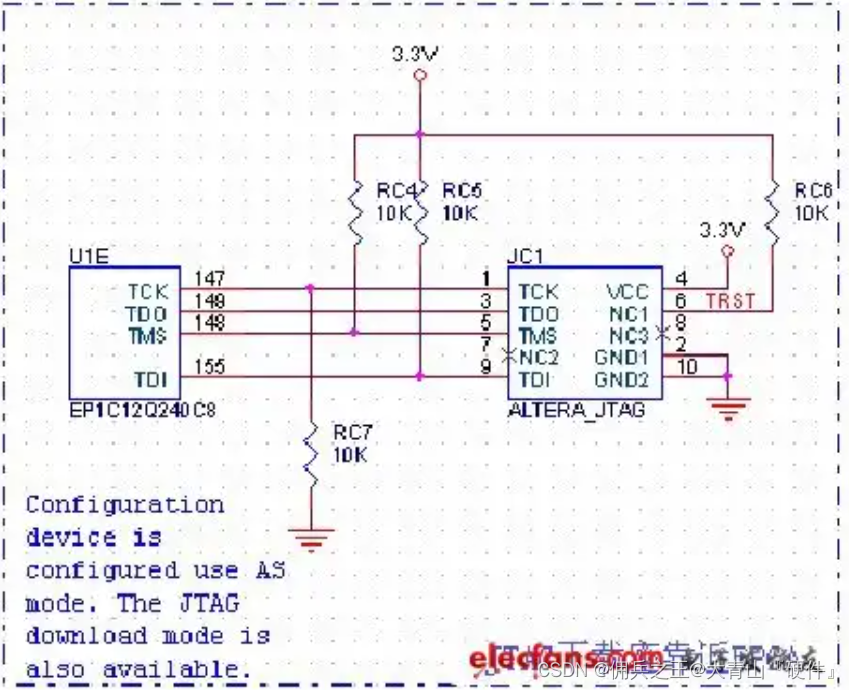

今天着重看看Altera的JTAG下载电路模块。如下图所示,是标准的JTAG电路。

Altera的MAX系列、Cyclone系列、Arria系列、Stratix10系列,都是使用该电路。

为什么有些引脚加上拉电阻、有些引脚加下拉电阻、有些引脚悬空呢?

难道都是随便接的吗?带着这样的疑问,我们继续向下看。

这和Altera-FPGA芯片的datasheet资料有关,资料显示

| 序号 | 引脚名称 | 引脚含义 | 禁用状态 |

| 1 | TCK | 下载器产生并输入到FPGA 上升沿和下降沿时,进行操作 内部有弱下拉 | TCK=L,禁用JTAG |

| 2 | TDO | 测试数据从FPGA传输到下载器 | TDO悬空,禁用JTAG |

| 3 | TMS | 测试模式选择 内部有弱上拉 | TMS=H,禁用JTAG |

| 4 | TDI | 测试数据从下载器到FPGA 内部有弱上拉 | TDI=H,禁用JTAG |

通过上面的图表,可以发现,当JTAG被禁用时,4个引脚的默认状态,再比对上面的电路图,是不是就知道为什么了吧!

7815

7815

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?