4.2输入与显示部分

4.2.1液晶显示

液品显示作为单片机的外围电路,起着提供人机交五界面和提供系统运行状态的作用,市面上的液晶显示屏很多,大多都已集成了液晶显示控制电路。选用何种控制芯片的显示屏就决定了液品显示屏的工作方式。根据本设计需要选用了精工的MGLS 19264 液品显示屏。该液晶显示屏内置2块HD61202U液晶显示驱动控制器。这种液晶显示屏电路简单,价格便宜,并且易于操作。

其中CSA,CSB作为左、右屏片选信号,接单片机 A8、A9脚,同时单片机用地址A1作为 R/W信号控制数据总线的数据流向:用地址AO作为 D/I信号控制寄存器的选择;E信号出单片机的读信号 RD和写信号 WR合成产生。从而实现计算机对内置HD61202U 图形液品显示模块的电路连接。电位器用于显示对比度的调节。由图可知,液晶显示左半屏命令字地址为 0EOOH;状态字地址为 OEIOH:写显示命令字地址为 0EO1H;读显示命令字地址为 0E11H;右半屏对应地址为 0D00H、0D10H、0D01H、0D11H。

4.22键盘

本系统因为测量装置需要设置输出波形、频率等参数,所以需要设置键盘键盘采用外接软键盘,使用软件扫描的方式获得按键信息,因为按键需要去担动,这些都以软件编程的方式实现,这样可以节省硬件资源,使电路变得简单。

4.3 微处理器控制部分

基于DDS的波形发生器的微处理器部分主要完成三个功能:

(1)接收输入的波形参数、控制信号

(2)频率控制字的换算

(3)产生一些控制信号。

本课题中的微处理器-采用AT89C51单片机芯片,主要的接口有四个微处理器与扩展芯片之间的接口:微处理器与FPGA 模块的接口,微处理器与键盘、显示模块的接口。

4.31复位电路

这果所说的复位是指单片机复位,也称系统复位。复位使单片机在开始工作之前所处的一种预备状态,单片机只有以这个状态为起点,后面的工作才是正常的,因此,单片机在每次上电时必须复位。对于 89C51 单片机而言,通常在其RST引脚上保持10ms 以上的高电平就能使单片机完全复位。为了达到这个要求,可以有很多方法。本设计中使用的是如图4-3 的接法。 这种复位电路的工作原理是:按键按下时,电容E1两端相当于短路,RST引脚上为高电平,然后电源通过电阻R1对电容E1充电RST端电压慢慢下降降到一定电压值下,即为低电平,单片机开始正常工作。

复位操作的主要功能是把 PC初始化为 0000H,使单片机程序存储器从0000H单元开始执行程序。此外,复位操作使 PO~P3这些引脚变成高电平,还会对内部的一些单元产生影响。

4.3.2频率控制字计算方法

如前所述,微处理器另外一个重要的功能就是把用户设定的输出频率转换为二进制的频率控制字,送入到DDS主通道中。在本课题的前期设计工作中用户在键盘上设定的不是选择的输出频率,而是频率控制字的十进制表示,所谓的转换只是把键盘输入的十进制数转换成它的二进制形式送入到累加器中进行运算。这种方法唯一的优点就是算法简单、快速,但它的直观性非常不好,使用户不清楚输出的频率,所以在设定频率控制字的时候比较模糊。在此基础上,本文使用了一种直观性强的输入方法”。这种输入方法和一般的仪器非常相似,操作起来非常符合人们的习惯。

本课题的输出频率的相对带宽较宽时钟频率f-40M,经FPGA内部的PLL倍频可达80M,相位累加器位数 N32,输出频率在理论上可以达到0~40M,工程上也可以达到0~30M,频率分辨率可达0.019Hz。如何兼顾频率控制字的准确性、仪器操作的简单性与编程的简单可靠性,是仪器设计者必须解决的一个问题。为此,我们参考其它同类仪器进行了设计。我们允许的频率单位可以是Hz,KHz,MHz 三种,同一频率可以用不同的单位键入,可以保留三位小数。如:1234KHz也可以输入为1234000Hz或1234MHz,K=107374.1824B*21=1099511623AB1099511624.B首先计算如下公式:

(41)

K=232/40*10=107.374182f(42) 其中,f表示用户键入的输出频率,K 表示计算出的频率控制字。出于单片机的计算能力较差,如果直接按照 4-1 式进行计算,将使计算很繁琐,占用时间也比较长,但忽略掉小数部分又使频率控制字不准确,从而影响输出频率的准确度。我们的做法如下:

设f=4.B(单位),则首先看单位,如果

(1)单位为Hz时:K-107.3741824B=KAB将K乘以220-1048576,得:

K。=107.3741824.B*22=112589990.26=112589904.B当B=0时,也就是输入的频率没有小数部分,则直接用式(4-3)计算。当 B≠0时,先将键入的值乘以 1000,再舍去前面常数项的低三位,则

(43)

K.=1125894.B(4-4)最后将K右移20位,取前四个字节即可得到误差极小的二进制频率控制字K。*这里的乘都是二进制的乘,写成十进制数是为了更容易的说明,至于此处的常数项和输入频率的十进制转二进制可以用一些经典的方法,如查表法等(2)单位为KHz时:K=107.374182AB*1000107374.182AB将K乘以210=1024,得:

K=107374.1824B*2=109951162.3AB109951162A.B45)当B-0时,直接用上式进行计算,最后将K右移10位,取前四个字节。当B≠0时,先将键入的值乘以 1000,同时将单位变成HZ,按B=时的

Hz 单位处理。

(3)单位为MHz时:K=107.3741824B*1000000=107374182AB当B=0时,直接用上式进行计算,最后将K右移10位,取前四个字节当B头0时,先将键入的值乘以1000,同时将单位变成KHZ,按B-0时的KHz单位处理。综上所述,本文给出整个频率控制字计算的程序框图。

对于上述方法,我们对它的输出结果进行了人工校验,发现误差非常小整个方法频率控制字计算准确、程序简单可靠、运行速度快(仅需整数乘法运算)已经成为本课题进一步研制的首选方案。

4.33FPGA与单片机的连接及控制程序

4.3.31FPGA与单片机的连接要控制DDS芯片使其输出一定频率相位以及其他参数的波形,就必须设计一个接口,通过这个接口向 DDS 芯片送控制字。我们先来看一下DDS芯片与MCU接口的一些特性。DDS芯片的控制字一共有23bit。其中8bit 是送给 DDS的频率控制字,还有 8bit 的相位控制字,还有7位是控制 DDS工作方式的控制字和设计波形参数的控制字。在控制字的传输上,两个8位的频率和相位控制字采用的是并行传输,当8位控制字都发送后单片机再传送一位控制字的触发位,使控制字可靠的传输给 FPGA。

由于单片机的输出管脚有限,所以需对管脚进行扩展,本设计中采用的是非常成熟的扩展方法:用8255芯片对单片机的管脚进行了扩展,8255的PA用来做相位控制字的输出,另外用8255的PB来做频率控制字的输出,PC是位可控的输出端,所以用它来做 DDS工作方式的控制字和设计波形参数的控制字的 输出管脚。

在接口电压的配置上,由于单片机和8255 片的输出电压是5V,而FPGA的输入电压是 3.3V,所以这里就需要一个电压上的转化,在这里,用74ALVC164245来完成16位控制字的电压转化,用74LVC4245来进行工作方式控制字和波形参数控制字的电压转化。 图4-5是单片机与FPGA连接电路图。

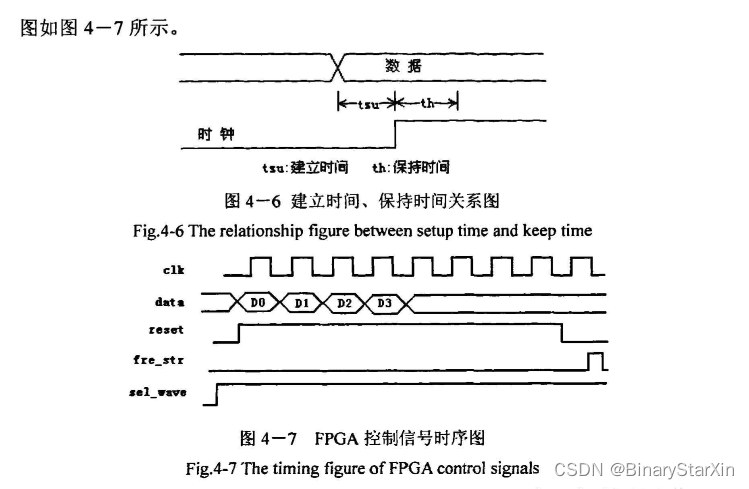

4.3.31FPGA控制程序设计 单片机程序核心部分就是对FPGA的控制部分,这部分直接影响到整台机器的工作,是整个程序设计的核心。根据第四章中介绍的,将配置文件传输到 FPGA 后,这时的 FPGA 就可以看成是一个独立的数字芯片。那么对数字芯片的控制,控制信号之间的时序关系是非常重要的,对于单独的一个信号,要准确地被芯片接受,就必须满足采样和保持时间。建立时间与保持时间的关系图如图4一6所示。

对于本设计中有复杂信号群出现的时候。在满足单个信号的建立和保持时间的基础上,确定信号间彼此关系就变得非常重要了,单片机的控制输出时序

CLK 是频率字接收模块的输入时钟端,DATA 是分别在四个周期输出的8位频率控制字,RESET是频率字接收模块的复位信号。FRESTR信号是频率控制字触发信号,高有效。SEL WAVE 是波形选择信号,被选波形的相应端应为高电平。必须保证信号间的时序正确,频率字接收模块才能正常工作。

4.4FPGA下载电路设计

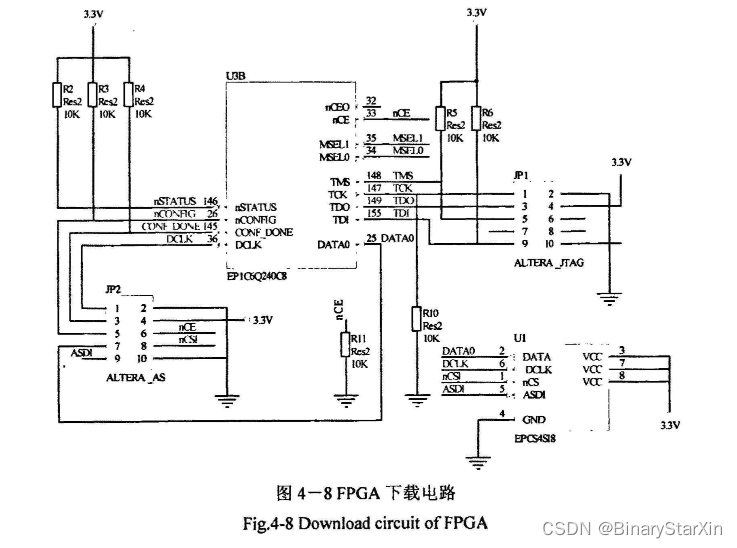

芯片的下载!~是指将芯片的配置文件输入到FPGA器件中,从而完成对芯片的编程,使芯片实现指定功能。Altera 公司为不同系列器件提供了不同的编程与配置方式,常用的下载方式有 BitBlaster 下载、ByteBlaster 并行下载以及ByteBlasterMV并行下载。 本设计选用了ByteBlasterMV并行下载方式,实际上Altera公司的器件在实际应用中大都采用这种下载方式,这种下载方式支持两种数据下载模式:主动串行同步(AS)模式和JTAG模式。

本设计选用了两种模式混合的方式,图4-8 即为本设计中用户板上AS与JTAG的混合模式下进行配置的原理图。

在使用JTAG模式进行下载时ByteBlasterMV并行下载电缆两端的接口信号不同于AS模式下的接口信号,在进行编程/配置时所用到的数据信号是TCK,TDO,TMS 以及TDI。

JTAG与AS方式的主要区别:通过AS 方式,必须先将配置文件先下载到存储芯片中,而JTAG方式则直接将配置文件下载到FPGA的FLASH中,所以JTAG这种下载方式的电路简单,但每次掉电后,配置必须重新下载。而AS方式电路较为复杂,并且费用高。

4.5D/A器件及幅值调节部分

从RAM 中读出的波形幅度值,最终要经过 D/A 转换成相应的模拟阶梯波形,然后再通过低通滤波器输出。理想的DAC 是一个采样保持系统,一个数码被转换为一个模拟值并在整个采样周期内保持其值,在输出瞬间从一个模拟值变化到另一个模拟值。不幸的是,DAC 并不是理想的,它的输出具有有限的转换时间,存在相关码突变,这是一个短暂的输出误差,其幅度和宽度是输入编码的变化函数。本课题使用的DAC 器件是AD公司的9713B 100MBPS高速芯片,它有以下几个优点:速度快(100M 的转换速率)、精度高(12 位分率)、转换噪声低(SFDR1MHz:70dbc)、功耗低;ECL/TTL 电平兼容。

在数据输入时序上,其锁存信号是低电平有效,即在锁存信号 LATCH=0时,输入通道是透明的。锁存信号与输入数据应符合一定的时序关系小能被正确锁存。如下图所示,从图中可以看出,数据要被正确地接收,必须满足一定的数据建立时间和数据保持时间。

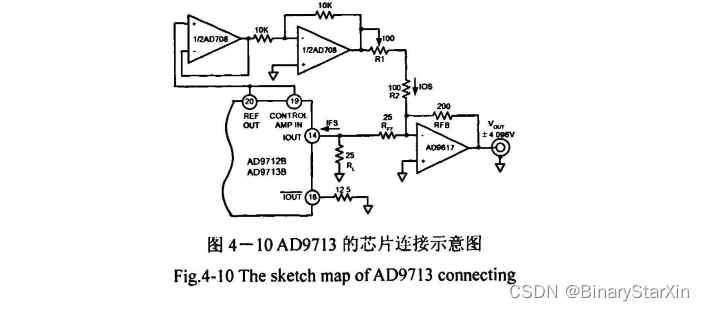

幅度调节电路是利用放大器AD708,AD9617和AD9713组成电路调节D/A 输出波形的幅度。电路如下图所示,这是一个电流反馈的高速放大电路。它把DAC输出的电流转化成电压,通过反馈电阻 R的DAC电流决定9617输出的幅度。R和 Re起分流作用,限制用于IV 转换的电流,同时在9713内部提供一个输出电压幅度。通过 R,的电流给 9617 输出端提供一个直流偏置,调节 R的阻值可以调整偏置电流的大小。整个放大电路最大的幅度是土4.096V,这里的土相对于参考电平。

其中R1选用X9318数字电位器。由按键对它的U/D端和INC端进行控制DDS系统的输出波形接到数字电位器的固定端和滑动端来改变滑动端在电阻阵列中的位置,从而改变数字电位器的阻值,使得输出波形的幅值得以改变。采用数字电位器取代传统的机械式电位器,不仅控制方便,而且还增加了系统的可靠性。

4.6滤波器部分

4.6.1滤波器的分类和选择

以离散数字序列经数模转换为模拟信号原理为基础实现的信号发生器有其固有的优点,但同时也具有频谱分量复杂,杂波多的缺点。在信号发生器中,滤波器起着保持有效分量、抑制杂波的作用。理想低通滤波器”的幅频特性和群延迟特性如图4-11所示。

实际上,理想的滤波器特性是不可能获得的,只能用某种方式按某种规律去逼近它。采用不同的曲线逼近理想滤波器,就获得了不同类型的滤波器。常见的滤波器有以下几种:Butterworth 滤波器Chebyshev 滤波器、椭圆滤波器“Bessel 滤波器和线性相位滤波器。

五种滤波器有着各自的特点:Butterworth 滤波器也称为最大平滑滤波器,它的传递函数只有实数极点和无穷零点,因而其幅频特性在通带和阻带内都是单调的,但也造成了通带到阻带的过渡缓慢:Chebyshev 滤波器的传递函数有复数极点和无穷零点,因而其幅频特性表现为有波动,其中ChebyshevI型为通带单调、阻带波动,ChebyshevII型为通带波动、阻带单调,Chebyshev 滤波器以引入纹波为代价,使其过渡特性比 Butterworth 滤波器要陡峭:圆滤波器也叫 考尔滤波器,它的传递函数有复数极点和(截止频率附近的)有限零点,因而其幅频特性在通带和阻带内都是波动的,但它的过渡特性最陡峭:Bessel 滤波器的传递函数只有实数极点和无穷零点,其幅频特性在通带和阻带内都是单调的,但它采用 Bessel 逼近来实现滤波器设计,在通带内具有线性相位或平坦延迟线性相位滤波器与 Bessel 滤波器相似,在其通带内具有线性相位的响应,但在整个通带内,滤波器的群延迟特性并不是单调的,而是引入了纹波,从而在整个通带内达到群延迟的均方误差最小。

由以上对滤波器的简介可以看出,椭圆滤波器具有最陡峭的过渡特性,线性相位滤波器在整个通带内具有整体最好的相位特性。设计中选用了这两种滤波器分别完成对F弦波和其他波形的滤波。滤波器组组成如图4-12所示

4.62滤波器电路实现

设计中,设计输出正弦信号频率上限为40MHZ。单频输出时,理想的频谱为一条单一谱线,但实际输出信号中必然有杂散分量存在。理论上杂散分量将从60MHz后开始出现,但由于频率的混迭,杂散信号将不仅仅局限于60MHz以上。此外,信号发生器作为信号源,其通带内误差总体最小,即均方误差最小。这就要求设计的滤波器过渡特性要陡峭,通带内幅频特性对理想曲线是致逼近。为此选用椭圆滤波器完成对正弦信号的滤波。

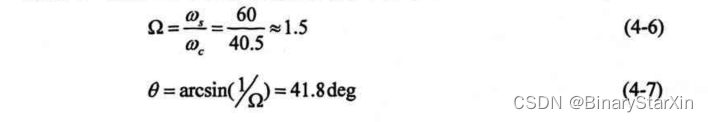

根据系统要求和实现上的可行性,确定滤波器参数如下:反射系数为5%即通带内最大纹波衰减4为00108dB,滤波器通带带宽为405MHZ,阻带

带边频率w为60MHz,阻带最小衰减A为60dB,两终端电阻为50欧姆采用归一化低通原型滤波器模型进行滤波器设计。

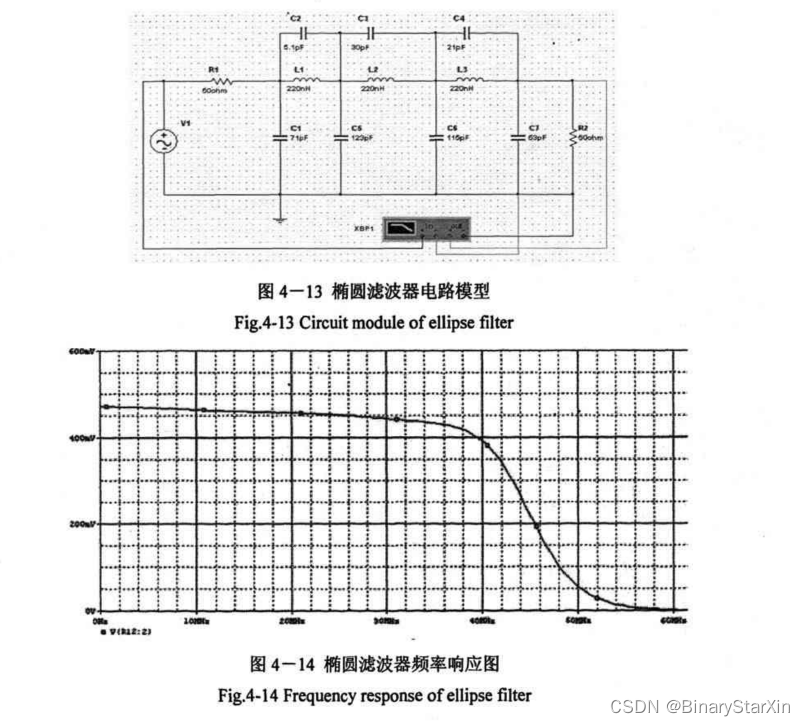

根据性能要求,查椭圆滤波器原型计算曲线,选0=43deg,@为40MHz。去归一化后,得到元件参数。按照得到的元件参数,根据电容、电感的实际可获得值,考虑电感O值有限和节点对地电容的影响,在PSPICE0中建立电路模型如图4-13所示,该模型仿真结果得频率响应如图4-14所示

与理论的O值无限大的情况相比可知:有限O值对频率响应的影响是使得滤波器的过渡带变长,截止频率提前,截止带的最小衰减变小。但由于滤波器设计中,技术指标留有充分的余量,使得最终获得的滤波器能满足系统对正弦波滤波的要求。

对于锯齿波和三角波,信号本身的频谱不再是单一的谱线,其谐波成分复杂,这时已经不能按输出信号重复频率来决定滤波的截止频率。由奈奎斯特采样定理可知:100MHz的转换率最大只能无失真地重建不超过50MHz的信号。在设计中,对复杂波形采用按采样率决定截止频率的方法,将滤波器的截止频率设定为40MHz。同时,为了正确地复现波形,通带内不同频率分量的延迟应尽可能保持一致,即滤波器相位和群延迟特性必须良好。满足以上要求的有Bessel滤波器和线性相位滤波器。其中,线性相位滤波器的群延迟特性具有等波动的起伏,其相位特性以等波动的方式逼近于线性函数。所以,通带内相位误差总体最小,即相位的均方误差最小。在具有相同的元件数的情况下,具有等波动误差的线性相位滤波器的群延迟特性比 Bessel 滤波器在更长的频率区间内近似为常数,其阻带衰减也相对陡峭。综合以上原因,选用线性相位滤波器完成复杂波形的滤波。

根据系统要求和实现上的可行性,确定滤波器参数如下:最大相移为0.05滤波器3dB带宽o为50MHz,阻带带边频率为120MH阻带最小衰减A为20dB,两终端电阻为50欧姆。

根据性能要求,采用归一化低通滤波器模型进行滤波器设计,查线性相位滤波器原型计算曲线,选0=25deg,为50MHz,最后采用6阶线性相位滤波器完成对复杂波形的滤波,查得各元件参数。根据所得参数,根据电容、电感的实际可获得值,考虑电感O值有限和节点对地电容的影响,在PSPICE 中建立电路模型如图4-15所示,该模型仿真结果得到频率响应如图4-16 所示。

4.7本章小结

本章依次介绍了组成仪器系统硬件的控制部分、输入和输出部分、DA幅度调节部分、滤波器部分以及FPGA的下载电路部分。电路实验结果表明,采用以上功能电路基本实现了项目对模拟通道的设计要求。

582

582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?