TIMING-10

:

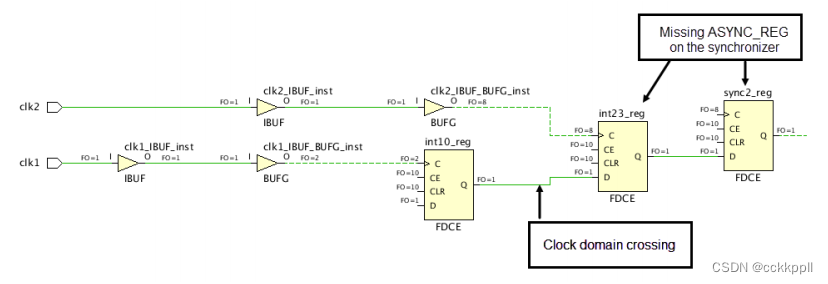

同步器上缺失属性

在

2

个时钟域之间已检测到

1

个或多个逻辑同步器

,

但同步器的

1

个或

2

个寄存器上并未定义

ASYNC_REG

属性。建议运行 report_cdc

以实现完整详细的

CDC

覆盖。

描述

同步器寄存器的

ASYNC_REG

属性必须设置为

TRUE

才能在综合与实现期间保留经过任意逻辑最优化的单元

;

并最优化其布局以实现最佳“平均故障间隔时间 (MTBF)

”统计数据。

解决方案

解决方案是向逻辑同步器的每个阶段添加

ASYNC_REG

约束。要获取

CDC

违例的详细列表

,

请运行

report_cdc

。只要前 2

个同步器寄存器中至少其一缺少 ASYNC_REG

属性

,

就会触发

TIMING-10

违例。

示例

在下图中

,

在

clk1

与

clk2

之间存在异步时钟域

,

通过双寄存器逻辑同步器已实现正常同步。但对此同步器的每个寄存器都必须应用 ASYNC_REG

属性以增大时序裕量并降低

MTBF

。

TIMING-11

:

含“

Datapath Only

”选项的最大延迟不适

用

在

<pin_name>

与

<pin_name>

之间已应用含

-datapath_only

的最大延迟约束。起点和端点属于相同时钟域或者属于 2

个时钟域

(

前提是这

2

个时钟域可一起安全定时

)

。仅建议在不存在已知相位关系的时钟间的路径上使用

-datapath_only 选项。在路径端点上找到同步器时

,

将豁免此

DRC

。

描述

set_max_delay

搭配

-datapath_only

选项可用于从建立时序裕量计算中移除时钟偏差

,

并忽略保持时序。

set_max_delay -datapath_only

命令用于约束满足以下条件的异步信号时序路径

:

(1)

无时钟关系

;

但

(2)

需要最大延迟。不建议在同步路径上使用此约束。

解决方案

解决方案是修改

set_max_delay -datapath_only

约束

,

以使其避免覆盖同步时序路径。请参阅消息中列出的起点单元和端点单元,

以查找关联的

set_max_delay

约束。

TIMING-12

:

已禁用“时钟再收敛消极因素移除”

描述

“

Clock Reconvergence Pessimism Removal (CRPR)

”

(

时钟再收敛消极因素移除

)

模式处于已禁用状态。不建议在此模式下执行时序分析,

因为过消极的时钟树延迟可能导致无法实现时序收敛。

CRPR

功能用于消除人为引发的消极因素

,

此类消极因素源自于时钟网络的公用部分中使用的最大和最小延迟。如果禁用 CRPR

,

则可能导致难以实现时序收敛。

解决方案

建议启用

CRPR

分析以确保设计包含准确的时序信息。用于启用

CRPR

分析的

Tcl

命令为

config_timing_pessimism -enable

。

TIMING-13

:

因路径分段而忽略的时序路径

由于管脚

<pin_name>

上的路径分段

,

某些时序路径不包含在报告中。为防止路径分段

,

应使用有效起点和端点列表来定义所有最小延迟约束和最大延迟约束。

描述

当时序路径细分为较小的路径以便定时时

,

即发生路径分段。当分别在属于无效起点和端点的管脚上定义最大和最小延迟约束时,

时序引擎对穿过节点的时序弧进行细分以便使各节点分别成为有效的起点和端点。强烈建议避免进行路径分段,

因为它会导致意外后果。这可能导致时序分析不正确或者硬件故障。

解决方案

在

set_max_delay

和

set_min_delay

约束中谨慎选择有效的起点和端点

,

尽可能避免路径分段。

1306

1306

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?