本章主要会回答以下问题 ?

- imx6u 的时钟源来自于哪 ?

- 为什么一个起始时钟源,最终分成了多路?

- 不同的时钟源是如何与外设对应起来的?(时钟树)

- 要配置内核时钟频率

- 有哪些步骤 ?

- 涉及到哪些寄存器 ?

目录

2、设置内核时钟主频(CCM_ANALOG_PLL_ARMn)

一、时钟系统详解

1、系统时钟来源

imx6u 的系统时钟来源于两部分:32.768KHz 和 24MHz 的晶振。

- 32.768KHz:RTC 的时钟源。RTC 用于提供精准的日期和时间,自带电池,不依赖外部电源

- 24MHz:内核以及其他外设的时钟源。(如串口、音视频、网络等设备)

其中我们要重点分析的是 24MHz 的时钟源。

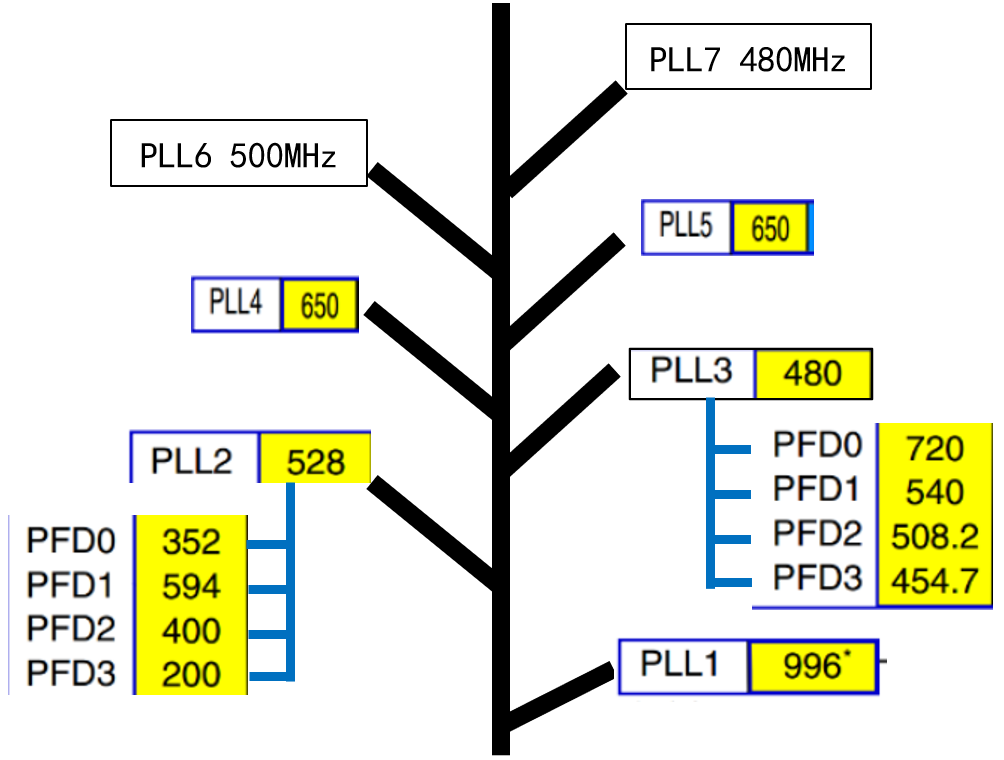

2、7 路 PLL 时钟源

PLL 表示倍频,imx6u 的主频默认是 396MHz,和上面说的 24 MHz 差了数十倍,原本的 24 MHz 经过放大才变成了 396MHz,这就是所谓的“倍频”。

为什么会有 7 路时钟源?因为不同外设对时钟的需求不一样,单纯的 24 MHz 无法满足外设需求,所以我们会对其放大(也就是 倍频),最终得到不同频率的时钟源。一共有如下 7 组时钟源:

| PLLx | 用途 | 频率范围 | 可否修改 | 备注 |

| PLL1 | ARM PLL。用于内核时钟 | 最高可达1.3GHz | √ | - |

| PLL2 | System PLL。一般作为内部系统总线的时钟源,比如逻辑处理单元、DDR、NAND | 固定22倍频,即 24 × 22 = 528 MHz | × | PLL_PFDx分路频率可被修改 |

| PLL3 | USB1 PLL。主要用于 USBPHY,可作为其他外设的根时钟源 | 固定20倍频,即 24 × 20 = 480 MHz | × | PLL_PFDx分路频率可被修改 |

| PLL4 | Audio PLL。主要用于音频接口 | 650MHz~1300MHz | √ | - |

| PLL5 | Video PLL。主要用于视频 | 650MHz~1300MHz | √ | - |

| PLL6 | ENET PLL。主要用于生成网络所需的时钟 | 固定20+5/6倍频,即24*(20 + 20+5/6) = 500MHz | √ | - |

| PLL7 | USB2 PLL。主要用于 USB2PHY | 固定20倍频,即 24 × 20 = 480 MHz | × | - |

需要留意一下 PLL2 和 PLL3,这两路在固定倍频的基础上,继续分了四路(PFD0 ~ 3),每一路的频率都不一样。

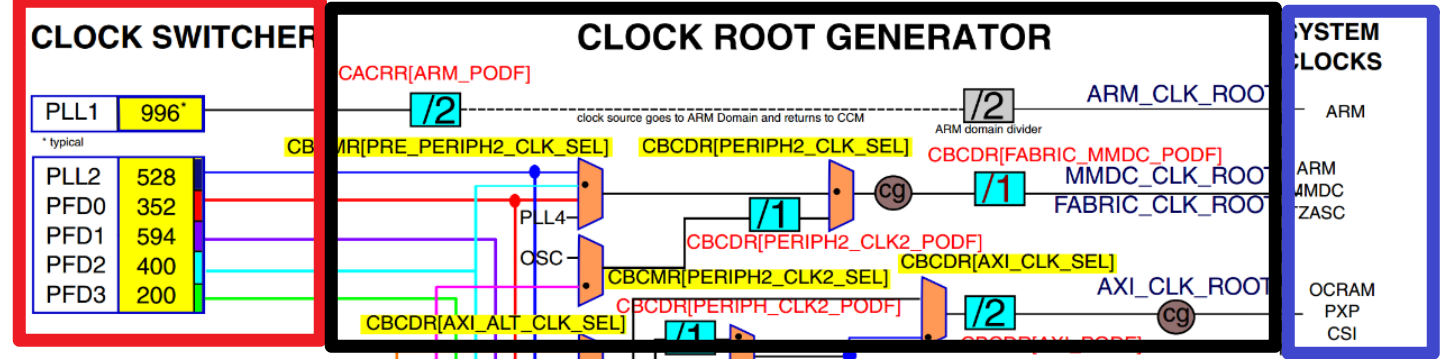

3、时钟树(时钟选择)

外设的时钟源基本上都来自这 7 路 PLL 以及一些 PFD。不同路的时钟源是如何与外设对应起来的呢?这就要涉及到时钟树了。在《imx6u开发手册》中有这么一个图,最左边是各路时钟源,最右边就是外设,中间比较复杂的就是选择器、分频器。

各路时钟源经过选择、分频来满足外设需求,最终将合适的时钟频率传递给外设。

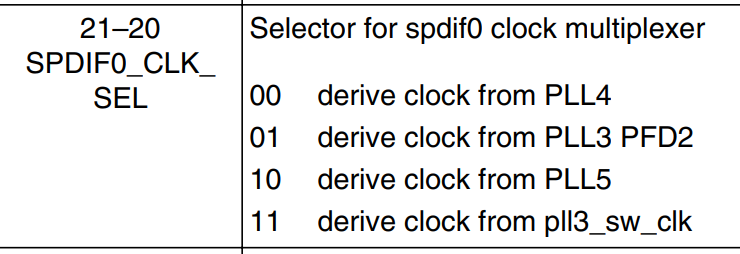

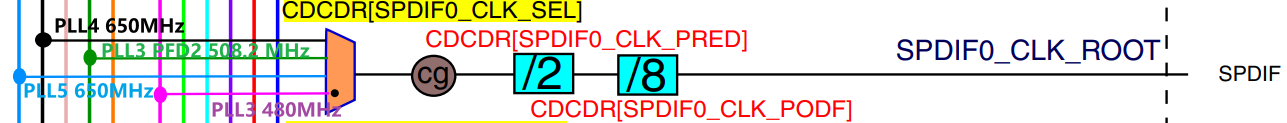

以下面这个外设 SPDIF 为例。 SPDIF 有四个可选的时钟源,分别是 PLL4、PLL3_PFD2、PLL5、PLL3。CDCDR 是选择器,选择哪一个时钟由 SPDIF0_CLK_SEL 位来决定

① 如果选择 PLL3_PDF2 路(508.2MHz),那就要将 CCM_CDCDR 的 21-20 设为 01

② 先经过二分频,结果就是 508.2 / 2 = 254.1 MHz

③ 然后再经过八分频,结果就是 254.1 / 8 = 31.7625 MHz

④ 最终进入到外设 SPDIF 的时钟就是 31.7625 MHz

二、内核时钟设置步骤

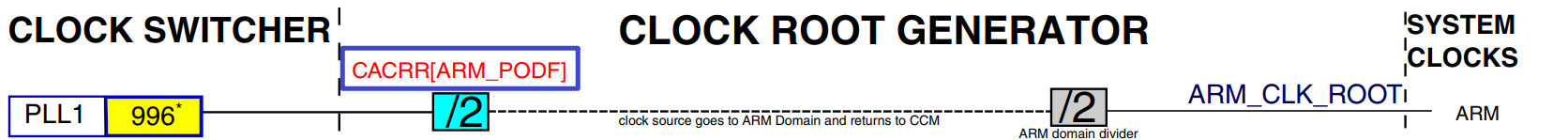

设置内核时钟,其实就是设置 PLL1 分路,PLL1分路默认是 996 MHz,经过2分频以后(498MHz)传递给内核。假设我们要将内核主频设为 528MHz,2分频,那么PLL1分路就是 1056MHz(< 1.3GHz)

设置内核时钟的步骤如下:

- 换上备用时钟。内核时钟就如同心脏,心脏停止,就等同于内核不会运作,所以我们在修改内核时钟的时候,需要换上备用时钟。

- 时钟输出使能,并设置时钟主频(PLL1分路)为1056

- 将时钟切换回内核时钟。

- 设置时钟树的分频器。到这步,PLL1的输出频率是 1056MHz,但是我们希望进入内核的频率是528MHz,因此需要设为 2 分频。

三、寄存器分析

1、切换至备用时钟(CCM_CCSR)

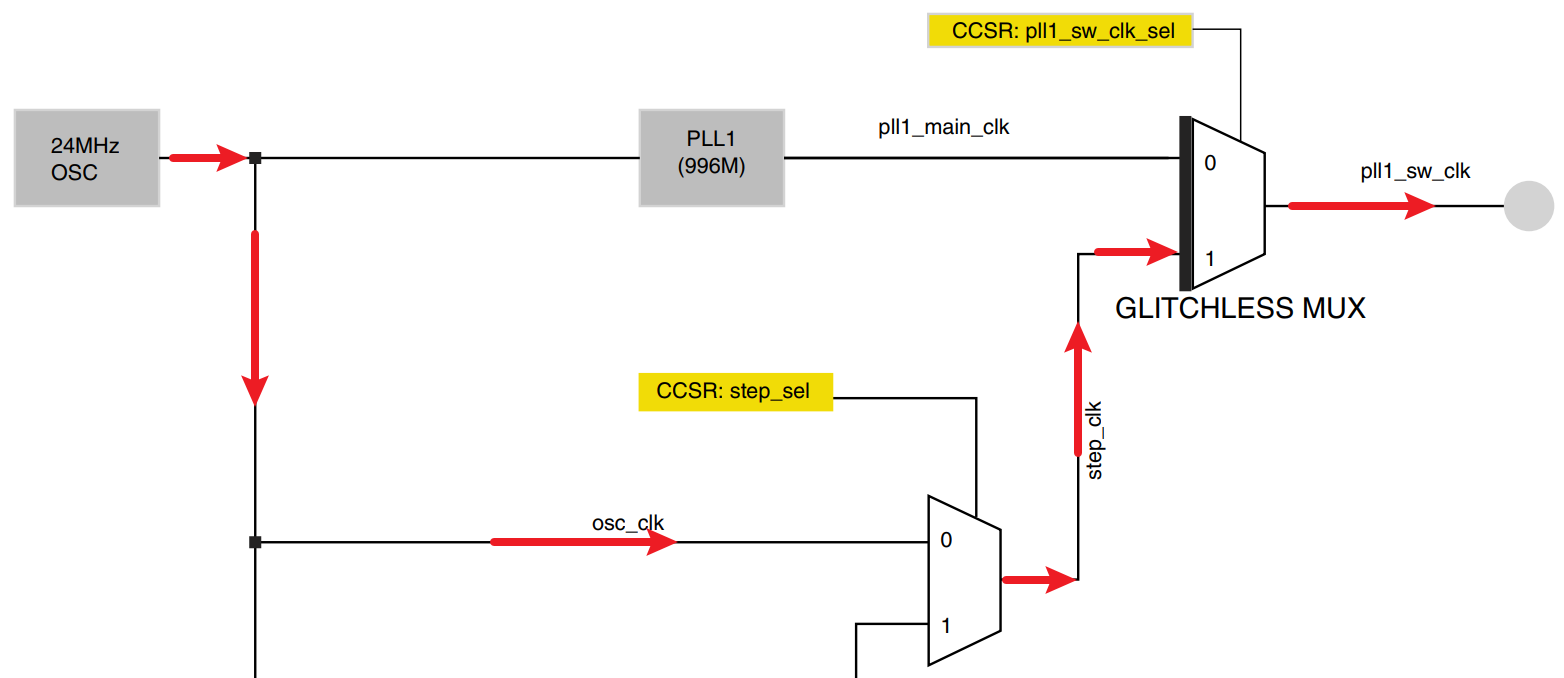

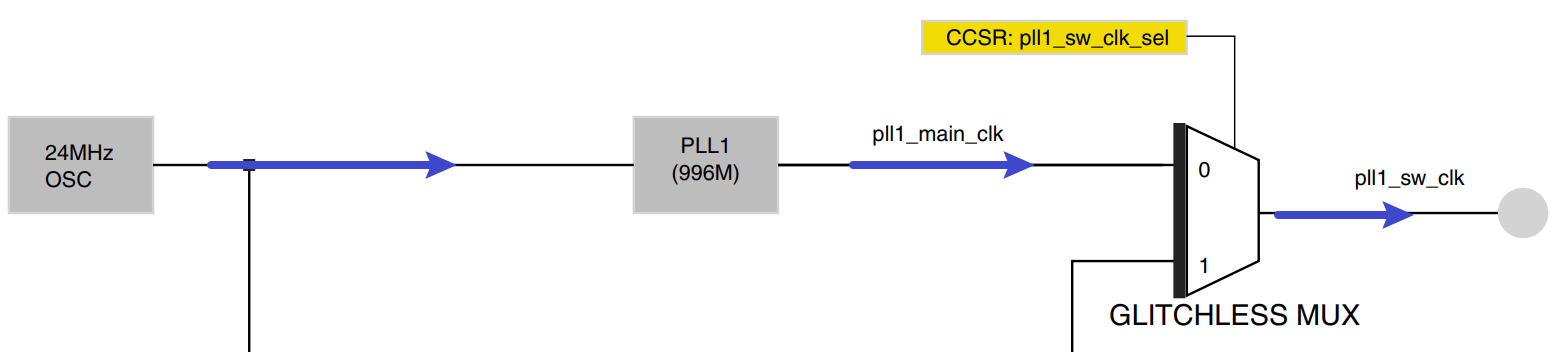

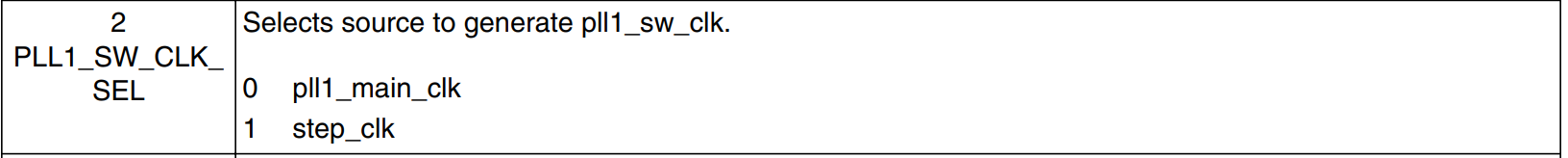

也就是选择输送给 PLL1 的时钟源,所以我们要先看看 PLL1 可以选择哪些时钟源。在第18.5.1.5 小节,这里介绍了时钟树给外设分配时钟之前,24MHz的晶振是如何产生各路时钟的。

pll1_sw_clk 是 PLL1 最终的输出频率(注意不是ARM内核时钟的频率),要切换至备用时钟(step_clk),我们就需要打通下面这条路线,即设置该路线上的相关寄存器。

基本步骤如下:

- 设置 CCSR 寄存器的 step_sel 位,设为 0

- 设置 CCSR 寄存器的 pll1_sw_clk_sel 位,设为 1

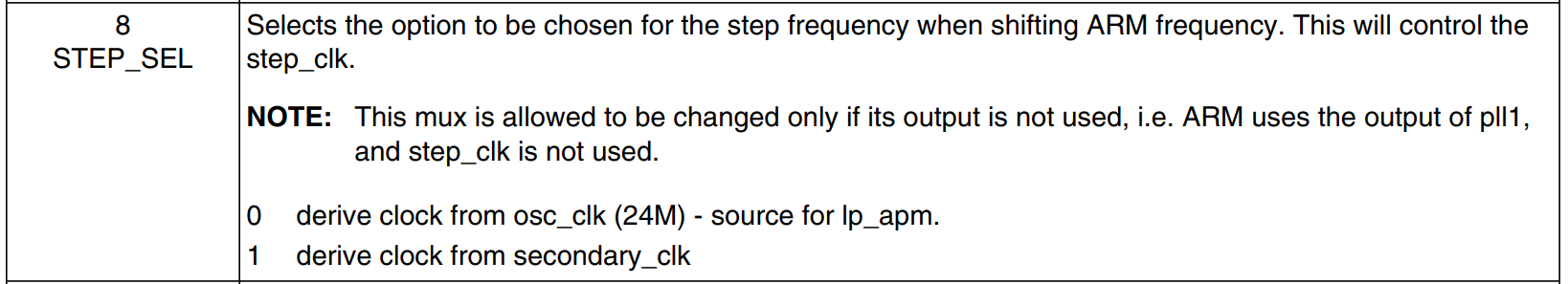

《imx6u参考手册》第 18 章下的 CCM Memory Map,选择 CCM_CCSR,找到 step_sel 位 和 pll1_sw_clk_sel 位

![]()

寄存器: CCM_CCSR

基地址: 0x20C400C

初始化操作:

CCM_CCSR &= ~(1 << 8) // 将 STEP_SEL位设为 0

CCM_CCSR |= (1 << 2) // 将 PLL1_SW_CLK_SEL 设为 12、设置内核时钟主频(CCM_ANALOG_PLL_ARMn)

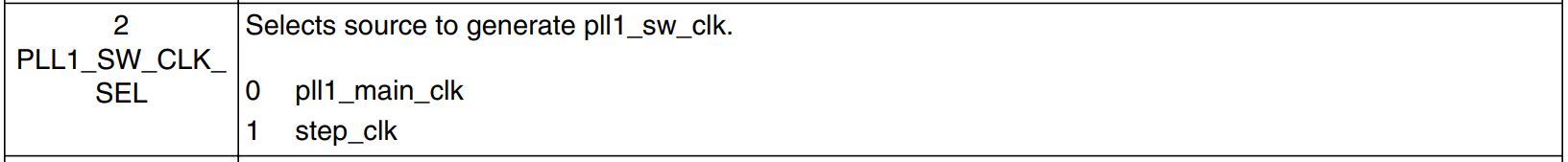

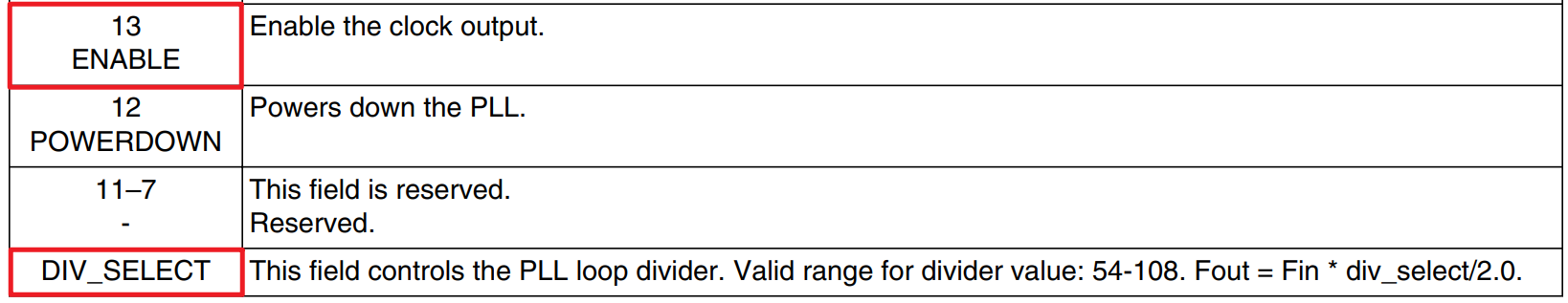

由 第18.5.1.3.1小节 ARM PLL (644页)可知,修改时钟主频对应的是 CCM_ANALOG_PLL_ARM 寄存器的 DIV_SELECT 位。我们无法直接设置 PLL1 输出频率,只能设置 DIV_SEL,PLL1 输出频率和 DIV_SEL之间存在一个转换公式。

其中 Fref 表示晶振频率,即 24 MHz。假设我们要设为 1056 MHz,那么 DIV_SEL 就应该设为 88,十六进制为 0x58。

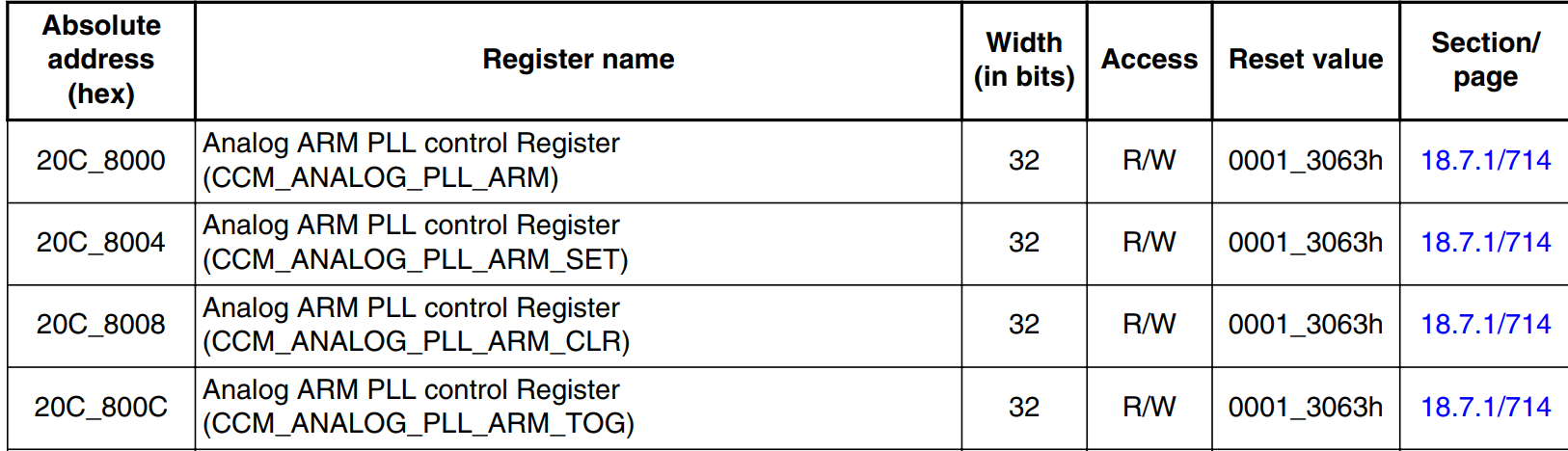

选择第 18 章的 CCM Analog Memory Map 的 CCM_ANALOG_PLL_ARMn,为什么是 PLL_ARMn?因为这里涉及到 4 种寄存器,这四种寄存器都和 PLL_ARM 有关,但是他们有着不同的功能。(只不过他们的字段分布都是一样的)

我们要设置的是 CCM_ANALOG_PLL_ARM 寄存器的 DIV_SELECT 位(6 - 0 bit)和 ENABLE(第 13 bit)。

寄存器: CCM_ANALOG_PLL_ARM

基地址: 0x20C8000

初始化操作:

CCM_ANALOG_PLL_ARM |= (1 << 13); // 设置时钟输出使能

CCM_ANALOG_PLL_ARM &= ~(0x7F) // 清空低7位 (6 - 0 bit)

CCM_ANALOG_PLL_ARM |= 0x58; // 将低7位设为0x58,对应十进制 88 3、切换回内核时钟(CCM_CCSR)

接下来要切换回原本的内核时钟,我们选择如下路线,此时我们只需要设置 CCSR 寄存器的 pll1_sw_clk_sel 位,设为 0,就可以切换回主频了。

寄存器: CCM_CCSR

基地址: 0x20C400C

初始化操作:

CCM_CCSR &= ~(1 << 2) // 将 PLL1_SW_CLK_SEL 设为 04、设置分频器

现在 PLL1 输出的频率就是 1056MHz 了,我们希望最终进入到ARM 内核的频率只有 528 MHz,因此我们还需要回到时钟树这里,设置分频器。控制分频器的是 CACRR 寄存器的 ARM_PODF 位。

我们要设为 2 分频,就需要将低3位设为 001

![]()

寄存器: CCM_CACRR

基地址: 0x20C4010

初始化操作:

CCM_CACRR &= ~(0x07) // 清空低3位(2 - 0 bit)

CCM_CACRR |= 0x01; // 将低7位设为001,对应十六进制 0x01

7117

7117

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?