(原创声明:该文是作者的原创,面向对象是FPGA入门者,后续会有进阶的高级教程。宗旨是让每个想做FPGA的人轻松入门,作者不光让大家知其然,还要让大家知其所以然!每个工程作者都搭建了全自动化的仿真环境,只需要双击top_tb.bat文件就可以完成整个的仿真(前提是安装了modelsim),降低了初学者的门槛。如需整个工程请留言(WX:Blue23Light),不收任何费用,但是仅供参考,不建议大家获得资料后从事一些商业活动!)

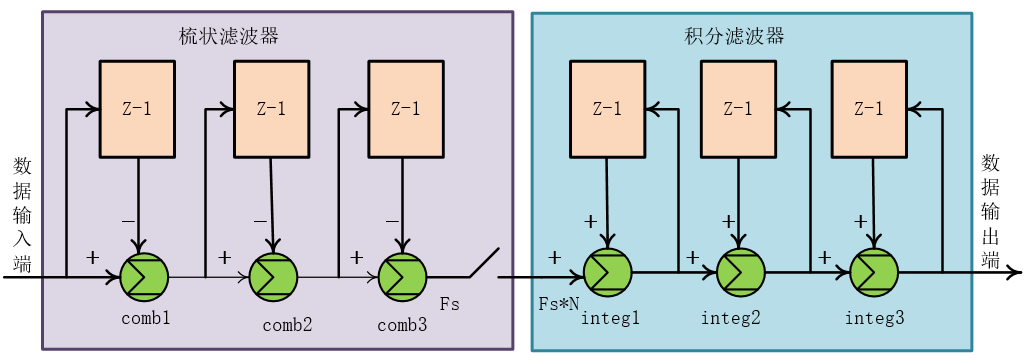

上节课主要讲述了CIC的抽取滤波器的FPGA设计,当时也说了既然CIC可以进行降采样抽取,那也可以升采样进行插值。不过插值滤波器的结构和抽取滤波器的结构稍有不同,CIC抽取滤波器是先积分滤波,再梳状滤波;而插值滤波器是先梳状滤波,再积分滤波,结构图如下所示,如果数据输入频率是的Fs,那经过CIC插值滤波器后输出输出频率是Fs*N,在两个输入数据之间插入了N-1个新的数值。当然处理过程中位数的扩展和上节课是一样的。

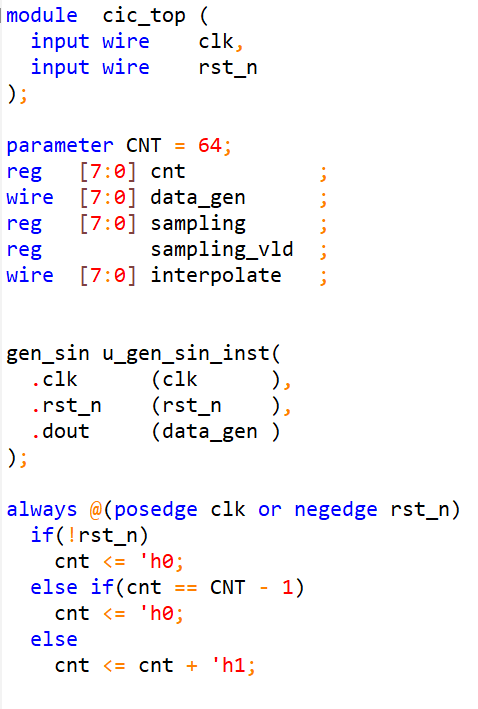

这样不做过多的原理讲解,直接接入FPGA的设计。在cic_top中,定义了参数CNT=64,就是将正弦波的输出每64个点取一个点给到CIC的插值模块。系统时钟是100MHz,所以正弦波的采样频率是100/64=1.5625MHz。

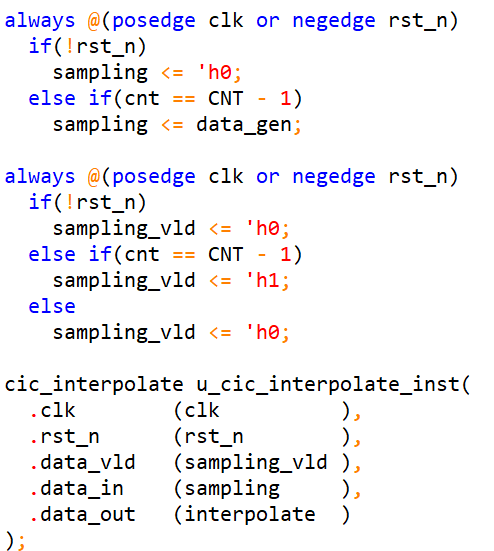

将采样频率是1.5625MHz的采样数据和使能信号给CIC插值模块cic_interpolate。

在CIC插值模块cic_interpolate中,输入数据是8位的,在两个数据均匀插入15个点,就是16倍的插值,还是采样3阶的积分滤波和梳状滤波,按照上节的位数扩展计数公式,扩展后最大位是20位。

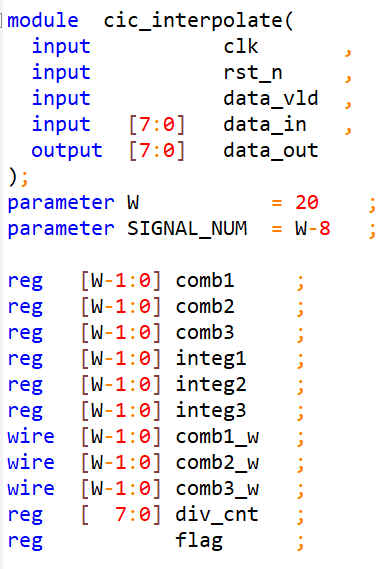

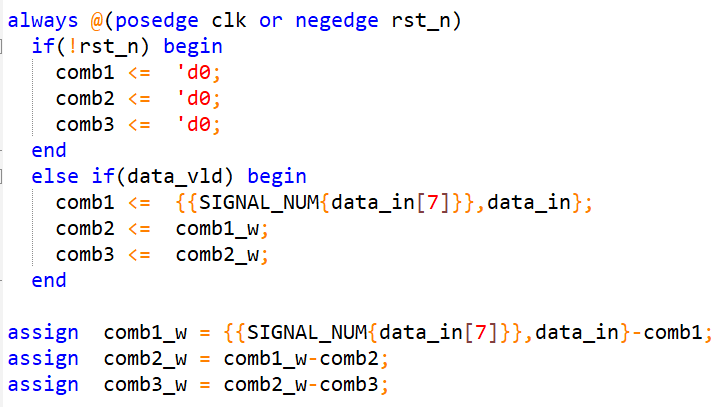

先进行梳状滤波的设计,就是输入的数据先进入3阶的梳状滤波,此时数据的输入频率是100/64=1.5625MHz。

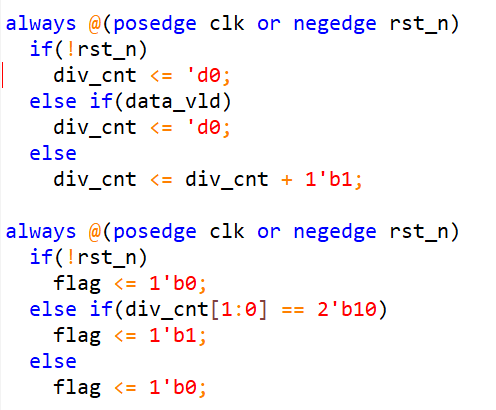

通过计数div_cnt产生插值的标志信号flag,在两个数据的标志信号data_vld之间,均匀的插入了15个flag信号。

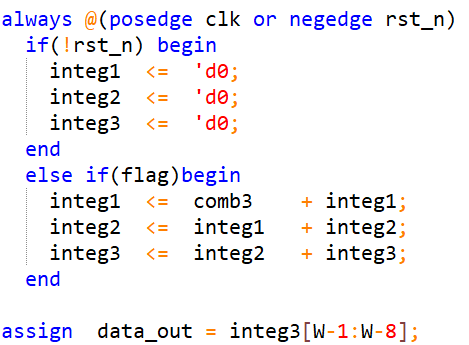

最后实现3阶的积分滤波器,此时处理的频率是1.5625*16=25MHz。将最后1阶积分累加结果的高8位输出,既可以得到16倍插值后的正弦波。

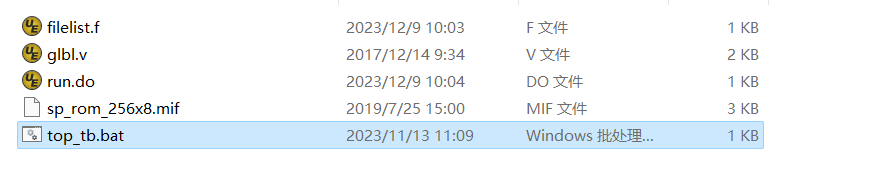

新建仿真文件后,双击sim目录下的top_tb.bat文件,完成系统的自动化仿真。

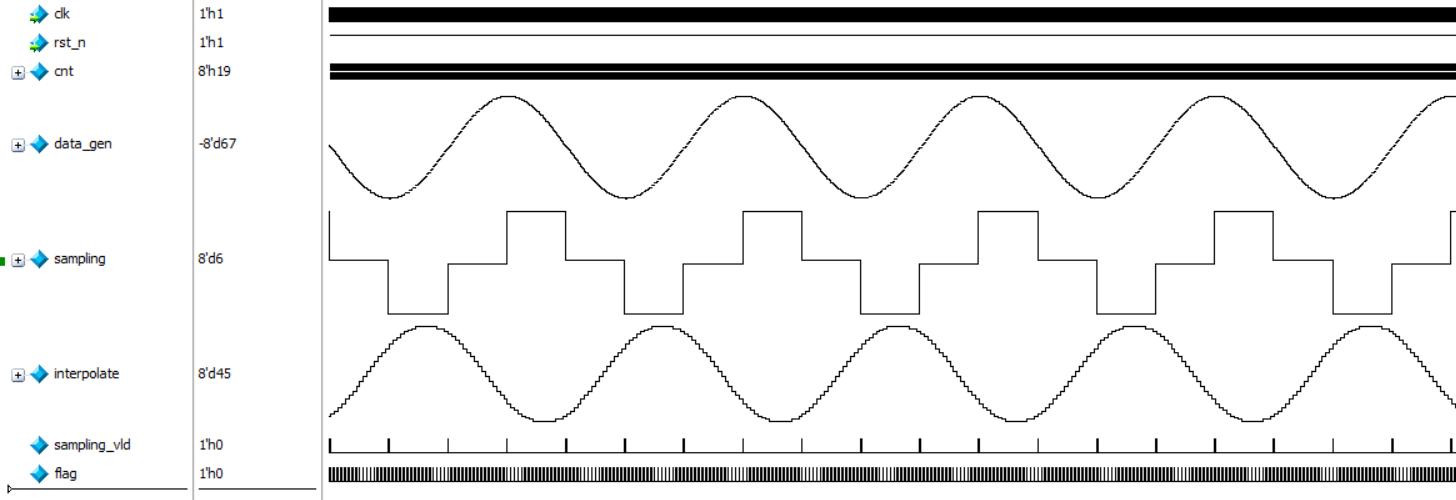

看一下modelsim的仿真波形,正弦波信号data_gen经过64倍的降采样后产生波形信号sampling,失真已经很严重了,经过cic_interpolate的16倍插值,基本恢复了正弦波的所有细节,除了相位有较大的偏移(这个偏移量是固定的),所以功能开发是正确的。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?