一、核心思路

基于 FPGA 的实时图像去雾系统。设计的主要思路为:首先需要对系统的框架进行设计搭建,对去雾的过程有初步的理解;其次进行去雾算法的研究与学习,选择最合适的去雾算法,在研究内容的基础上对选择的算法进行改进;最后对硬件电路进行设计。本文的主要研究内容:

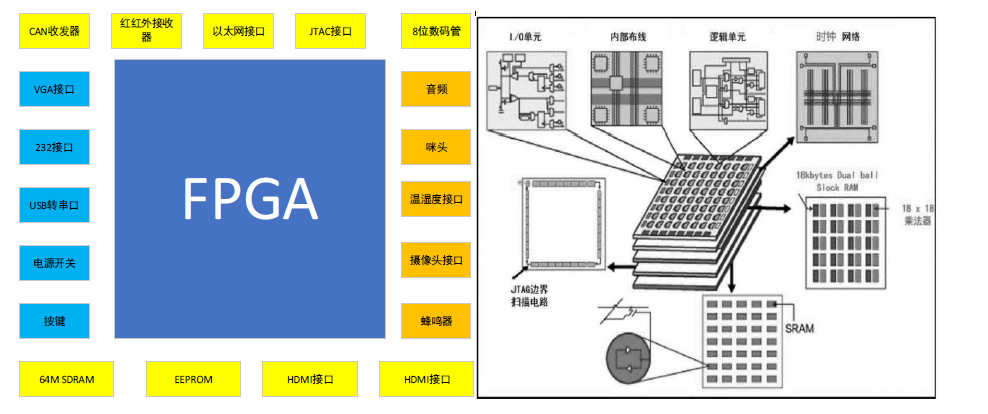

(1) 分析 FPGA 的芯片结构和硬件资源,对图像去雾过程中的硬件总体框架进行设计,在uartus Ⅱ平台上利用 Verilog 语言对图像去雾设计方案进行代码编写。

(2) 对雾天图像的形成原理、雾天图像的大气散射模型、暗通道图像先验算法进行研究和分析。通过比较分析图像去雾过程中各个步骤,选择去雾效果最理想的方式。

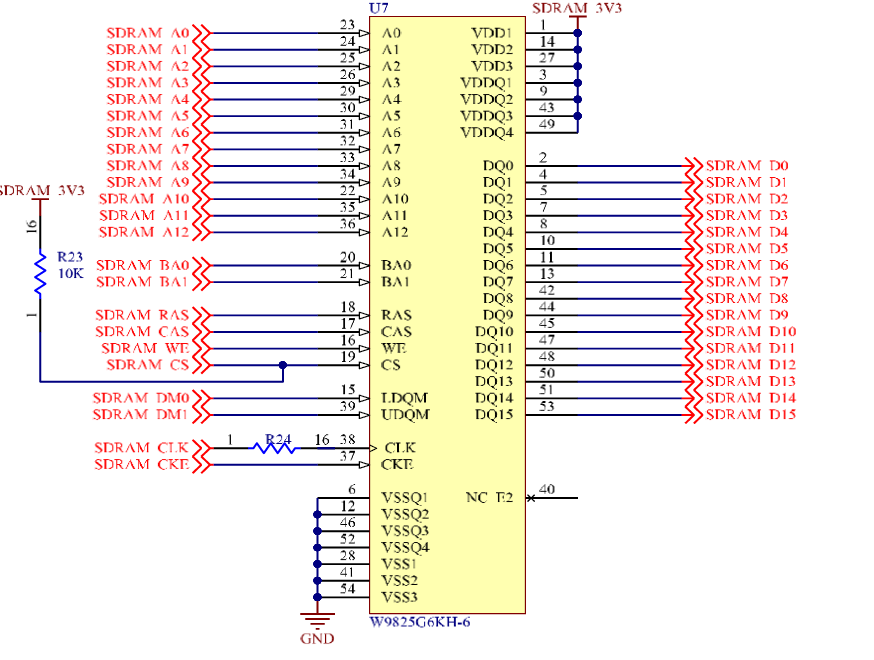

(3) 分析 FIFO 模块和 SDRAM 存储器的原理,通过 FIFO 模块实现数据的跨时钟域处理和数据缓存,在 SDRAM 存储器中进行数据的读写操作。分析 I2C 协议的相关原理,在FPGA 内部设计实现基于 I2C 协议的图像数据采集过程。

(4) 研究并分析最小值滤波、导向滤波的实现方式以及大气光值 A 的计算方法。采用快速最小值滤波求取暗通道图像,减少算法运行时间;通过导向滤波对粗糙透射率进行细化处理,消除图像中的块状效应,使获取的图像更加清晰。

二、主要设计内容

本文设计图像去雾处理采用的 Cyclone Ⅳ FPGA 开发板芯片型号是 EP4CE10F17C8,采用的软件环境是 Quartus Ⅱ 13.0,运用 Testbench 编写代码,对 Verilog 语言设计的电路进行测试,运用 ModelSim 进行仿真验证。ModelSim 支持 XP、Windows 和 Linux 系统等语言编译器,支持 VHDL 和 Verilog 混合仿真,为编译系统提供了良好的环境,其个性化的图像界面能够使用户方便进行调试操作,并能够将调试波形图清晰的显示出来,便于使用者进行观察仿真波形图中的细节信息。就 FPGA 电路结构而言,FPGA 可编程是指:可编程逻辑块、可编程 I/O、可编程布线资源。

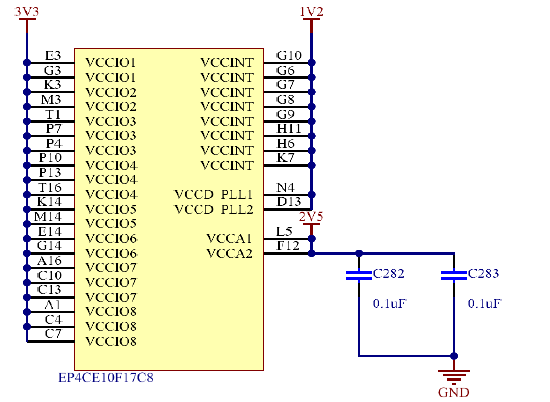

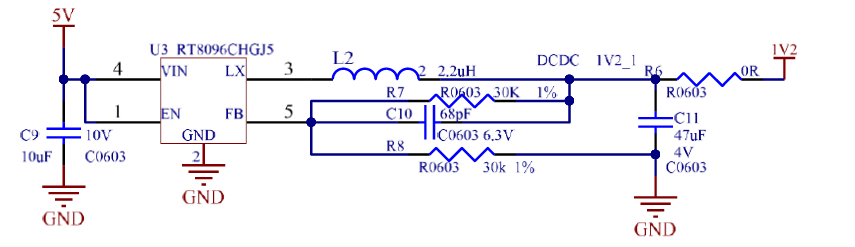

开发板上的IO BANK 采用 3.3V 电源供电,为其提供最大的供电电压,目的是确保FPGA 开发板能正常工作。为了获得所需要的时钟信号,使用 PLL 锁相环将输入的时钟信号进行倍频或分频处理,FPGA 开发板上设置两个 PLL 锁相环,分别为 PLL 模拟供电管脚和PLL 数字供电管脚,PLL 数字供电管脚接 1.2V 内核电源,PLL 模拟供电管脚接 2.5V 的模拟电源。此外,在电源引脚附近增加高频滤波电容器,目的是使提供的电压具有平滑稳定的特点。FPGA 供电电源电路如图

博主简介:本团队擅长数据处理、建模仿真、程序设计、论文写作与指导,项目与课题经验交流。

976

976

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?