1-NXP i.MX RT1052 连载之 MCU 简介【1】_KiFF的博客-CSDN博客

2-NXP i.MX RT1052 连载之 Boot 简介【2】_KiFF的博客-CSDN博客(重要)

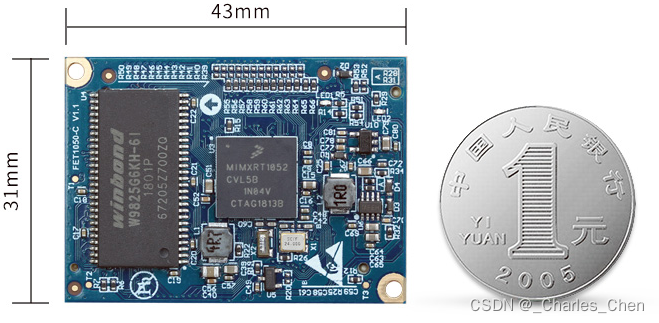

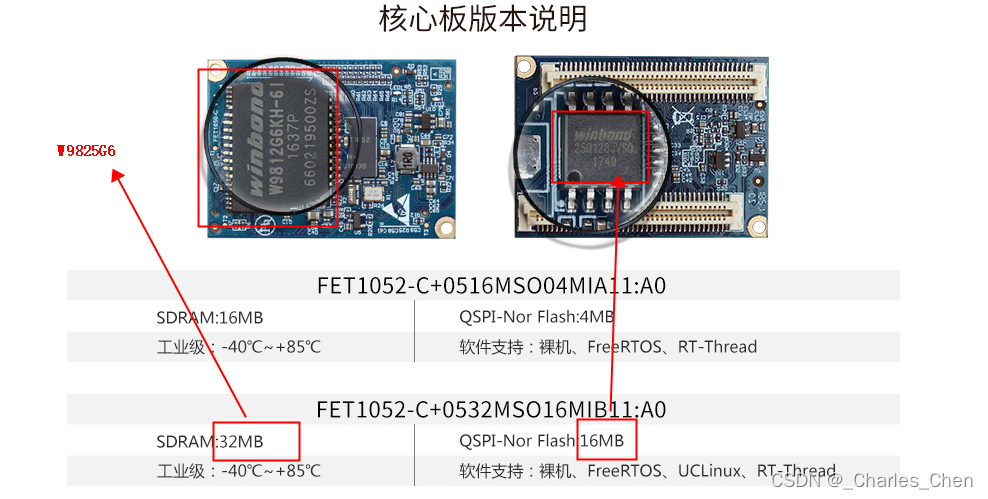

3-i.MXRT单片机-Cortex-M7 i.MX RT1052 跨界核心板 - ARM核心板 - 保定飞凌嵌入式技术有限公司

4-RT-Thread合作伙伴正点原子发布号令者RT1052开发板_wx60dac676d6910的技术博客_51CTO博客

这两个插座型号是什么?

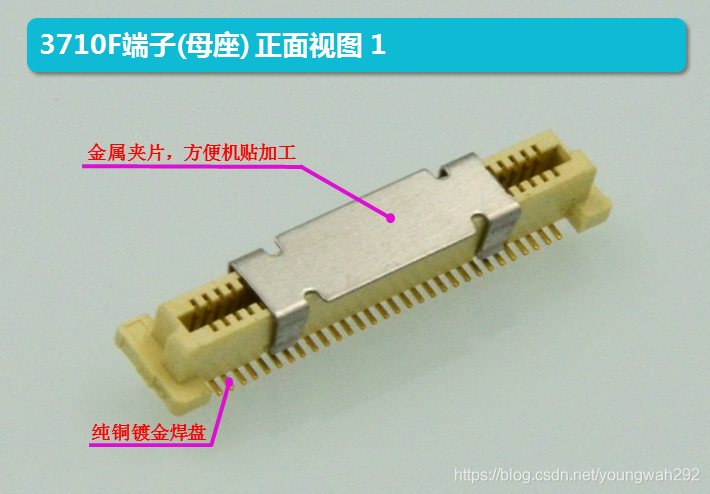

在核心板上安装的这两个插座,是3710F插座(公头)。

那么与之对应的是3710F插座(母座),如下图所示。

正点原子官网有这种购买连接,可以搜索“3710F板对板连接器”查找购买。

RT1052性能很强大,但是其价格贵,70-100左右一片。

需要外部存储才行,同时主频频率那么高,功耗肯定低不了。

rt1052性能还是很强大的,虽然不能和stm32最高新能比,但是和中等芯片还是可以的。

目前还是不能替代的,RT1052是一个高端的处理器,主要的面对市场不能可能代替STM32。

取代不了STM32,RT1052的问题也很多,第一是不带内部flash,运行时需要外接sdram,那这样说,就是1052即使是用最小系统,也必须要把外置spi flash或nand flash,以及sdram画上电路板才能用。

一、代码放在哪里了?

我们辛辛苦苦编写好的代码都会通过下载工具下载到设备的 ROM 、RAM 或者 Flash 当中去,既然代码的安身之处有如此多的地方,那设备上电后,应该去哪里取代码执行呢?是不是设备已经非常 "智能" 了,可以自动的识别代码 "藏" 在哪里了?显然答案是否定的,设备可没有那么智能~,既然设备无法自动识别代码在哪里,那只能由代码的烧录者来告诉它,让它知道代码放在哪里了,应该去哪里取代码执行。那应该怎么告诉它呢? Boot Mode 启动模式就应运而生了,往往通过设置不同的引脚电平来告诉芯片,让它知道去那里取代码执行。

在正式说 RT1052 启动模式之前,还有个重量级的人物要介绍,它就是 Bootrom(或Boot ROM)是嵌入处理器芯片内的一小块掩模 ROM 或写保护闪存。它包含处理器在上电或复位时执行的第一段代码。根据某些特定引脚或内部保险丝的配置,它可以决定从哪里加载要执行的代码的下一部分以及如何/或是否验证其正确性或有效性。有时它可能包含其他功能,可能在引导期间或之后由用户代码使用。

二、启动设备与启动模式

从 NXP 官方提供的参考手册《IMXRT1050RM.pdf》可以了解到芯片引导过程从上电复位 (POR) 开始,硬件复位逻辑强制 ARM 内核从片上 boot ROM 开始执行。boot ROM 代码使用内部寄存器 BOOT_MODE[1:0] 的状态以及各种 eFUSE 和 GPIO 设置的状态来确定设备的引导流程。其中 ROM 的主要功能包括:

对于设备的 ROM,本文主要介绍它支持的外部启动设备,其它方式启动:例如串行下载、DCD、低功耗唤醒等功能放到后面再介绍,从上图中,我们可以了解到 RT1050 系列支持六种启动设备【针对的内部启动方式】,分别是:

> FlexSPI 控制的串行 NOR Flash

> FlexSPI 控制的串行 NAND Flash

> SEMC 控制的并行 NOR Flash

> SEMC 控制的 RAW NAND Flash

> SD/MMC

> LPSPI 控制的 SPI NOR/EEPROM

相信看到这里,对于没有接触过 NXP 芯片的同学来讲可能会产生疑问了,为啥这里既有 FlexSPI 又有 LPSPI,难道它们不是一样的吗?还有 SEMC 又是什么来的呢?所以还是穿插一下讲讲 FlexSPI / LPSPI / SEMC 又是何方神圣:

RT1052 芯片集成了专门用于 SPI 协议通讯的外设 FlexSPI、LPSPI,其中 LPSPI (Low Power Serial Peripheral Interface)主要定位于通用的 SPI 通讯,而 FlexSPI (Quad Serial Peripheral Interface)外设除了支持 SPI 通讯外还提供了很多与存储器相关的特性,所以 FlexSPI 外设通常用于与使用 SPI 协议的存储设备进行通讯。

SEMC(Smart External Memory Controller) 是一种多标准内存控制器,针对高性能和低引脚数进行了优化。 它可以在具有共享地址和数据引脚的同一应用中支持多个外部存储器。 支持的接口包括 SDRAM、SRAM、NOR Flash和 NAND Flash 以及 8080 显示接口。

回归主题,现在我们已经知道了 RT1050 系列的六种启动设备了,那我们应该使用哪种设备呢作为启动设备呢?芯片又是怎么知道我们想要它把代码拷贝到哪个设备中去执行呢?

如何决定使用哪种设备作为启动(ROM)设备呢?具体的可以参考博文最后的几个链接,根据实际项目需要,从芯片读/写速度、擦除速度、寿命、价格等因素进行芯片选型即可。

选择好一款启动设备后该怎么告诉主芯片我们用的是哪种启动设备呢?优先想到的就是使用一个拨码开关,用哪款启动芯片就拨到相应的地址,这样是不是就可以解决怎么告诉主芯片了?事实确实也是这样:

从上图中,我们可以了解到 RT1050 系列的芯片是怎样选择启动设备的,是通过 BOOT_CFG1[7:4] 这四位寄存器的值来判断当前的启动设备是哪款。所以实际操作就可以利用四个 IO 管脚来连接一个拨码开关,进而实现多款设备都能切换启动的方式。

介绍完了启动设备,接下来看看启动模式:从 RT1050 的参考手册中,我们可以知道该系列的芯片支持四种启动模式(由 BOOT_MODE0 和 BOOT_MODE1 的启动电平决定):

BOOT_MODE[1:0] Boot Type

00 通过熔丝引导启动

01 通过串行下载(eg:USB)

10 内部 boot 启动

11 保留

知道了启动设备 / 启动模式相应的寄存器后,那它们对应的 GPIO 管脚又是哪些呢?下面给出一个表格,通过表格,可以知道哪些 GPIO 管脚用来负责启动模式的选择、哪些用来负责启动设备的选择:

三、设备的初始化流程

现在我们已经知道了 RT1050 这颗 SOC 里有一段固化的代码(boot ROM),也知道了启动模式、启动设备是如何选择的了,哪它们又是怎么联系在一起,它们中间又有什么故事发生呢?

一般在内部启动模式下,芯片会执行内部的 boot ROM 代码,这段 boot ROM 代码会进行硬件初始化(一部分外设),然后从 boot 设备(就是存放代码的设备:比如 SD/EMMC、 NAND Flash、Nor Flash、SPI Flash 等)中将代码拷贝出来复制到指定的 RAM 中运行。从 RT1050 参数手册中,我们可以知道 Boot ROM 设备初始化过程中执行了以下的操作:

> ROM 存储器映射;

> RAM 存储器映射;

> 必要的片上 ROM 使用或更改 POR 寄存器的默认值;

> 时钟初始化;

> 启用 L1 级的指令/数据缓存;

> 异常处理和中断处理;

> 数据位保持;

ROM / RAM 存储器映射:

从上面两张图我们可以知道,在 Boot ROM 阶段,它映射了 96KByte 的 ROM 空间,用于存放异常向量表、ROM 版本号、ROM Apis 等一些列的操作,也映射了 32 KByte 的 RAM 空间,用于存放 BSS段、RW段、堆栈等一些列的操作;而它们之间的细节会在后面专门讲 ROM / RAM 的章节中详细展开来描述。

硬件单元控制:

在系统启动初期,在操作硬件前需要对一系列的硬件控制单元进行初始化/配置才能正常使用,其中包括 CCM、SPI、IOMUX 等系列的硬件单元(具体可以参看上表)。

初期的时钟配置:

通过上面的表格,可以看出在设置不同的 BOOT_FREQ 和 LPB_BOOT 值后所得到的 Core 时钟频率也有所不同,更为详细的时钟相关的内容会在后续专门介绍时钟单元的博文中详细介绍。

启用 L1 级的指令/数据缓存:

在系统启动初期,boot ROM 会去启动 L1 级缓存(指令缓存 / 数据缓存)以提高系统的启动速度,L1 级的指令 cache 在开始下载镜像的时候变开始启动,L1 级的数据 cache 在校验镜像的时候启动。

这时候可能就会有同学问了,那我不想它启用 cache 能不能操作呢?答案是肯定的,用户可以通过编程熔丝寄存器的某些位去禁用 cache。

指令缓存功能由 BT_ICACHE_DISABLE 熔丝控制,数据缓存功能由 BT_DCACHE_DISABLE 熔丝控制。 默认情况下,两个保险丝都没有熔断,这意味着 boot ROM 会使用 ARM 内核的 L1-ICache 和 L1-DCache,提高了 HAB 签名验证软件的性能。

异常处理和中断处理:

异常向量(中断向量/向量表)表位于 ROM 的开头。在启动阶段,CPU 从异常向量表加载 SP 和 PC 并启动,启动后程序映像可以根据需要重新定位向量表。

在引导过程中不需要特殊的中断处理服务, 所以中断服务在 boot ROM 执行期间被禁用,但可以在 boot ROM 以后的引导中启用。

数据位保持:

热复位后某些模式下 boot ROM 要求寄存器保持它们的值不发生改变,所以就有了 SRC 通用寄存器去实现该目的,详细的可以参看下面的表格:

名称 位域 描述

PERSIST_SECONDARY_BOOT SRC_GPR10[30] 该位标识必须使用哪个映像作为主要和次要映像。 仅用于 eMMC/SD 启动。

PERSISTENT_ENTRY0 SRC_GPR1[31:0] 保持 CPU0 从低功耗模式唤醒的入口函数。

PERSISTENT_ARG0 SRC_GPR2[31:0] 保持 CPU0 从低功耗模式唤醒的入口函数的参数。

PERSIST_REDUNDANT_BOOT SRC_GPR10[27:26] 该域标识着镜像必须使用 0/1/2/3。用于 SPI Nand 和 SLC raw Nand 设备。

四、启动流程

关于 RT1050 系列的启动流程,通过上图可以看出还是比较清晰、比较简单的,博主画了几根不同颜色的线用于代表不同的启动流程(画的有点丑,不要太介意 ^_^),如果看不清图标可以点击图片放大来看,其中:

> 绿色的线代表使用 FlexSPI / SEMC 启动的方式;

> 橘色的线代表使用串行 NOR/EEPROM 启动的方式;

> 紫色的线表达使用 SD 卡启动的方式;

> 蓝色的线代表使用串行下载(USB 或 LPUART)启动的方式;

不同的启动设备(只针对内部设备)所需要配置的信息不同(例如电平的大小不同、读写时序不同等),启动的流程也稍有不同,这里就挑一个 QSPI Nor Flash 作为例子讲解,其它类型的设备就不再赘述。

从上面的表格可以了解到,对于不同的 spi nor flash 可以配置 Flash Type、Hold time before read 等一系列的参数。

FlexSPI Nor Fash 的启动流程:首先系统会根据 BOOT_CFG1 [7:4] 位的配置,如果都是 0 的话,则 boot ROM 会去初始化 FlexSPI 接口;紧接着 boot ROM 会去读取 Nor Flash 中的前 512 字节的数据(它包含 FlexSPI NOR 配置参数),boot ROM 会使用 BOOT_CFG2[2:0] 指定的读取命令读取这些配置参数,此时串行时钟运行在 30 MHz;最后 boot ROM 会使用从 Nor Flash 读取的配置块中提供的参数配置 FlexSPI1 接口并启动启动程序。

下图是 FlexSPI Nor Fash 的启动流程图:

五、镜像格式

上图是一张简要的 Image 镜像格式,由于篇幅的原因,不想一篇博文太长,详细的 Image 在后续的博文中再展开来讲。

六、其它

参考链接:

1. NOR FLASH和NAND FLASH基本结构和特点_vincentxj2008的专栏-CSDN博客

2. MMC/SD/SDIO介绍

3. EEPROM、FLASH、NOR FLASH、NAND FLASH 区别、关系总结_浅浅0099的博客-CSDN博客

————————————————

版权声明:本文为CSDN博主「KiFF」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/sinat_34266686/article/details/121559644

1072

1072

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?