〇、关于本文

本文我的Verilog课程作业,由于我尚处在初学阶段,并且这门课和我实际工作的关系并不大,因此代码仅供参考。

我使用的编译环境为iverilog,在Windows下运行。

一、4-1选择器

文件a.v代码

module mux4_1(out, in0, in1, in2, in3, sel);

output out;

input in0, in1, in2, in3;

input [1:0] sel;

reg out;

always @(in0 or in1 or in2 or in3 or sel)

case(sel)

2'b00: out = in0;

2'b01: out = in1;

2'b10: out = in2;

2'b11: out = in3;

default: out = 2'bx;

endcase

endmodule文件b.v代码

module test();

wire out;

reg in0, in1, in2, in3;

reg [1:0] sel;

mux4_1 dut(.out(out), .in0(in0), .in1(in1), .in2(in2), .in3(in3), .sel(sel));

initial begin

in0 = 2'b00;

in1 = 2'b01;

in2 = 2'b10;

in3 = 2'b11;

#1 sel = 2'b00;

#1 sel = 2'b01;

#1 sel = 2'b10;

#1 sel = 2'b11;

end

initial begin

$dumpfile("./test.vcd");

$dumpvars(-1, test);

$dumpon();

#6

$dumpoff();

$finish;

end

always #1

$display("%t: cout=%b %h %h %h %h %b", $time, out, in0, in1, in2, in3, sel);

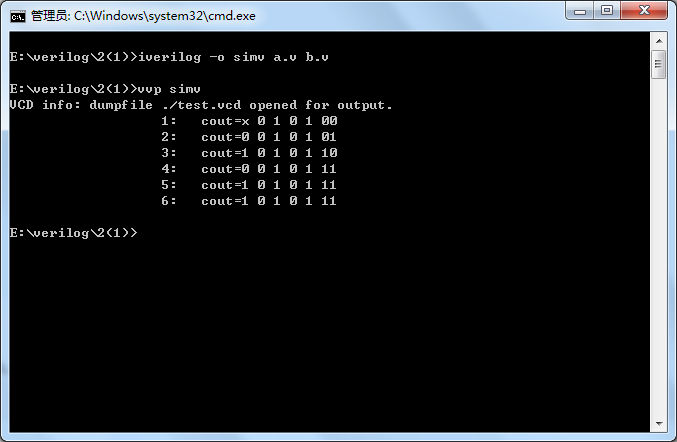

endmodule运行结果

gtkwave.exe中显示的波形

二、8位计数器

文件a.v代码

module count_en(clock, reset, out);

input clock, reset;

output [7:0] out;

reg [7:0] out;

always @(posedge clock or negedge reset)

if(!reset)

out = 8'b0;

else

out = out + 1;

endmodule文件b.v代码

module test();

reg clock, reset;

wire[7:0] out;

count_en dut(.clock(clock), .reset(reset), .out(out));

initial begin

#1 reset = 0;

#1 reset = 1;

end

always begin

#1 clock = 0;

#1 clock = 1;

end

initial begin

$dumpfile("./test.vcd");

$dumpvars(-1, test);

$dumpon();

#40

$dumpoff();

$finish;

end

always #2

$display("%t: out=%b", $time, out);

endmodule运行结果

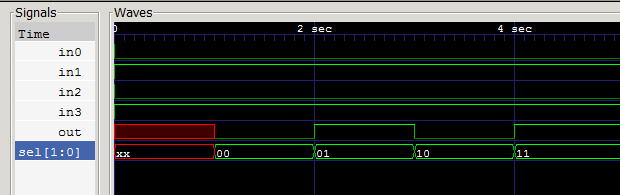

gtkwave.exe中显示的波形

三、设计一个通过函数完成的模块,实现16位无符号数乘法

文件a.v代码

module mult16(product,a,b);

output [15:0] product;

input [15:0] a;

input [15:0] b;

reg [15:0] product;

always @(a,b)

product = multiply(a, b);

function [15:0] multiply;

input [15:0] a;

input [15:0] b;

multiply = a * b;

endfunction

endmodule文件b.v代码

module test();

reg [15:0] a, b;

wire [15:0] product;

mult16 dut(.a(a), .b(b), .product(product));

initial begin

#1 a = 16'b00000000; b = 16'b00000000;

#1 a = 16'b00000010; b = 16'b00000011;

#1 a = 16'b00010010; b = 16'b01000011;

#1 a = 16'b01101010; b = 16'b00101011;

#1 a = 16'b01111111; b = 16'b00001111;

end

initial begin

$dumpfile("./test.vcd");

$dumpvars(-1, test);

$dumpon();

#5

$dumpoff();

$finish;

end

always #1

$display("%t: a=%h b=%h product=%b", $time, a, b, product);

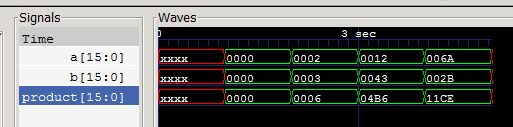

endmodule运行结果

gtkwave.exe中显示的波形

1473

1473

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?