在FPGA中,信号同步处理是解决亚稳态问题的常见处理方式,常见的同步设计方案有以下三种

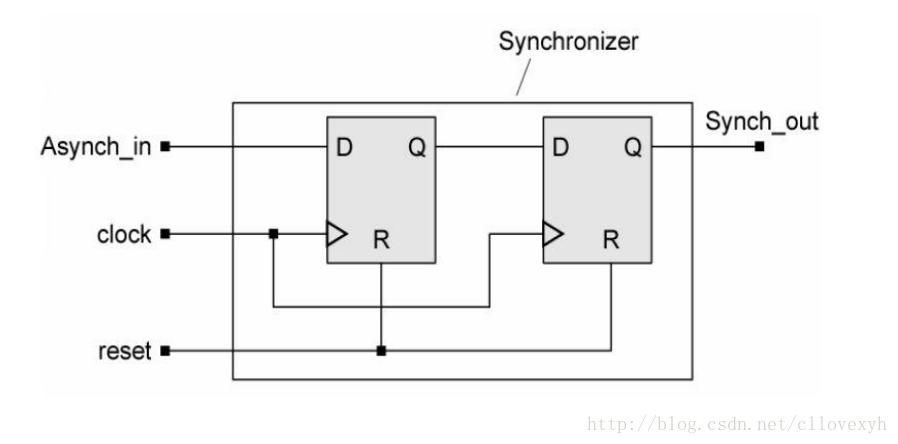

一、同步方案一

1、verilog代码

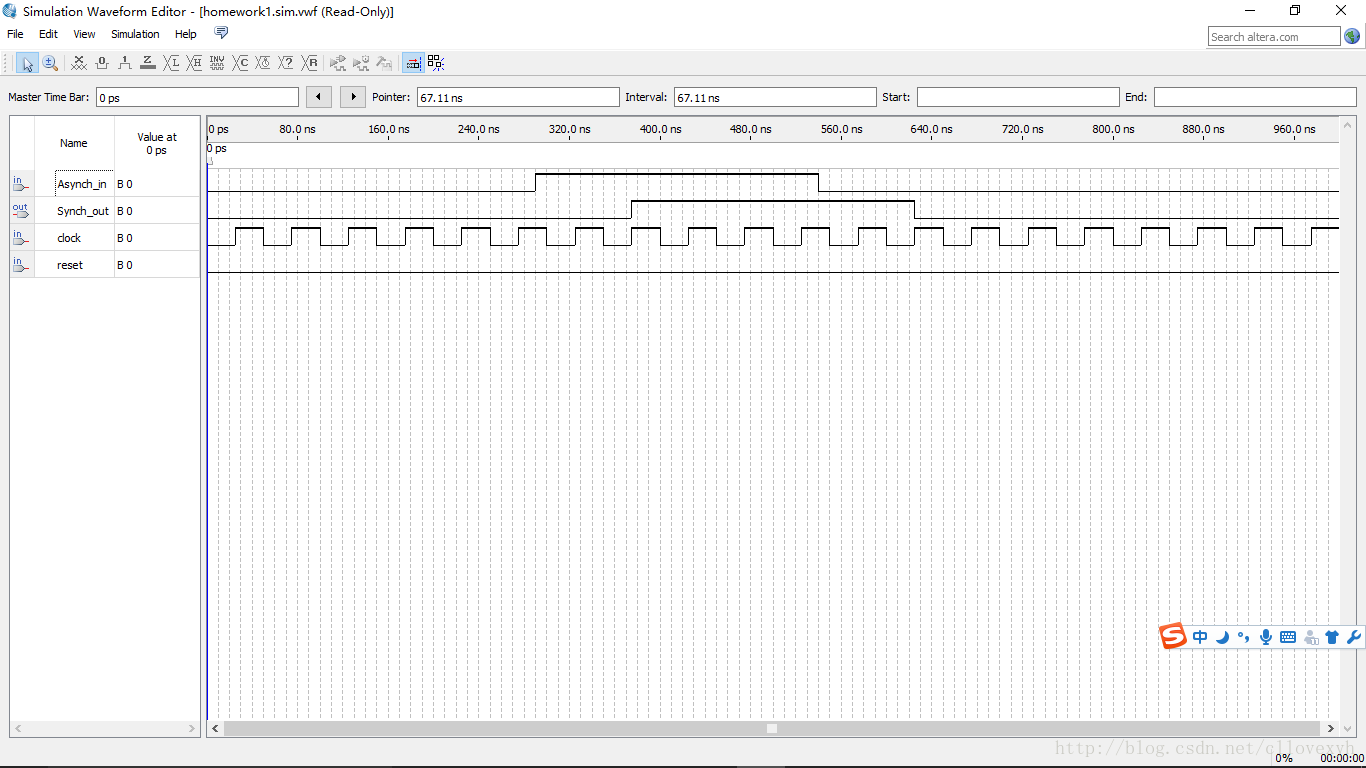

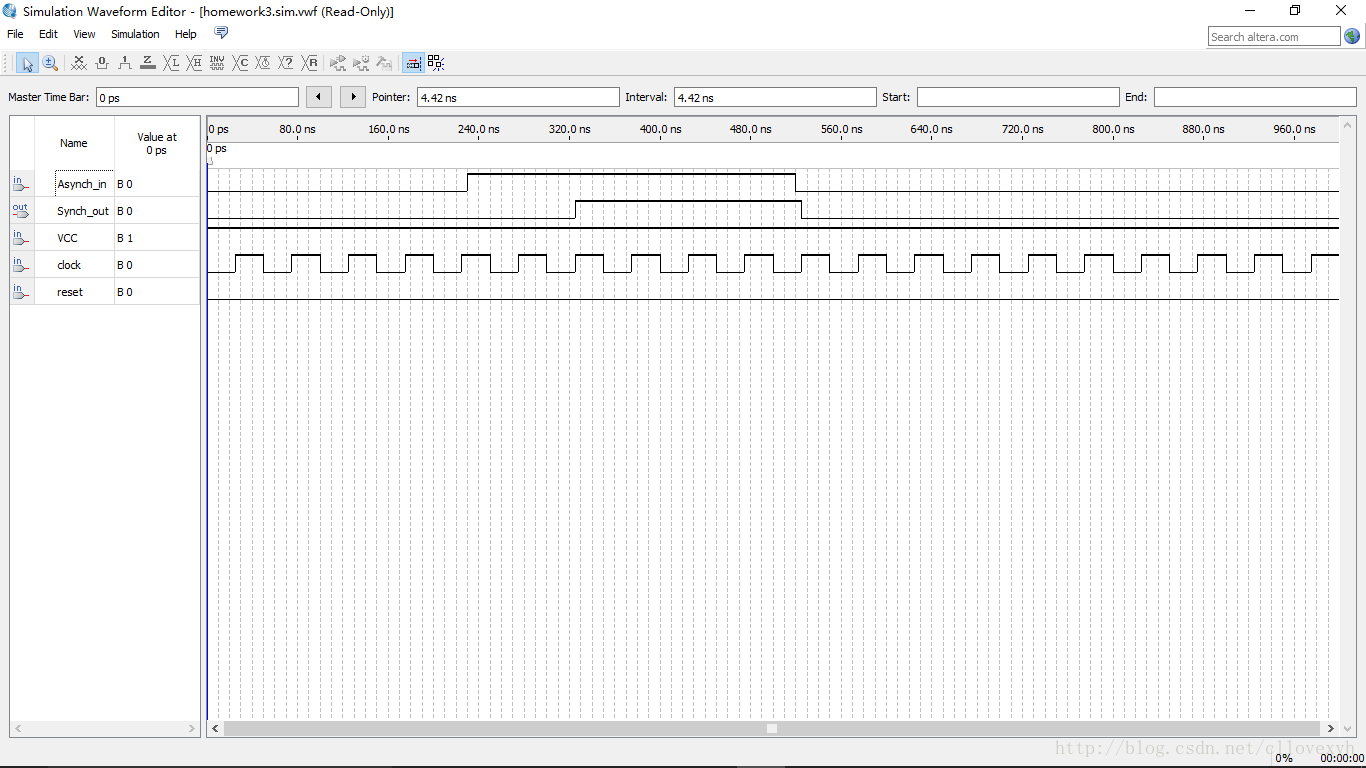

2、仿真

2.1 信号周期大于时钟周期

2.2 信号周期小于时钟周期

分析:

该同步电路设计简单,使用时钟上升沿进行触发同步,在同步大于时钟周期的大信号时没有任何问题,但是在同步比一个时钟周期小的小信号时(如上图所示),就很有可能采集不到该信号导致无法同步。

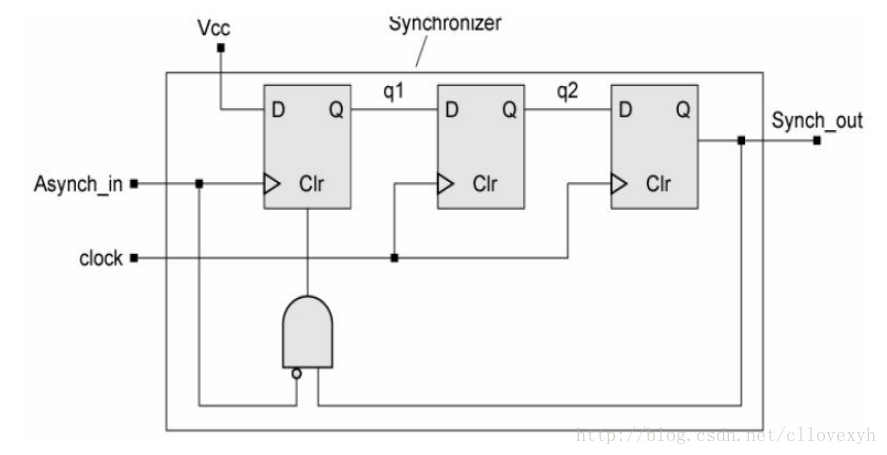

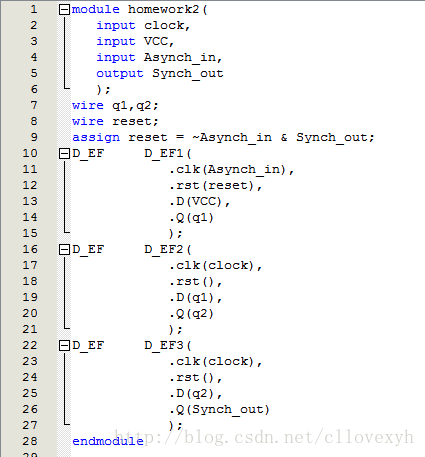

二、同步方案二

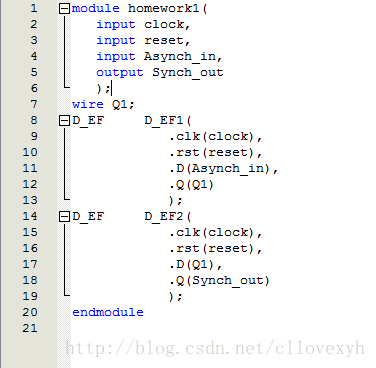

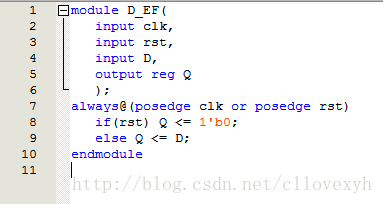

1、verilog代码

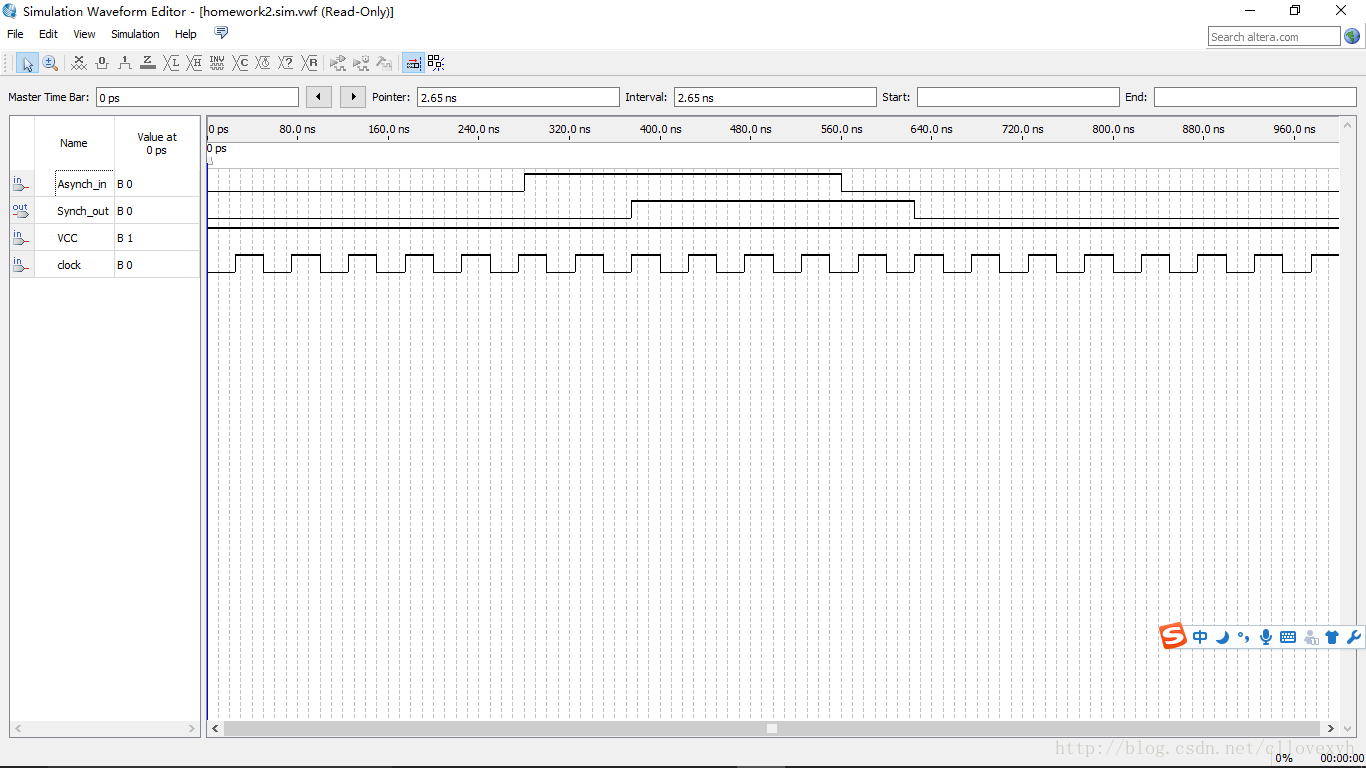

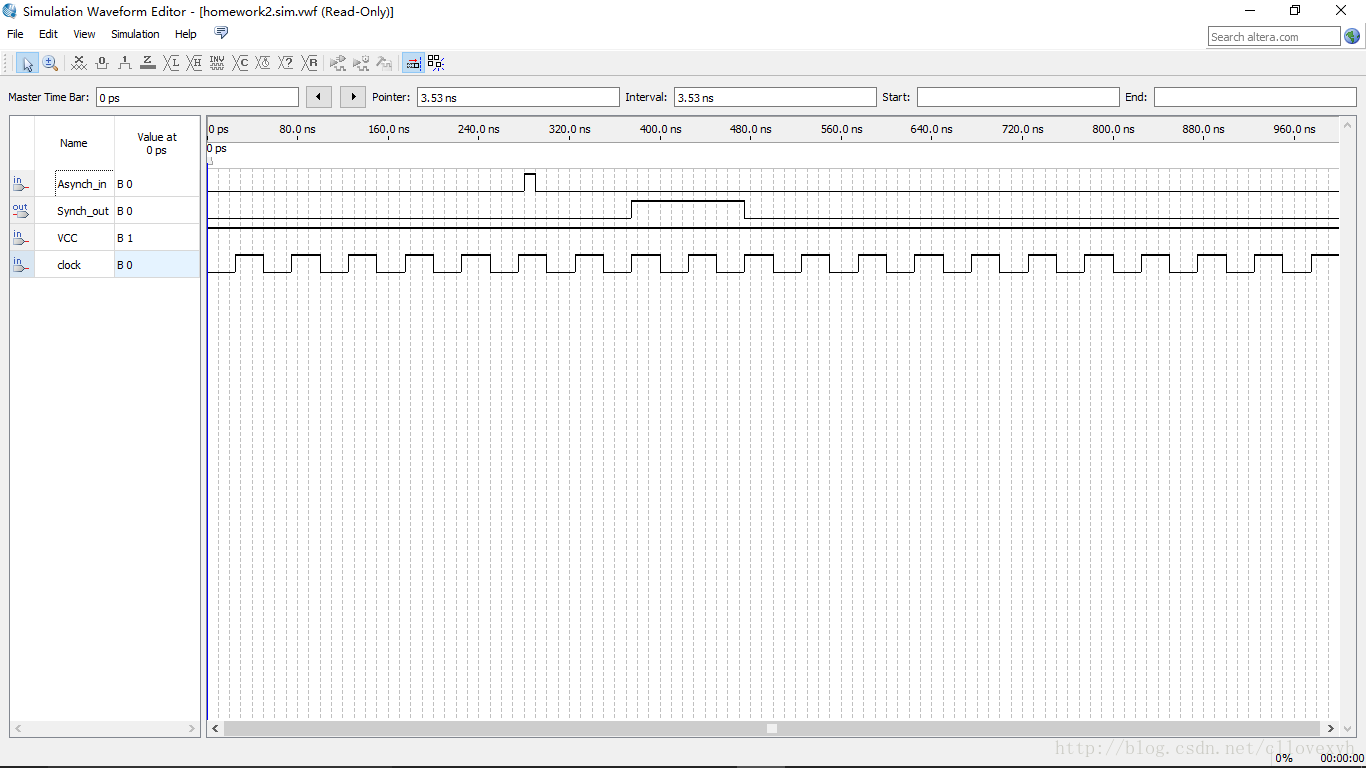

2、仿真

2.1 信号周期大于时钟周期

2.2 信号周期小于时钟周期

分析:

该电路设计稍显复杂,使用3个触发器会使得信号滞后到第3个时钟上升沿到来时实现同步,有效避免亚稳态;同时该设计使用信号作为触发,高电平作为输出,有效避免了小信号采集不到的问题。

但同步后的信号宽度较长,如上图在同步一个周期小于时钟周期的小信号时,同步后的脉冲宽度变为2个时钟周期。

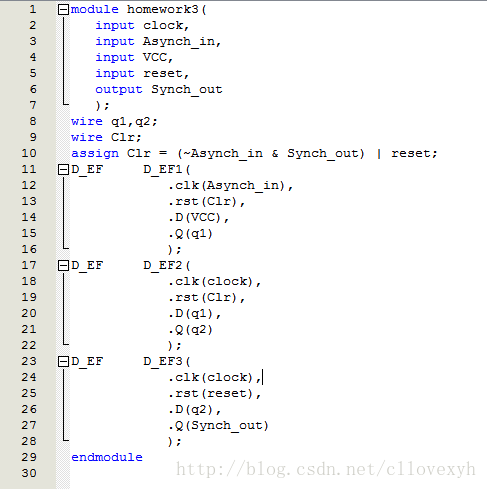

三、同步方案三

1、verilog代码

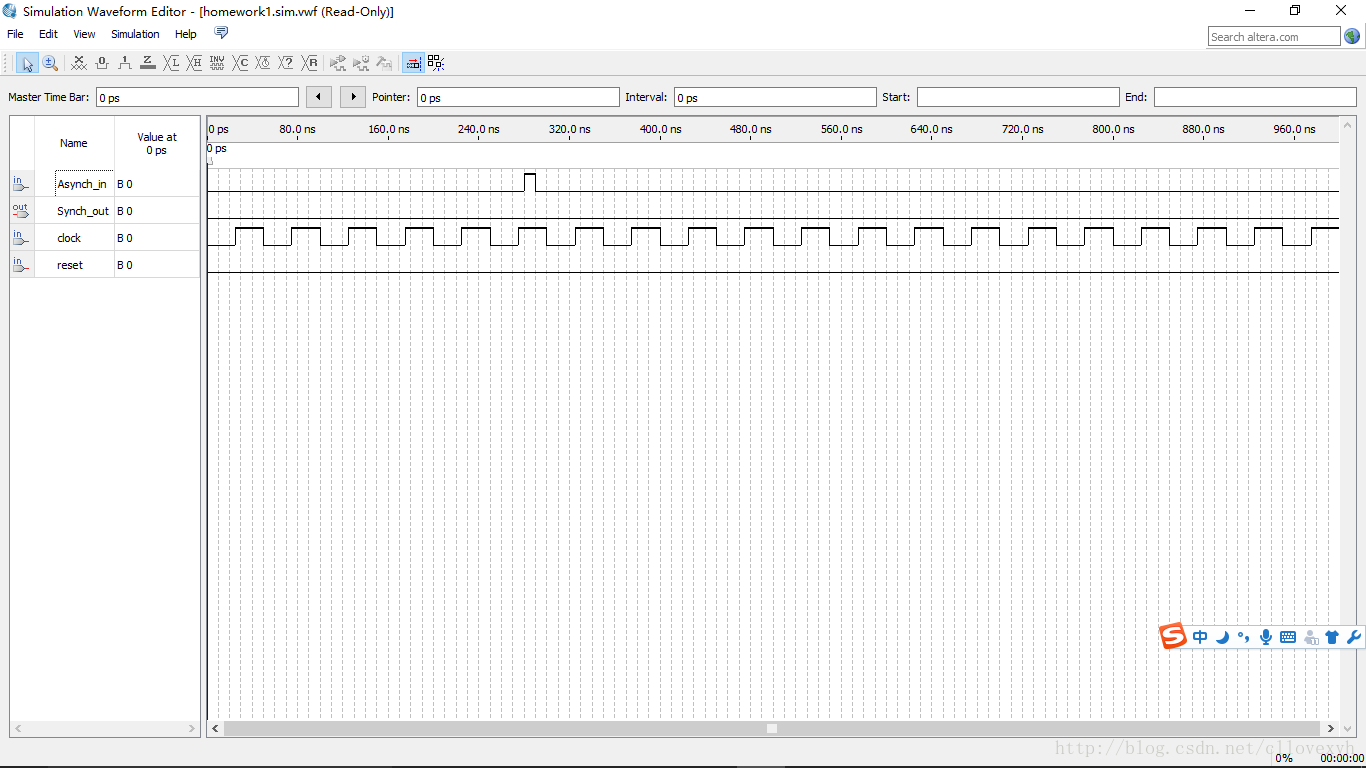

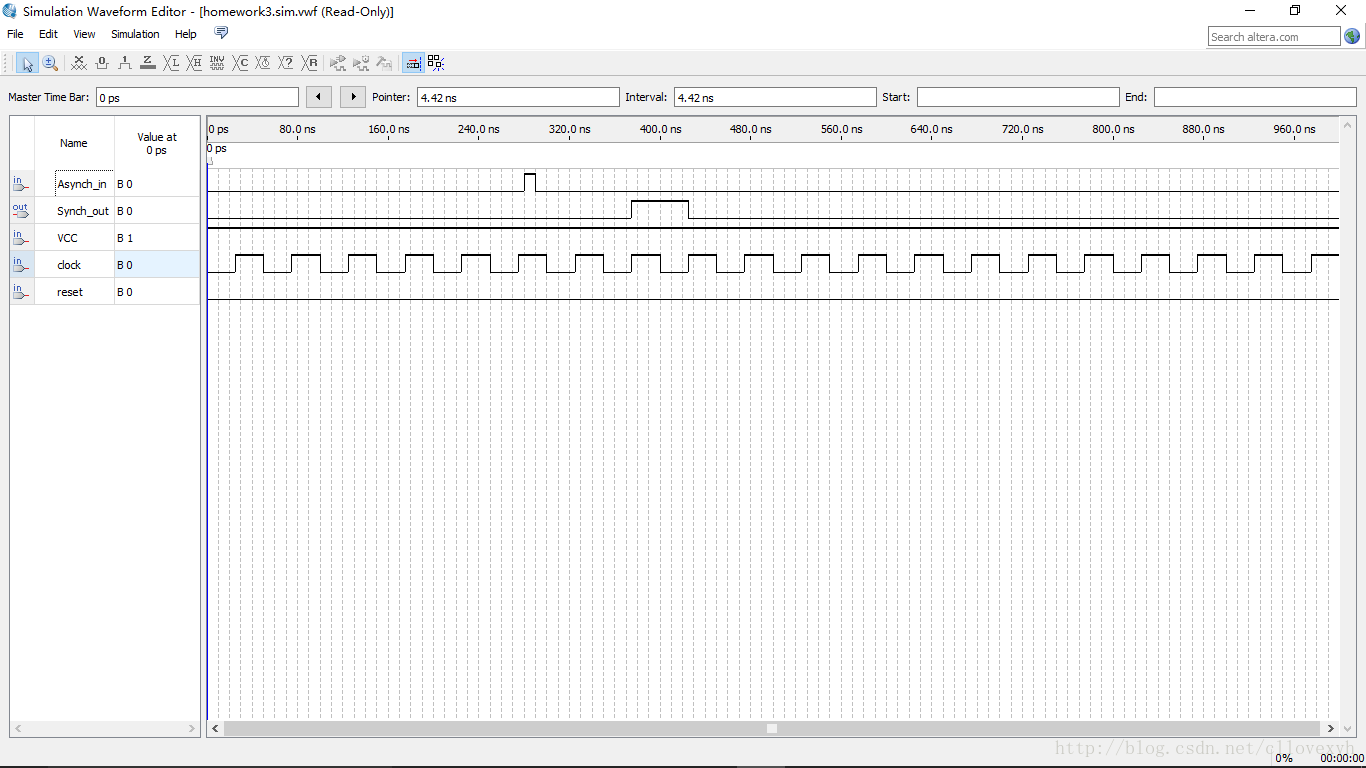

2、仿真

2.1 信号周期大于时钟周期

2.2 信号周期小于时钟周期

分析:

该同步电路设计复杂,联合使用测试信号和系统时钟作为触发源,并且使用三级D触发器,能够保证同步所有信号且有效避免出现亚稳态;同时使用相同输入输出联合信号,控制的D触发器的清零端口,减小了同步后脉冲宽度。

在下学习FPGA不久,若有错误处,还请大神们斧正。

1284

1284

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?