、基本术语

二、基本概念

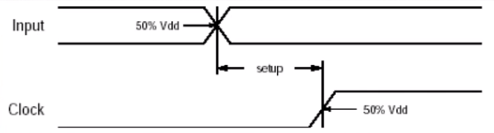

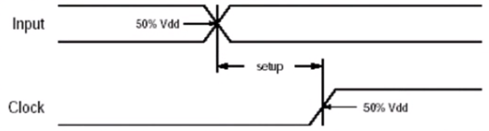

1.建立时间(setup time)

触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被打入触发器

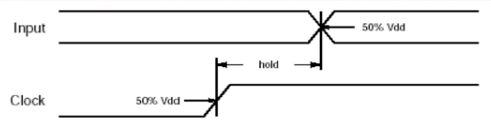

2.保持时间(hold time)

触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据将不能被打入触发器。

3.时间裕量(time slack)

传输中的信号的真实时间于需求时间之间的差值。通常用来表示设计是否满足时序要求。

Setup slack = Data Required Time(setup) - Data Arrival Time

Hold slack = Data Arrival Time - Data Required Time (hold)

4.时钟抖动(clock jitter)

指时钟边沿变化不确定的时间。

5.时钟偏斜(clock skew)

时钟和其它信号的传输一样会有延时的。下图中,时钟信号从时钟源传输到源寄存器的延时定义为Tc2s ,传输到目标寄存器的延时定义为 Tc2d。

时钟偏斜是指时钟源到达源寄存器和目的寄存器的时间偏移。其计算公式为:Tskew = Tc2d – Tc2s。

6.时序分析起点(launch edge)

第一级寄存器数据变化的时钟边沿,也是静态时序分析的起点。

7.时序分析终点(latch edge)

数据锁存的时钟边沿,也是静态时序分析的终点。

8.数据输出延时(Clock-to-Output Delay)

这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。

9.数据到达时间(data arrival time)

输入数据在有效时钟沿后到达所需要的时间。主要分为三部分:时钟到达源寄存器时间(Tc2s),寄存器输出的延时(Tco)和源寄存器到目的寄存器数据传输的延时(Tr2r),如下图:

因此,Data Arrival Time = launch edge + Tc2s + Tco + Tr2r

10.数据需求时间(Data Required Time)

在时钟锁存的建立时间和保持时间之间数据必须稳定,从源时钟起点达到这种稳定状态需要的时间即为数据需求时间。如下图:

因此,(建立)Data Required Time = latch edge + Tc2d – Tsu;

(保持)Data Required Time = latch edge + Tc2d + Th;

而习惯用Clock Arrival Time (时钟到达时间)= latch edge + Tc2d

三、基本流程

STA主要分为以下三步:

1、将整个电路设计分割成不同的时序路径

2、计算每一条时序路径的逻辑延时

3、检查时序路径是否满足其时序约束

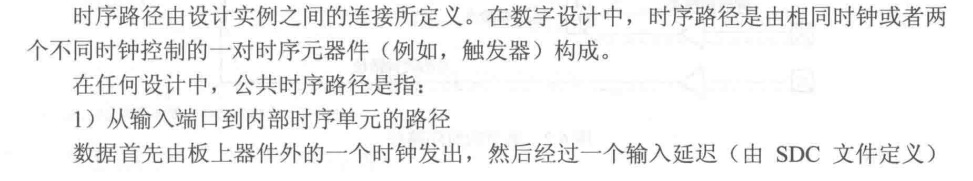

四、时序路径

时序路径可分为以下四种:

1、英文版本

2、中文版本

参考:添加链接描述

7153

7153

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?