提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

前言

静态时序分析是检查IC系统时序是否满足要求的主要手段。以往时序的验证依赖于仿真,采用仿真的方法,覆盖率跟所施加的激励有关,有些时序违例会被忽略。此外,仿真方法效率非常的低,会大大延长产品的开发周期。静态时序分析工具很好地解决了这两个问题。它不需要激励向量,可以报出芯片中所有的时序违例,并且速度很快。

提示:以下是本篇文章正文内容,下面案例可供参考

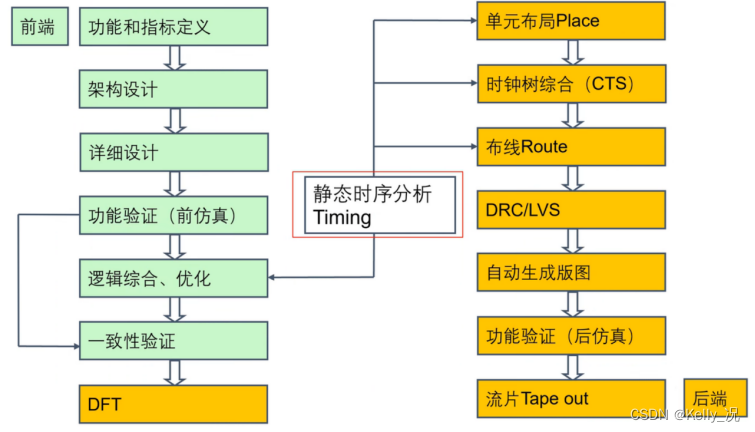

一、数字IC设计流程(前端+后端)

(1)系统设计规划(需求分析)

(2)RTL设计输入

(3)RTL验证(功能仿真)

(4)顶层模块集成、验证(SV/VCS/UVM)

(5)逻辑综合

(6)形式验证(包括门级验证)即综合后仿真

(7)静态时序分析 以上是数字IC前端

(8)DFT可测性设计

(9)版图物理规划

(10)布局与优化

(11)时钟树综合

(12)详细布线

(13)提取寄生参数

(14)静态时序分析、后仿真

(15)版图后验证

芯片生产、测试

二、静态时序分析在芯片设计中的地位

三、静态时序分析的作用

通过静态时序:

检查设计中的关键路径分布;

检查电路中的路径延时是否会导致setup违例;

检查电路中是否由于时钟偏移过大导致hold违例;

检查时钟树的偏移和延时等情况。

此外静态时序分析工具还可以与信号完整性工具结合在一起分析串扰问题。常用的静态时序工具是PrimeTime。

四、静态时序分析过程

静态时序分析原理:静态时序分析工具读入门级网表、时序约束等信息,然后进行静态时序分析。分析过程可以分为3步:

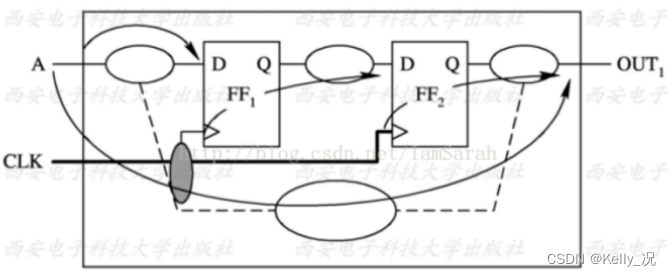

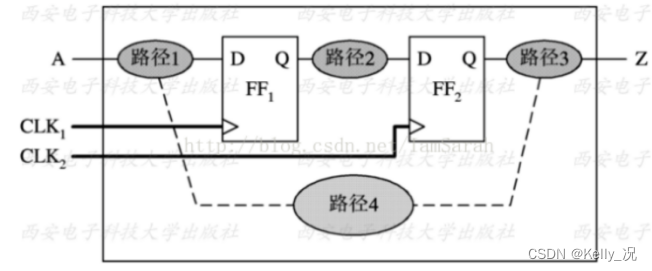

1)将电路分解为时序路径,即将电路转换为时序路径的集合。

时序路径是一个点到点的数据通路,数据沿着时序路径进行传递。它的起点是输入端口或者寄存器的时钟,终点是输出端口或者一个寄存器的输入引脚,每个路径最多只能穿过一个寄存器。这样时序路径就可以划分为:输入端口→寄存器、寄存器→寄存器、寄存器→输出端口、输入端口→输出端口。

2)计算每个路径上面的延时。

在一个路径上,可能包含这几类延时:连线延时、组合逻辑的单位延时、寄存器从clk端到Q端的延时。一个路径上的延时是该路径上所有连线的延时与单位延时的综合。

连线的延时:单元的输出端口和扇出网络负载之间的信息;

单元的延时:单元的输出端口到单元的输入端口间的延时信息。

延时一般定义为从输入跳变的50%时刻到输出跳变的50%之间的时间。

3)检查路径时序约束是否满足。

路径约束主要指的是建立时间约束和保持时间约束。在寄存器的综合库描述中对寄存器的D端定义了建立时间和保持时间的约束。

建立时间约束是指在采样时钟到达之前,数据应该稳定的时间;

保持时间约束是指在时钟到达之后,数据应该保持的时间,这样才能保证寄存器正确地锁存数据。

对于纯组合逻辑,时序分析主要检查最大延时约束和最小延时路径。

亚稳态是由于寄存器的输入信号没有满足建立时间和保持时间,导致寄存器的输出处于一种不确定的状态。

只要系统中有异步元件,亚稳态就无法避免,亚稳态主要发生在异步信号检测、跨时钟域信号传输、复位电路等常用设计中。

**

产生亚稳态后,寄存器Q端输出在稳定下来之前可能是毛刺、振荡、固定的某一电压值。在信号传输中产生亚稳态就会导致与其相连其他数字部件将其作出不同的判断,有的判断到“1”有的判断到“0”,有的也进入了亚稳态,数字部件就会逻辑混乱。在复位电路中产生亚稳态可能会导致复位失败。

**

5711

5711

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?